# Si53xx Any-Rate Precision Clocks

March 2007

### Introducing Si53xx Any-Rate Precision Clocks

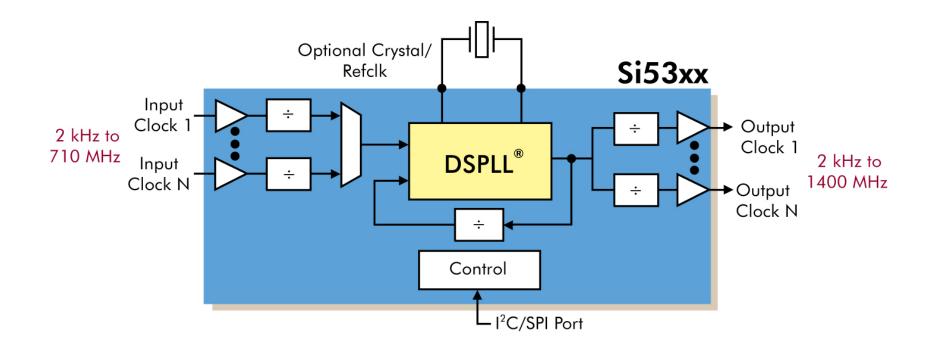

- New family of 9 highly integrated, ultra low jitter clock multiplier ICs

- DSPLL based architecture enables any-rate frequency synthesis

- Improves performance and simplifies design

### **Precision Timing Market**

| Market Segment        | Application                   | Example Frequencies<br>(MHz) |  |  |  |

|-----------------------|-------------------------------|------------------------------|--|--|--|

| Telecom               | SONET/SDH                     | 155.52, 622.08               |  |  |  |

| Datacom               | Ethernet                      | 156.25, 644.53               |  |  |  |

| Storage Area Networks | Fibre Channel                 | 106.25, 212.50               |  |  |  |

| Wireless Basestations | CDMA, GSM, WIMAX              | 78.64, 491.52                |  |  |  |

| Data Acquisition      | Data converter sampling clock | 80, 124.41                   |  |  |  |

| Video                 | HDTV broadcast video          | 74.17, 74.25                 |  |  |  |

| Test & Measurement    | Bench equipment               | 125, 533                     |  |  |  |

| Military              | Communications<br>Displays    | 27, 129.29                   |  |  |  |

Diverse market requiring a broad range of frequencies and excellent jitter performance

### **Key Feature—Any-Rate Frequency Synthesis**

- DSPLL enables any-rate operation over a wide frequency range

- No external component changes required

- Frequency flexibility reduces BOM and enables design reuse

### Silicon Labs Si53xx versus Discrete Solutions

#### Si53xx Any-Rate Precision Clocks Traditional VCXO/VCSO-Based PLLs

| Fully integrated IC replaces VCXO/VCSO PLLs                 | PLL implemented with discrete VCXO or VCSOs                               |

|-------------------------------------------------------------|---------------------------------------------------------------------------|

| Same device can be re-used for all frequencies of operation | New PLL design and components required for<br>each frequency of operation |

| Reconfigurable for multi-rate applications                  | Multi-rate applications require multiple VCXOs                            |

| PLL designed and integrated in IC                           | Requires analog PLL design expertise                                      |

| Short, consistent lead times: 4-6 weeks                     | Long, unpredictable lead times: 8-14 weeks                                |

## The DSPLL Advantage

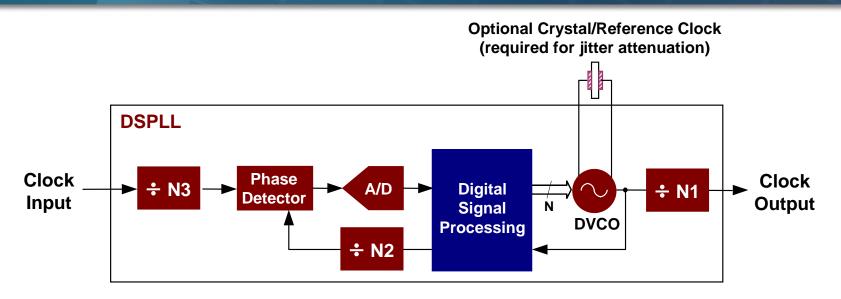

- Patented DSPLL architecture provides frequency agility

- Eliminates need for discrete VCXO/VCSOs

- Ultra-low jitter generation (0.3 ps rms: 12 kHz to 20 MHz)

- Integrated loop filter minimizes PLL sensitivity to board-level noise

- High integration simplifies PLL design and layout

- User-selectable loop bandwidth enables jitter performance optimization

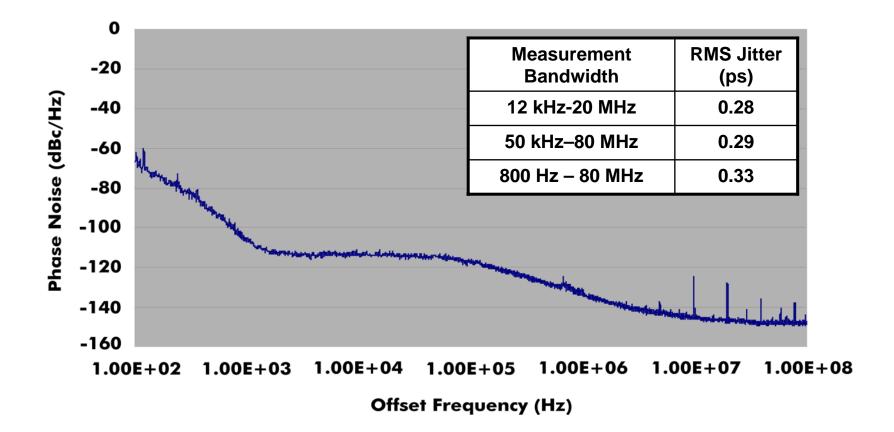

### Si53xx—Ultra Low Jitter/Phase Noise

Si53xx performance comparable to best-in-class VCXO/VCSO PLLs

Configuration: CLKIN = 155.52 MHz, CLKOUT = 622.08 MHz, 800 Hz Loop Bandwidth

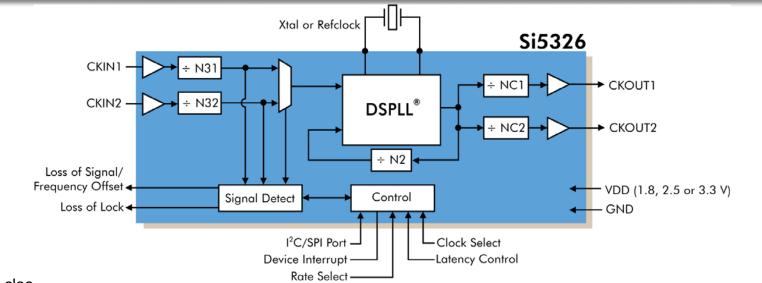

### Si532x Any-Rate Precision Clocks

Two clock inputs/two clock outputs

- Input frequency range: 2 kHz to 710 MHz

- Output frequency range: 2 kHz to 945 MHz, select frequencies to 1.4 GHz

- Output clocks related by ratio of output divider settings (CKOUT2 = (NC1/NC2) \* CKOUT1)

- Ultra low jitter: 0.3 ps<sub>rms</sub>(12 kHz to 20 MHz)

- Automatic (revertive, non-revertive) or manual clock selection with hitless switching

- Programmable output clock signal format: LVPECL, LVDS, CML or CMOS

- Programmable loop bandwidth for jitter attenuation:

60 Hz to 8.4 kHz

- Supply: 1.8 V, 2.5 V, or 3.3 V

- 8 6x6 mm 36-QFN, Pb-free

|               | Fur                   | Control                 |               |     |  |

|---------------|-----------------------|-------------------------|---------------|-----|--|

| Part #        | Jitter<br>Attenuation | Clock<br>Multiplication | μΡ<br>I²C/SPI | Pin |  |

| <u>Si5326</u> | $\checkmark$          | $\checkmark$            | ✓             |     |  |

| Si5323        | $\checkmark$          | $\checkmark$            |               | ✓   |  |

| Si5316        | $\checkmark$          |                         |               | ✓   |  |

| Si5325        |                       | $\checkmark$            | ✓             |     |  |

| Si5322        |                       | $\checkmark$            |               | ✓   |  |

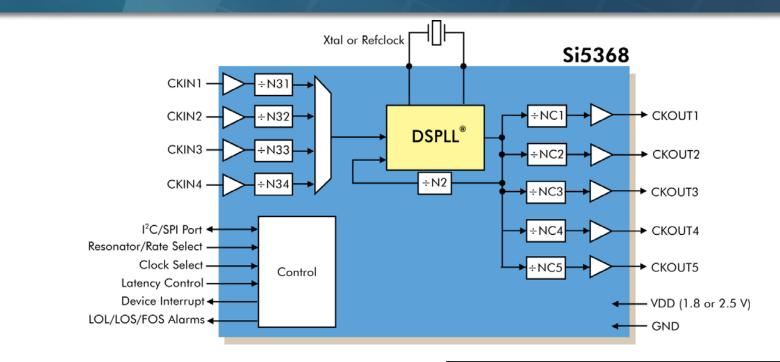

### Si536x Any-Rate Precision Clocks

- Same base features as Si532x PLUS:

- Four clock inputs

- Five clock outputs

- Supply: 1.8 or 2.5 V

- 14x14 mm 100-TQFP, Pb-free

|               | Fun                   | Control                 |               |          |  |

|---------------|-----------------------|-------------------------|---------------|----------|--|

| Part #        | Jitter<br>Attenuation | Clock<br>Multiplication | μΡ<br>I²C/SPI | Pin      |  |

| <u>Si5368</u> | ✓                     | ✓                       | <b>~</b>      |          |  |

| Si5366        | ✓                     | ~                       |               | <b>~</b> |  |

| Si5367        |                       | $\checkmark$            | <b>~</b>      |          |  |

| Si5365        |                       | $\checkmark$            |               | <b>√</b> |  |

### **Key Feature—Frequency Flexibility**

#### Si5325/26/65/68 μP-controlled precision clocks provide any-rate frequency synthesis

- Easily supports custom frequencies

- Reconfigurable to support multi-rate applications

- Three speed grades available

| Speed<br>Grade | Max Output<br>Frequency |

|----------------|-------------------------|

| А              | 1417 MHz                |

| В              | 808 MHz                 |

| С              | 346 MHz                 |

#### Si5322/23/66/68 pin-controlled precision clocks provide ease of use

- 275 popular SONET, Ethernet, Fibre Channel and HDTV frequency translations available via lookup tables

- Includes support for SONET-to-datacomm frequency translations

- Provides upgrade path for existing Si5320/21/64 customers

| -  | FRQ56<br>[3:0] | -   | 100      | 190  | (MH   | r)           |         |       |           | 1              |                   |               | fin BW Max BW<br>(kHZ) (kHz)<br>L+L) |    |         |                 |

|----|----------------|-----|----------|------|-------|--------------|---------|-------|-----------|----------------|-------------------|---------------|--------------------------------------|----|---------|-----------------|

| 0  | LLLL           | 140 | FRQS     | ٤.   | 2.0   | 2.4          | 5.      | M     | uit Pacto | er Nominal     |                   | 15366 Only    | N3 Min B                             |    |         |                 |

| 7  | LUN            |     | ps       | ٥.   | 28    | 28           | MH      |       |           | four' 17       |                   |               | (KHZ                                 |    | (KH2)   |                 |

| 2  | LLLP           |     |          |      | -     |              |         | -     |           |                |                   |               | ps (FRQTBL+L)                        |    |         |                 |

| 3  | LLM            | 0   |          |      | 10 FR | 058L<br>3:0] | 5-63221 | 1228  | (MHz)     | Mult Pactor    | Norminal<br>four* |               | 6 Only<br>FS_OUT (MHz)               | NJ | Min Bit | Max B1<br>(NH2) |

| 4  | LLMB           |     | LLU      |      | 1     |              | 22      | 12126 |           |                | (MHz)             | ICK. CONF # D | ICK_COMP = 1)                        |    |         | 1               |

| ŧ, | LLM            | 2   | ш        |      | 0 1   | uu           | -       |       | 0.008     | 1              | 0.008             | 0.008         | 0.008                                | 1  | 180     | TBO             |

| 6  | LLH            | 3   | LUN      |      | 1.    | LLM          | -       |       |           | 2430           | 19.44             | 19.44         | 0.008                                | 1  | 180     | TEO             |

| 7  | LUHA           | 4   | LLM      |      | 2 1   | LLH          | -       |       |           | 4860           | 38.88             | 38.88         | 0.008                                | 1  | 780     | TEO             |

| 8  | LLHP           | •   | LUM      |      | 3 6   | LML          | -       |       |           | 9720           | 77.76             | 77.76         | 0.008                                | 1  | 780     | 780             |

| ,  | LMU            | 4   | LUH      |      | 4 L   | LMM          | -       |       |           | 19440          | 155.52            | 155.52        | 0.008                                | 1  | TBO     | TBO             |

|    | LMLA           | 7   | LUH      |      | 6 L   | LMH          | -       |       |           | 38880          | 311.04            | 311.04        | 0.008                                | 1  | 180     | TED             |

| 11 | MU             | ۰   | шн       |      | 6 1   | LHL          | -       |       |           | 77760          | 622.08            | 622.08        | 0.008                                | 1  | TBO     | TBO             |

| 2  | LMM            | ۰   | LML      |      | 7 6   | LHM          | •       |       | 19.44     | 1              | 19.44             | 19.44         | 0.008                                | 10 | 180     | TEO             |

| 13 | LMM            | 10  | LML      | t.   |       | LHH          |         |       |           | 2              | 38.88             | 38.88         | 0.008                                | 10 | 780     | TBO             |

| 14 | LABO           | 11  | LML      |      | 9 1   | MLL          |         |       |           | 4              | 77.76             | 77.76         | 0.008                                | 10 | 180     | TEO             |

| 15 | LMH            | 12  | LNB      |      | 0 6   | M.M          |         | ÷     |           |                | 155.52            | 165.52        | 0.008                                | 10 | 180     | TEO             |

| 14 | LMH            | 13  | LMN      |      | 1 1   | MLH          | -       | ÷     |           | 8 x (255/238)  | 166.63            | 165.53        | 166.63                               | 14 | 780     | TBO             |

| 17 | 1.5.8-0        | 14  | LMN      | 16   | 2 6   | MA.          | -       |       |           | 8 x (255/237)  | 167.33            | 167.33        | 167.33                               | 79 | 180     | TEO             |

|    | UHL            | 15  | LMP      | 41.  |       | uuu          | -       | ÷     |           | 8 x (255/236)  | 168.04            | 168.04        | 168.04                               | 59 | 780     | TBO             |

| 19 | LHUN           | 16  | LMH      | 1h   |       | MAH .        |         | ÷     |           | 16             | 311.04            | 311.04        | 0.008                                | 10 | 180     | TEO             |

| 20 | LHLP           | 17  | LMH      |      | 5 L   | MHL          |         | ÷     |           | 32             | 622.08            | 622.08        | 0.008                                | 10 | TBO     | TBO             |

| _  | e: Lini        | 18  | UH,      | h    | -     | MHM          | ÷       | ÷     |           | 32 x (255/238) | 666.51            | 666.51        | 666.51                               | 14 | 180     | TEC             |

|    | unity          | 19  | LHL      | N LL | -     | 1.0-04       | -       | ÷     |           | 32 x (255/237) | 669.33            | 669.33        | 669.33                               | 79 | TBO     | TBO             |

|    |                | 20  | LHL      | ł    |       | HLL          | -       | ÷     |           | 32 x (255/236) | 672.16            | 672.16        | 672.16                               | 59 | 180     | TRO             |

|    |                | 160 | te: List | 61.  |       | HLM          |         | ÷     |           | 48             | 903.12            | 933.12        | 0.004                                | 10 | 180     | TBO             |

|    |                | -   |          | -1   | -     | нн           | ÷       | ÷     |           | 54             | 1048.76           | 1049.76       | 0.008                                | 10 | 780     | TEO             |

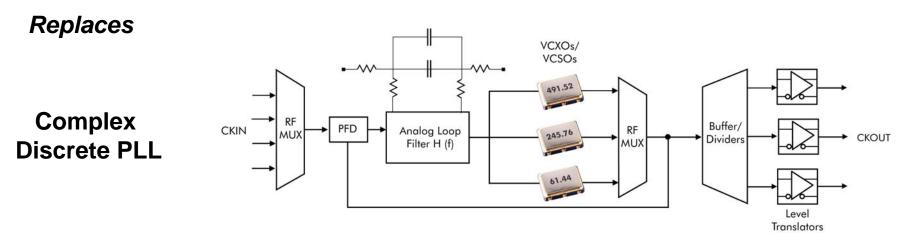

### **Key Feature—Integration**

Single IC

### Traditional PLL designs require many discrete components

- Multiple VCXO/VCSOs required for multi-frequency applications

- RF muxes, phase frequency detector, analog loop filter, low jitter buffers, etc.

#### Si53xx provides highly integrated solution

- Simplifies PLL design and layout

- Improves noise immunity since all loop components are integrated

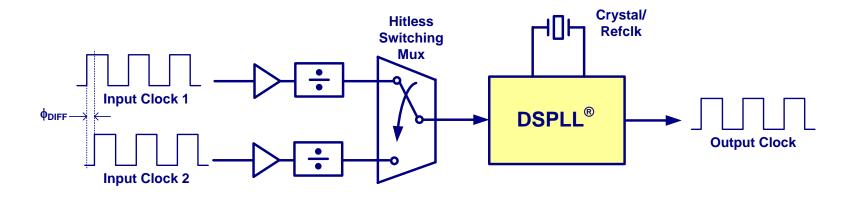

### **Key Feature—Hitless Switching**

Absorbs phase difference between input clocks during switchover

- Guarantees system BER in mission-critical telecom applications

- Meets SONET Stratum 3/3E phase transient requirements (MTIE)

- Simplifies clock switching in applications requiring multiple input clocks

- Automatic (revertive, non-revertive) and manual control options available

- Supports switching between clocks at different frequencies

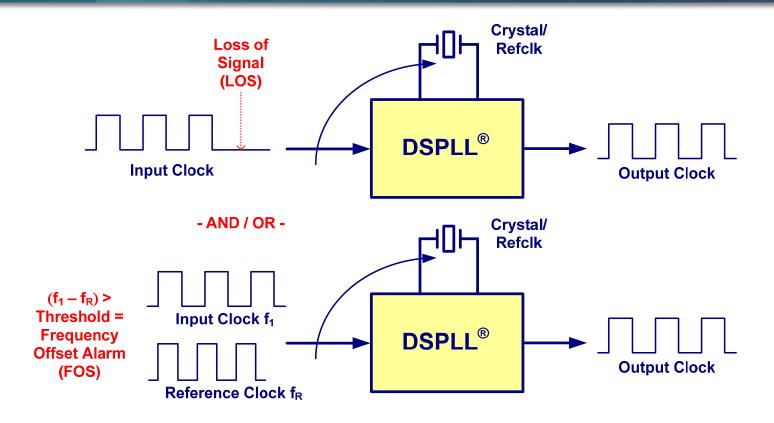

## **Key Feature—Digital Hold**

• Provides stable output clock in the absence of a valid input clock

- Entry to digital hold triggered by input clock alarm (LOS, FOS)

- Meets stringent telecom specifications for initial frequency accuracy

- Stratum 3E: 1 ppb

- Tracks crystal/reference clock's drift and temperature stability

### Si53xx Features and Benefits Summary

| Key Feature                            | Customer Benefits                                                                                                                         |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Any-rate frequency synthesis           | Replaces VCXO/VCSO-based PLL with IC solution<br>Reconfigurable to support multi-frequency operation<br>Simplifies design reuse           |

| Low jitter (0.3 ps rms typ)            | Great fit for high-performance applications<br>Additional design margin for less jitter-sensitive apps                                    |

| Integrated VCO and loop filter         | Simplifies design/layout<br>Adjustable jitter attenuation<br>Superior PSRR to discrete PLLs<br>Low phase noise in real-world applications |

| Multiple inputs with hitless switching | Simplifies design/layout<br>Comprehensive alarm monitoring<br>Meets telecom phase transient (MTIE) requirements                           |

| Multiple frequency flexible outputs    | Simplifies design/layout<br>Eliminates buffers, level translators                                                                         |

| IC-based solution                      | Short lead times: 4-6 weeks                                                                                                               |

SILICON LABS

### **Silicon Labs Any-Rate Precision Clocks**

|                       |                        |                         |                            |                         |                          | Jitter                     |                            |                 | , D                  | A                 | larn                | າຣ  |                  |                            |           |                |  |  |  |  |   |   |          |

|-----------------------|------------------------|-------------------------|----------------------------|-------------------------|--------------------------|----------------------------|----------------------------|-----------------|----------------------|-------------------|---------------------|-----|------------------|----------------------------|-----------|----------------|--|--|--|--|---|---|----------|

| Device                | No.<br>Clock<br>Inputs | No.<br>Clock<br>Outputs | Control                    | Input<br>Freq.<br>(MHz) | Output<br>Freq.<br>(MHz) | Gen<br>(50 kHz-<br>80 MHz) | Loop<br>BW                 | Clock<br>Mult.  | Hitless<br>Switching | LOL               | SOJ                 | FOS | Pkg.             |                            |           |                |  |  |  |  |   |   |          |

|                       |                        |                         |                            | Any-                    | Rate Preci               | sion Clock                 | Multipliers                |                 |                      |                   |                     |     |                  |                            |           |                |  |  |  |  |   |   |          |

| Si5322 <sup>1</sup>   | 2                      | 2                       | Pin                        | 15 to 707               | 19 to 1050               |                            |                            |                 |                      |                   | •                   |     | 6x6 mm           |                            |           |                |  |  |  |  |   |   |          |

| Si5325                |                        | 2                       | l <sup>2</sup> C or<br>SPI | 10 to 710               | 10 to 1400               | 0.6 ps                     | 30 kHz to                  | Y               | N                    |                   | •                   | •   | 36-QFN           |                            |           |                |  |  |  |  |   |   |          |

| Si5365 <sup>1</sup>   |                        | 4                       | Б                          | Pin                     | 15 to 707                | 19 to 1050                 | rms typ                    | 1.3 MHz         |                      |                   |                     | •   | •                | 14x14 mm                   |           |                |  |  |  |  |   |   |          |

| Si5367                | 4                      | Э                       | 5                          | Э                       | 5                        | 5                          | 5                          | 5               | 5                    | 5                 | 5                   | 5   | 5                | l <sup>2</sup> C or<br>SPI | 10 to 710 | 710 10 to 1400 |  |  |  |  | • | • | 100-TQFP |

|                       |                        |                         | Any-R                      | ate Precis              | ion Clock I              | Multipliers                | with Jitter A              | ttenuatio       | n                    |                   |                     |     |                  |                            |           |                |  |  |  |  |   |   |          |

| Si5316 <sup>1,2</sup> |                        | 1                       | Pin                        | 19 to 710               | 19 to 710                |                            |                            | Ν               | Ν                    | •                 | •                   |     |                  |                            |           |                |  |  |  |  |   |   |          |

| Si5323 <sup>1,2</sup> | 2                      | 2                       | Pin                        | 0.008 to<br>707         | 0.008 to<br>1050         |                            |                            |                 |                      | •                 | •                   |     | 6x6 mm<br>36-QFN |                            |           |                |  |  |  |  |   |   |          |

| Si5326 <sup>2</sup>   |                        |                         |                            |                         |                          | 2                          | l <sup>2</sup> C or<br>SPI | 0.002 to<br>710 | 0.002 to<br>1400     | 0.3 ps<br>rms typ | 60 Hz to<br>8.4 kHz | Y   | Y                | •                          | •         | •              |  |  |  |  |   |   |          |

| Si5366 <sup>1,2</sup> | 4                      | Б                       | Pin                        | 0.008 to<br>707         | 0.008 to<br>1050         |                            |                            | Ť               | r                    | •                 | •                   | •   | 14x14 mm         |                            |           |                |  |  |  |  |   |   |          |

| Si5368 <sup>2</sup>   | 4                      | 5                       | l <sup>2</sup> C or<br>SPI | 0.002 to<br>710         | 0.002 to<br>1400         |                            |                            |                 |                      | •                 | •                   | •   | 100-TQFP         |                            |           |                |  |  |  |  |   |   |          |

SILICON LABS

Note 1: Frequency plan pin-selectable from lookup table

Note 2: Requires external low-cost, fixed frequency crystal or 38.88 MHz reference clock

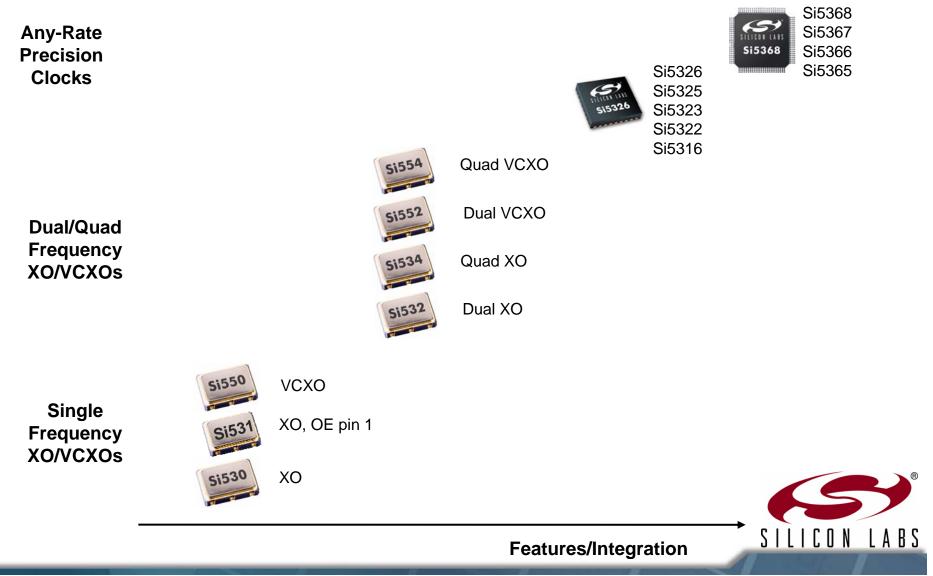

### **Silicon Labs Precision Timing Products**

Industry's broadest portfolio of frequency flexible, low jitter timing solutions

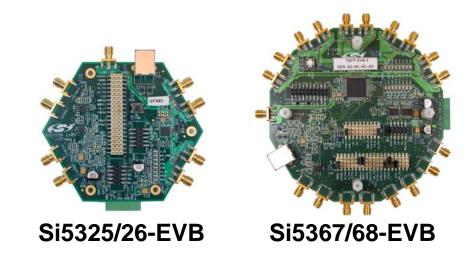

### **Sales Tools**

- Documentation available from <u>www.silabs.com/Timing</u>

- Data sheets

- EVB data sheets

- Evaluation boards

- > Si5316-EVB

- > Si5322/23-EVB

- > Si5325/26-EVB

- > Si5365/66-EVB

- > Si5367/68-EVB

- Documentation available from <u>www.mysilabs.com/SalesGuide/Timing/PrecisionClockICs</u>

- > DSPLL*sim* evaluation software

- Any-Rate Precision Clock Family Reference Manual

- Device errata

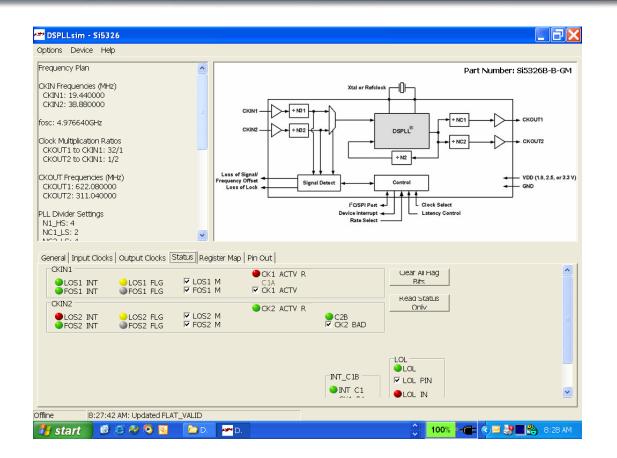

### DSPLLsim—Si53xx Customer Software

- Simplifies frequency planning, loop bandwidth selection, device configuration

- Provides listing of pin/register settings for desired configuration

Also used to control EVBs

### **Product Availability & Contact Info**

#### Product status

- > Samples: Available today!

- > Evaluation Boards: Available today!

- Production: 2Q'07

#### Contact

James Wilson Marketing Manager, Timing Products james.wilson@silabs.com Office Phone: +1-512-464-9233

David Yeh Product Manager, Timing Products <u>david.yeh@silabs.com</u> Office Phone: +1-512-532-5309

### Si53xx Summary

- Industry's first low jitter, any-rate clock multiplier/jitter attenuator family

- Industry-leading jitter performance

- Highly integrated and easy-to-use

# www.silabs.com/Timing