# NA2200 5V Analog Front End with High Gain PGA

Pseudo-differential<sup>(3)</sup>

1V/V to 512V/V

CRC8, Check Sum SSOP-16-BD

SPI

# FEATURES

- Supply Voltage +2.7V to +5.5V

- Ambient Operating Temperature -40°C to 125°C

- ADC Resolution

16-Bit (No missing codes)

- Data Rate

Input mode

Differential : 2 inputs

Single-ended <sup>(2)</sup> : 4 inputs

- PGA

- System Calibration for offset & gain drift

- Built-in Regulator

- Current Consumption Normal Mode 4mA

Low Power Mode 1.3mA

- Conversion mode

- n mode Single / Continuous

- Excitation Current Source 2 systems (0.1mA, 0.25mA, 0.5mA, 1.0mA)

- Interface

- CS (Chip Select)

- Error detection

- Package

# **GENERAL DESCRIPTION**

NA2200 is a CMOS-based 5V AFE with up to 512 times internal PGA (Programmable Gain Amplifier). Internal 16-bit  $\Delta\Sigma$  type A / D converter can perform conversion rates from 0.814ksps to 6.51ksps. The customer can choose internal A/D converter's input, among differential input, single-ended input and pseudo-differential input.

NA2200 can set the optimum gain to the pressure sensor, flow sensor by a wide range of gain setting. Various parameters (such as gain, conversion rate, correction) settings can be easily set in the SPI communication from an external MCU.

# APPLICATIONS

- Pressure sensors

- Flowmeters

- Current Measurement

- Thermostat

- PLC

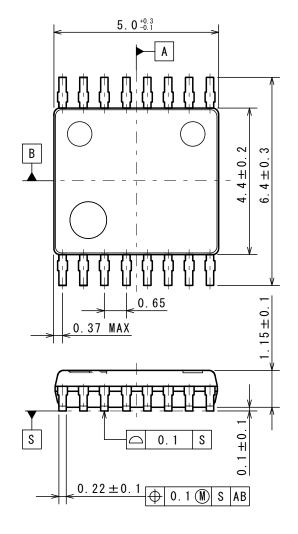

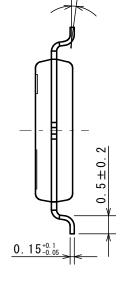

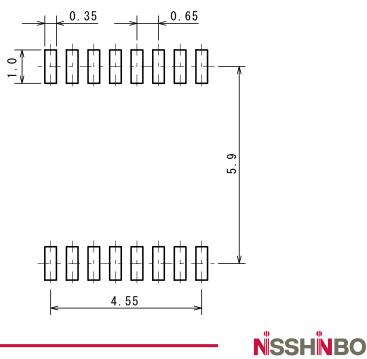

SSOP-16-BD 5.0 × 6.4 × 1.25(mm)

- (1) Case of single conversion. (Continuous conversion is three times the data rate.)

- (2) PGA2 can be used only. (PGA1 cannot be used.) Four channels of VIN1P, VIN1N, VIN2P & VIN2N can be used.

- (3) Bias voltage of VIN1P, VIN1N, VIN2P & VIN2N is common to VDD / 2. Input Signal can be used VIN1P and VIN2P only.

# ■ PRODUCT NAME INFORMATION

# NA2200 BD A E2 S

#### Description of configuration

| Suffix | Item         | Description                                            |

|--------|--------------|--------------------------------------------------------|

| BD     | Package code | Indicates the package. Refer to the order information. |

| А      | Version      | Product Version. Default is A.                         |

| E2     | Packing      | Refer to the packing specifications.                   |

| S      | Grade        | Indicates the quality grade.                           |

#### Grade

| Grade | Usage                                       | Operating Temperature Range | Test Temperature |

|-------|---------------------------------------------|-----------------------------|------------------|

| S     | General-purpose<br>and Consumer application | −40°C to 125°C              | 25°C             |

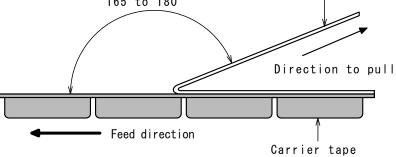

# ORDER INFORMATION

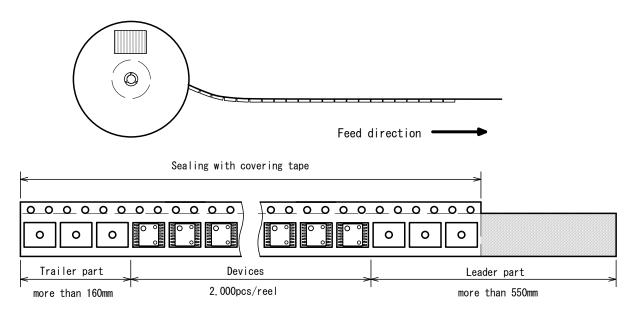

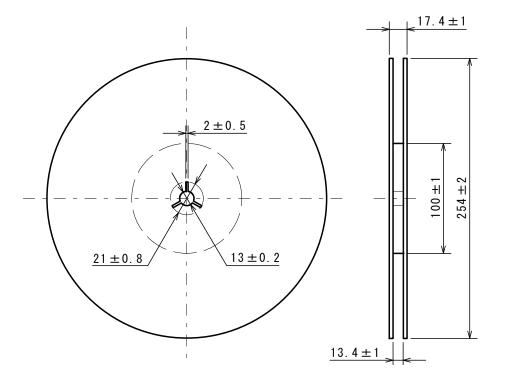

| Product Name | Package    | RoHS | Halogen-<br>Free | Terminal<br>Finish | Weight<br>(mg) | Quantity per Reel<br>(pcs) |

|--------------|------------|------|------------------|--------------------|----------------|----------------------------|

| NA2200BDAE2S | SSOP-16-BD | Yes  | Yes              | Sn-2Bi             | 68.00          | 2,000                      |

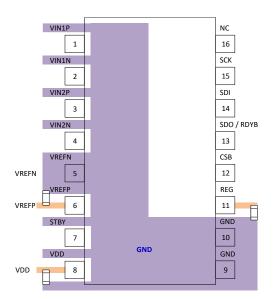

#### ■ PIN DESCRIPTION

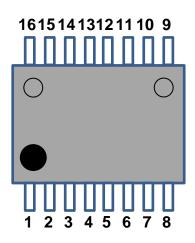

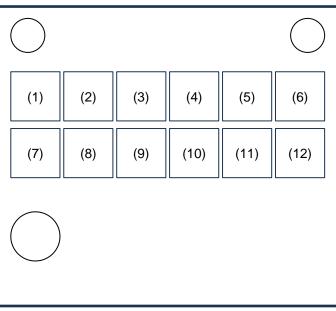

## SSOP-16-BD Pin Configuration

| Pin No. | Pin Name   | I/O            | Description                                                                               |

|---------|------------|----------------|-------------------------------------------------------------------------------------------|

| 1       | VIN1P      | Analog Input   | +INPUT 1 for differential mode / INPUT 1 for single-ended mode                            |

| 2       | VIN1N      | Analog Input   | -INPUT 1 for differential mode / INPUT 2 for single-ended mode                            |

| 3       | VIN2P      | Analog Input   | +INPUT 2 for differential mode / INPUT 3 for single-ended mode                            |

| 4       | VIN2N      | Analog Input   | -INPUT 2 for differential mode / INPUT 4 for single-ended mode                            |

| 5       | VREFN      | Analog Input   | -Reference Voltage Input                                                                  |

| 6       | VREFP      | Analog Input   | +Reference Voltage Input                                                                  |

| 7       | STBY       | Digital Input  | Standby Mode                                                                              |

| 8       | VDD        | Power Supply   | Supply Voltage                                                                            |

| 9       | GND        | GND            | GND                                                                                       |

| 10      | GND        | GND            | GND                                                                                       |

| 11      | REG        | Analog Output  | Built-in Regulator for Digital Power Supply (Place a decoupling capacitor close to 11pin) |

| 12      | CSB        | Digital Input  | SPI Chip Select                                                                           |

| 13      | SDO / RDYB | Digital Output | SPI serial data output / RDYB output                                                      |

| 14      | SDI        | Digital Input  | SPI serial data input                                                                     |

| 15      | SCK        | Digital Input  | SPI serial clock input                                                                    |

| 16      | NC         | GND            | Non Connection                                                                            |

Please refer to "TYPICAL APPLICATION CIRCUIT" or "APPLICATION NOTES" for details.

# ABSOLUTE MAXIMUM RATINGS

|                             | Symbol              | Ratings                                   | Unit |

|-----------------------------|---------------------|-------------------------------------------|------|

| Power Supply Voltage        | VDD <sub>abso</sub> | 7.0 (4)                                   | V    |

| Power Dissipation           | PD                  | 900 <sup>(5)</sup> / 1,300 <sup>(6)</sup> | mW   |

| Analog Input Voltage        | Vin                 | -0.3 to (VDD+0.3) <sup>(7)</sup>          | V    |

| Operating Temperature Range | T <sub>opr</sub>    | -40 to 125                                | °C   |

| Storage Temperature Range   | T <sub>stg</sub>    | -40 to 150                                | °C   |

(4) The difference between the absolute maximum power supply voltage and the operating power supply voltage is small. Please be careful so that the operating power supply voltage does not exceed the absolute maximum supply voltage by spike voltage.

- (5) Mounted on glass epoxy board.

(114.3 x 76.2 x 1.57mm: based on EIA/JEDEC standard, 2Layers FR-4.)

(6) Mounted on glass epoxy board.

- (114.3 x 76.2 x 1.6mm: based on EIA/JEDEC standard, 4Layers FR-4.)

- (7) Input pin is connected to the clamp diode to the power supply pin. When the input signal exceeds the supply rails 0.3V or more (below the GND rail 0.3V or more), the input current must be limited to less than 10mA.

#### **ABSOLUTE MAXIMUM RATINGS**

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the lifetime and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings is not assured.

V

V

kΩ

kΩ

dB

# ELECTRICAL CHARACTERISTICS

Ratio 1

## **ELECTRICAL CHARACTERISTICS (Analog Input)**

Unless otherwise specified, all limits ensured for  $T_a = +25$ °C, VDD = 5.0V, GND = 0V, VREFP = 0.5 x VDD, VREFN = 0V, PGAIN1 = PGAIN2 = 1, VCIN2 = 0.5 x VDD, DR = 0.814ksps or 1.63ksps

| Parameter | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|-----------|--------|------------|------|------|------|------|

|-----------|--------|------------|------|------|------|------|

|              | Analog Input 1 (PGA1 = unused         | l, PGA2 = use | d, PGAIN2 = 1 or 4)          |     |                     |     |

|--------------|---------------------------------------|---------------|------------------------------|-----|---------------------|-----|

|              | Differential Input Voltage<br>Range 1 | VDIN1         |                              | -   | ±VREF<br>/ (PGAIN2) | -   |

|              | Common Mode Input Voltage<br>Range 1  | VCIN1         |                              | GND | -                   | VDD |

|              | Innut Impedance 1                     | 70.14         | FMOD = 1.25MHz<br>PGAIN2 = 1 | -   | 600                 | -   |

| Input Impeda | Input Impedance 1                     | ZIN1          | FMOD = 1.25MHz<br>PGAIN2 = 4 | -   | 300                 | -   |

|              | Common Mode Rejection                 | CMPP1         |                              | 70  | 00                  |     |

#### Analog Input 2 (PGA1, 2 = used, PGAIN1 = 1 or 2 or 4 or 8 or 16 or 32 or 64 or 128, PGAIN2=1 or 4)

| Differential Input Voltage<br>Range 2 | VDIN2 | PGAIN1 ≥ 2                            | -   | (±VREF)<br>/ (PGAIN1<br>x PGAIN2) | -           | V  |

|---------------------------------------|-------|---------------------------------------|-----|-----------------------------------|-------------|----|

| Common Mode Input Voltage<br>Range 2  | VCIN2 |                                       | 0.1 | -                                 | VDD<br>-1.2 | V  |

| Input Impedance 2                     | ZIN2  |                                       | -   | 100                               | -           | MΩ |

| Common Mode Rejection<br>Ratio 2      | CMRR2 | PGAIN1 = 2<br>PGAIN2 = 1<br>CHOP = ON | 70  | 90                                | -           | dB |

PGAIN2 = 1

70

90

# ELECTRICAL CHARACTERISTICS (Reference Voltage Input)

Unless otherwise specified, all limits ensured for  $T_a = +25$  °C, VDD = 5.0V, GND = 0V

CMRR1

| Parameter                 | Symbol | Conditions                   | MIN. | TYP. | MAX.        | Unit |

|---------------------------|--------|------------------------------|------|------|-------------|------|

| Reference Voltage         | VREF   | VREF = VREFP - VREFN         | 2.0  | -    | VDD         | V    |

| VREFN Input Voltage Range | VREFN  |                              | 0    | -    | VDD<br>-2.5 | V    |

| Input Impedance 3         | ZIN3   | FMOD = 1.25MHz<br>PGAIN2 = 1 | -    | 180  | -           | kΩ   |

|                           |        | FMOD = 1.25MHz<br>PGAIN2 = 4 | -    | 250  | -           | kΩ   |

# **ELECTRICAL CHARACTERISTICS (Internal Regulator)**

| Unless otherwise specified, all limits ensured for $T_a = +25$ °C, VDD = 5.0V, GN            | D = 0V |

|----------------------------------------------------------------------------------------------|--------|

| $-$ 011633 01161 wise specified, all inflits ensured for $T_a = \pm 25$ C, $vDD = 5.0$ V, ON | D = 0  |

| Parameter         | Symbol | Conditions                                                                        | MIN.  | TYP. | MAX.  | Unit   |

|-------------------|--------|-----------------------------------------------------------------------------------|-------|------|-------|--------|

| Output Voltage    | REG    |                                                                                   | 2.376 | 2.4  | 2.424 | V      |

| Temperature Drift | REG_TD | Ta = 25 to 125°C<br>(REG125–REG25) / REG25 x<br>10 ^ 6 / (125 -25) <sup>(8)</sup> | -     | -25  | -     | ppm/°C |

(8) REG25 -> Measured value at 25°C. REG125 -> Measured value at 125°C.

# ELECTRICAL CHARACTERISTICS (Internal Oscillator)

Unless otherwise specified, all limits ensured for  $T_a = +25$ °C, VDD = 5.0V, GND = 0V

| Paramete   | r   | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|------------|-----|--------|------------|------|------|------|------|

| OSC Freque | ncy | FOSC   |            | 2.25 | 2.5  | 2.75 | MHz  |

## **ELECTRICAL CHARACTERISTICS (Excitation Current Source)**

Unless otherwise specified, all limits ensured for  $T_a = +25$  °C, VDD = 5.0V, GND = 0V

| Parameter                           | Symbol    | Conditions                                                                             | MIN. | TYP.                      | MAX. | Unit   |

|-------------------------------------|-----------|----------------------------------------------------------------------------------------|------|---------------------------|------|--------|

| Output Current                      | IEX       | VINxx = 1.2V                                                                           | -    | 0.10, 0.25,<br>0.50, 1.00 | -    | mA     |

| Absolute Value<br>Deviation         | IEX_E     | (Measured Value – IEX) / IEX<br>x 100                                                  | -    | -                         | ±10  | %      |

| Matching Error                      | IEX_ME    | IEX1 = 1mA,<br>(IEX2 - IEX1) / IEX1 x 100 <sup>(9)</sup>                               | -    | -                         | ±1   | %      |

| Temperature Drift                   | IEX_TD    | Ta = 25 to 125°C<br>(IEX125 - IEX25) / IEX125 x<br>10 ^ 6 / (125 - 25) <sup>(10)</sup> | -    | -300                      | -    | ppm/°C |

| Temperature Drift<br>Matching Error | IEX_TD_ME | IEX2_TD - IEX1_TD (11)                                                                 | -    | ±2                        | -    | ppm/°C |

(9) IEX1 -> Measured value of Excitation current source 1.

IEX2 -> Measured value of Excitation current source 2.

(10) IEX25 -> Measured value at 25°C.

IEX125 -> Measured value at 125°C.

(11) IEX1\_TD -> Temperature Drift of Excitation current source 1.

IEX2\_TD -> Temperature Drift of Excitation current source 2.

# ELECTRICAL CHARACTERISTICS (Programmable Gain Amplifier)

Unless otherwise specified, all limits ensured for  $T_a = +25^{\circ}C$ , VDD = 5.0V, GND = 0V

|   | Parameter | Symbol | Conditions | MIN. | TYP.                               | MAX. | Unit |

|---|-----------|--------|------------|------|------------------------------------|------|------|

| _ | PGA1 Gain | PGAIN1 |            | -    | 1, 2, 4, 8,<br>16, 32, 64,<br>128, | -    | V/V  |

| - | PGA2 Gain | PGAIN2 |            | -    | 1, 4                               | -    | V/V  |

# **ELECTRICAL CHARACTERISTICS (Analog to Digital Convertor)**

Unless otherwise specified, all limits ensured for  $T_a = +25^{\circ}C$ , VDD = 5.0V, GND = 0V, VREFP = 0.5 x VDD, VREFN = 0V, PGAIN1 = PGAIN2 = 1, VCIN2 = 0.5 x VDD

| Parameter                              | Symbol         | Conditions                                                         | MIN.    | TYP.           | MAX.     | Unit |

|----------------------------------------|----------------|--------------------------------------------------------------------|---------|----------------|----------|------|

| Resolution                             | N              | No missing codes <sup>(12)</sup>                                   | 16      |                |          | Bit  |

| Data Rate                              | DR             | Single Conversion <sup>(13)</sup><br>Normal Mode                   | 0.814k  | , 1.63k, 3.26k | , 6.51k  | 0.00 |

| Dala Nale                              | DIX            | Single Conversion <sup>(13)</sup><br>Low Power Mode                | 0.203k, | 0.407k, 0.814  | k, 1.63k | sps  |

| Clock Frequency                        | FMOD<br>(MDCK) | FMOD = FOSC / 2                                                    | 1.125   | 1.25           | 1.375    | MHz  |

| Integral Non Linearity                 | INL            | best-fit-line method <sup>(14)</sup><br>VREFP = 5.0V<br>PGAIN1 = 2 | -       | ±30            | ±60      | ppm  |

| Offset Error                           | OE             | PGAIN1 = 128<br>CHOP = OFF                                         | -       | ±150           | -        | μV   |

| Oliset Ellor                           | OE             | PGAIN1 = 128<br>CHOP = ON                                          | -       | ±1             | ±10      | μV   |

| Gain Error                             | GE             | PGAIN1 = 128<br>PGAIN2 = 1                                         | -       | ±0.5           | ±2.0     | %    |

| Noise Free Bit <sup>(12)(15)(16)</sup> |                | VDIN2 = 0V<br>VREFP = 5.0V<br>VREFN = 0V<br>DR = 0.814ksps         | -       | 15             | -        | Bit  |

|                                        | NFB            | VDIN2 = 0V<br>VREFP = 5.0V<br>VREFN = 0V<br>DR = 1.63ksps          | -       | 14             | -        | Bit  |

(12) This parameter is not production tested.(13) There is no latency by one settling behavior.

(14) Guaranteed by design evaluation and several points test

(15) See table of Effective resolution and Noise Free Bit(NFB) (see page 25 to 26).

(16) NFB represents the ADC output code variations 6.6 with the differential input shorted.

# ELECTRICAL CHARACTERISTICS (Power Supply / Supply Current)

# Unless otherwise specified, all limits ensured for $T_a = +25^{\circ}C$ , VDD = 5.0V, GND = 0V

| Parameter                      | Symbol                     | Conditions                                  | MIN. | TYP.  | MAX. | Unit |

|--------------------------------|----------------------------|---------------------------------------------|------|-------|------|------|

| Power Supply Voltage           | VDD                        |                                             | 2.7  | 5.0   | 5.5  | V    |

| Supply Current                 |                            | PGA OFF                                     | 1.4  | 2.3   | 3.3  | mA   |

| Normal Mode                    | IDD                        | PGA ON                                      | 2.7  | 4.0   | 5.7  | mA   |

| Supply Current                 |                            | PGA OFF                                     | 0.6  | 0.9   | 1.4  | mA   |

| Low Power Mode                 | IDD <sub>LOW</sub>         | PGA ON                                      | 0.85 | 1.3   | 1.9  | mA   |

| Supply Current<br>Sleep Mode   | IDDSLEEP                   | Sleep Mode                                  | 0.14 | 0.27  | 0.4  | mA   |

| Supply Current<br>Standby Mode | <b>IDD</b> <sub>STBY</sub> | Standby Mode<br>STBY = VDD<br>Regulator OFF | -    | 0.001 | 0.1  | μA   |

# ELECTRICAL CHARACTERISTICS (Digital I/Os)

# Unless otherwise specified, all limits ensured for $T_a = +25^{\circ}C$ , VDD = 5.0V, GND = 0V

| Parameter                    | Symbol          | Conditions                | MIN.         | TYP. | MAX.         | Unit |

|------------------------------|-----------------|---------------------------|--------------|------|--------------|------|

| High-level input<br>voltage  | V <sub>ih</sub> |                           | 0.7<br>x VDD | -    | -            | V    |

| Low-level input<br>voltage   | Vil             |                           | -            | -    | 0.2<br>x VDD | V    |

| High-level output<br>voltage | V <sub>oh</sub> | I <sub>oh</sub> max.= 6mA | 0.8<br>x VDD | -    | -            | V    |

| Low-level output<br>voltage  | Vol             | l₀⊨max.= 6mA              | -            | -    | 0.4          | V    |

| Parameter                                                       | Symbol            | MIN. | TYP. | MAX. | Unit |

|-----------------------------------------------------------------|-------------------|------|------|------|------|

| SPI clock frequency                                             | f <sub>sck</sub>  | -    | -    | 10   | MHz  |

| Setup time, CSB falling edge to first SCK rising edge           | t1                | 45   | -    | -    | nsec |

| Hold time, final SCK falling edge to CSB rising edge            | t2                | 45   | -    | -    | nsec |

| Pulse duration, SCK high                                        | t3                | 45   | -    | -    | nsec |

| Pulse duration, SCK low                                         | t4                | 45   | -    | -    | nsec |

| Setup time, SDI input data valid before SCK falling edge        | t5                | 10   | -    | -    | nsec |

| Hold time, SDI input data valid after SCK falling edge          | t6                | 10   | -    | -    | nsec |

| Setup time, CSB falling edge to SDO / RDYB output<br>data       | t7                | 0    | -    | 30   | nsec |

| Setup time, SCK rising edge to SDO / RDYB output<br>data        | t8                | 0    | -    | 40   | nsec |

| Hold time, SCK falling edge of LSB to SDO / RDYB<br>output data | t9                | 10   | -    | 50   | nsec |

| Setup time, CSB rising edge to SDO / RDYB changing to HiZ       | t10               | 0    | -    | 30   | nsec |

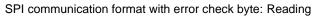

| Reset time                                                      | t <sub>rstw</sub> | -    | -    | 400  | nsec |

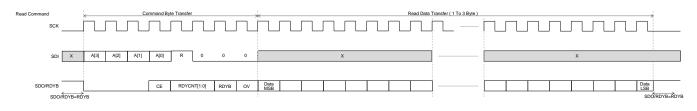

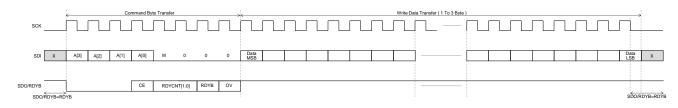

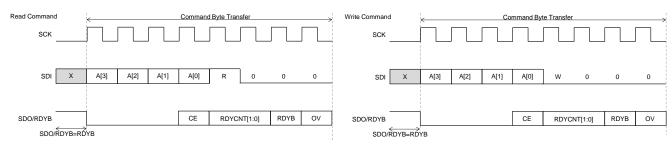

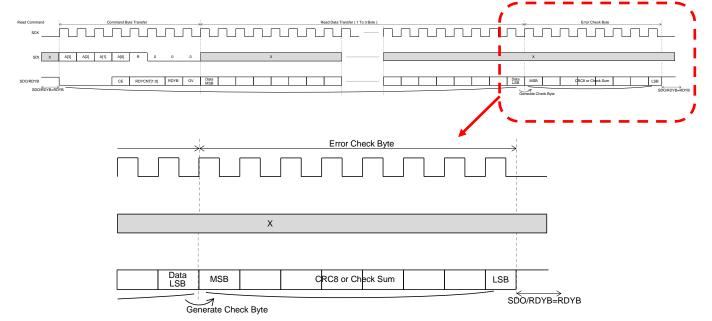

# ELECTRICAL CHARACTERISTICS (Serial Peripheral Interface)

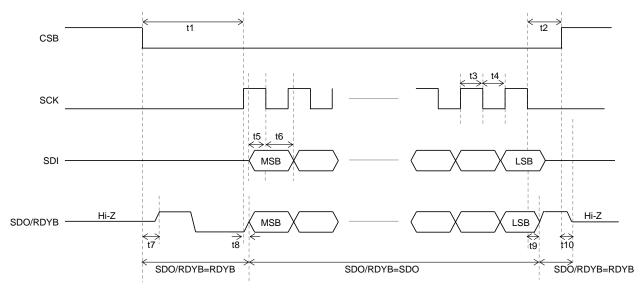

- The SPI AC timing is shown in the figure below. It is the communication of 10Mbps at the highest speed.

- Capacitance Load of SDO / RDYB terminal is assumed to 40pF

SPI AC timing

# REGISTER DESCRIPTION

NA2200 has register (list shown below) which can access it through SPI bus. Registers with different data lengths (1 to 3 bytes) are assigned to 4-Bit register address.

| Register<br>Address | Register<br>Name | Data Length<br>[byte] |

|---------------------|------------------|-----------------------|

| 0x0                 | CTRL             | 2-Byte (16-Bit)       |

| 0x1                 | ADCDATA          | 2-Byte (16-Bit)       |

| 0x2                 | IEXCONF          | 2-Byte (16-Bit)       |

| 0x3                 | PGACONF          | 1-Byte (8-Bit)        |

| 0x4                 | CLKCONF          | 1-Byte (8-Bit)        |

| 0x5                 | Not used         | -                     |

| 0x6                 | OPTION0          | 1-Byte (8-Bit)        |

| 0x7                 | Not used         | -                     |

| 0x8                 | GAIN1            | 3-Byte (24-Bit)       |

| 0x9                 | GAIN2            | 3-Byte (24-Bit)       |

| 0xA                 | Not used         | -                     |

| 0xB                 | Not used         | -                     |

| 0xC                 | OFFSET1          | 3-Byte (24-Bit)       |

| 0xD                 | OFFSET2          | 3-Byte (24-Bit)       |

| 0xE                 | Not used         | -                     |

| 0xF                 | Not used         | -                     |

#### < View of the register table>

|          | Register Name |     |     |     |     |     |     |     |  |

|----------|---------------|-----|-----|-----|-----|-----|-----|-----|--|

| Bit      | [7]           | [6] | [5] | [4] | [3] | [2] | [1] | [0] |  |

| Bit Name |               |     |     |     |     |     |     |     |  |

| R/W      |               |     |     |     |     |     |     |     |  |

| Reset    |               |     |     |     |     |     |     |     |  |

R / W: Bit of attribute (Read or Write)

- R (Read Only) : Read only

- W (Write Only) : Write only (At the time of read, return "0".)

- RW (Read Write) : Read & Write

- RC (Read / Write 1 to Clear bit) : Read returns the register value.

Writing 1 clears the bit to 0. Writing 0 does not affect the operation.

Reset: Reset value in register

Set to the reset value by SPI reset command and power-on reset.

NA2200

# REGISTER DESCRIPTION

# **CTRL Register**

|          | Register Address: 0x0 |      |            |      |      |        |     |     |

|----------|-----------------------|------|------------|------|------|--------|-----|-----|

|          | CTRL                  |      |            |      |      |        |     |     |

| Bit      | [15]                  | [14] | [13]       | [12] | [11] | [10]   | [9] | [8] |

| Bit Name | -                     |      | CHSELN     |      |      | CHSELP |     |     |

| R/W      | -                     |      | RW         |      |      | RW     |     |     |

| Reset    | -                     |      | 0x4        |      | -    | 0x4    |     |     |

| Bit      | [7]                   | [6]  | [5]        | [4]  | [3]  | [2]    | [1] | [0] |

| Bit Name | RDY                   | CNT  | NT RDYB OV |      |      | MC     | DE  |     |

| R/W      | F                     | R R  |            |      |      | R      | W   |     |

| Reset    | 0:                    | к0   | 1          | 0    |      | 0:     | x0  |     |

| Bit     | Bit Name | Function                                                                                                                                                                                           |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15]    | -        | -                                                                                                                                                                                                  |

| [14:12] | CHSELN   | Analog input channel setting of negative side.<br>Refer the below table: CHSELP / CHSELN Register.                                                                                                 |

| [11]    | -        | -                                                                                                                                                                                                  |

| [10:8]  | CHSELP   | Analog input channel setting of positive side.<br>Refer the below table: CHSELP / CHSELN Register.                                                                                                 |

| [7:6]   | RDYCNT   | Modulo operation counter.<br>2-Bit modulo operation counter that adds 1 each time the ADCDATA resister is updated.                                                                                 |

| [5]     | RDYB     | Data ready flag. When conversion data is updated, this bit is set to "0".<br>When ADCDATA read, this bit set to "1".<br>0: Conversion completion<br>1: Conversion non-completion                   |

| [4]     | OV       | Overflow flag. When conversion data is overflow, this bit is set to "1".<br>When ADCDATA read, this bit is set to "0".<br>0: Valid<br>1: Overflow (Invalid)                                        |

| [3:0]   | MODE     | Operation mode setting.<br>When this bit is "write", sets the operation mode of ADC.<br>When this bit is "read", returns the current configuration state.<br>Refer the below table : MODE Register |

# Table 1 CHSELP / CHSELN Bit

| CHSELP | Positive |

|--------|----------|

| 0x0    | VIN1P    |

| 0x1    | VIN1N    |

| 0x2    | VIN2P    |

| 0x3    | VIN2N    |

| 0x4    | VREFN    |

| 0x5    | VREFP    |

| 0x6    | REG      |

| 0x7    | GND      |

| CHSELN | Negative |

|--------|----------|

| 0x0    | VIN1P    |

| 0x1    | VIN1N    |

| 0x2    | VIN2P    |

| 0x3    | VIN2N    |

| 0x4    | VREFN    |

| 0x5    | VREFP    |

| 0x6    | REG      |

| 0x7    | GND      |

Datasheet

NA2200

| MODE | Operation                 | Processing                                                                  |

|------|---------------------------|-----------------------------------------------------------------------------|

| 0x0  | ldle                      | Waiting state of conversion operation or calibration                        |

|      |                           | Setting the state of low power consumption which conversion operation or    |

| 0x1  | Sleep                     | calibration is available.                                                   |

|      |                           | Start-up time is inserted automatically before conversion operation.        |

|      |                           | Convert once the input channel that is selected in the CHSELP / N.          |

| 0x2  | Single conversion         | After the conversion, the operation is "Idle (0x0)" state.                  |

|      |                           | Using the value of the "OFFSET1, 2" register.                               |

|      |                           | Convert continuous the input channel that is selected in the CHSELP / N.    |

| 0x3  | Continuous conversion     | Until the operation is set to "Idle (0x0)", conversion will continue.       |

|      |                           | Using the value of the "OFFSET1, 2" register.                               |

| 0x4  | Single conversion         | This is the same as "Single conversion (0x2)", but the data rate is 1/2.    |

| 074  | + CHOP                    | Not using the value of the "OFFSET1, 2" register.                           |

| 0x5  | Continuous conversion     | This is the same as "Continuous conversion (0x3)", but the data rate is 1/3 |

| 0,0  | + CHOP                    | Not using the value of the "OFFSET1, 2" register.                           |

|      |                           | This is the same as "Single conversion (0x2)", but the data rate is 1/2.    |

| 0x6  | Single conversion         | Not using the value of the "OFFSET1, 2" register.                           |

| 0.00 | + CHOP + IEX CHOP         | CHOP operation is valid. The connection channel of IEX1 and IEX2 is         |

|      |                           | switched in conjunction with the CHOP operation.                            |

|      |                           | This is the same as "Continuous conversion (0x3)", but the data rate is 1/3 |

| 0x7  | Continuous conversion     | Not using the value of the "OFFSET1, 2" register.                           |

| •    | + CHOP + IEX CHOP         | CHOP operation is valid. The connection channel of IEX1 and IEX2 is         |

|      |                           | switched in conjunction with the CHOP operation.                            |

| 0x8  | Not used <sup>(17)</sup>  | -                                                                           |

| 0x9  | Not used <sup>(17)</sup>  | -                                                                           |

| 0xA  | Not used <sup>(17)</sup>  | -                                                                           |

| 0xB  | Not used <sup>(17)</sup>  | -                                                                           |

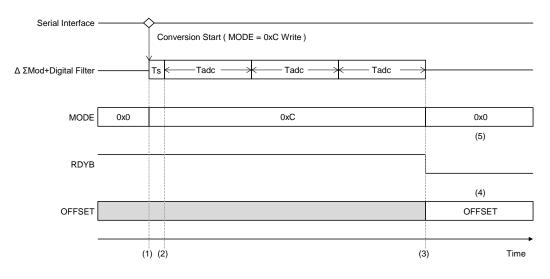

| 0xC  | Calibration system offset | Input is selected by CHSELP / N, system offset is calibrated.               |

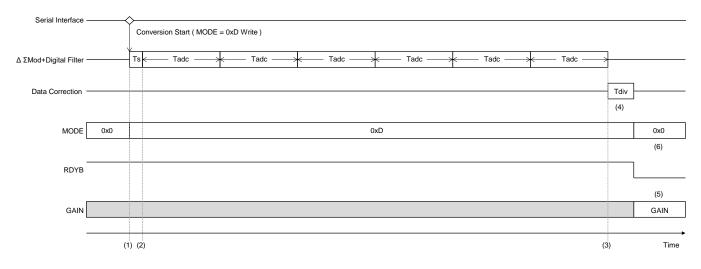

| 0xD  | Calibration system gain   | Input is selected by CHSELP / N, system gain is calibrated.                 |

| 0xE  | Not used <sup>(17)</sup>  | -                                                                           |

| 0xF  | Boot                      | Read only. It shows the state from the reset to change to "Idle (0x0)".     |

| UXF  | DUUL                      | After the initial setting, automatically shifts to the "Idle (0x0)".        |

(17) Please do not absolutely use the "Not used" code. It will be the cause of failure.

Datasheet

NA2200

# **ADCDATA Register**

|          |      | Register       | r Address: 0x1                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|----------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|          |      |                | ADCDATA                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Bit      | [15] | [14] [13] [12] | [11] [10] [9] [8] [7] [6] [5] [4] [3] [2] [1] [0]                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Bit Name |      |                | ADCDATA                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| R/W      |      |                | R                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Reset    |      |                | •                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|          |      |                |                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Bit      |      | Bit Name       | Function                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| [15:0]   |      | ADCDATA        | Store the converted data of the ADC. <sup>(18)</sup><br>Conversion data is expressed as a signed 16-bit.<br>- When the input voltage is negative full-scale, the output is 0x8000<br>- When the input voltage is zero, the output is 0x0000<br>- When the input voltage is positive full-scale, the output is 0x7FFF.<br>(in decimal -32768 to +32767) |  |  |  |  |  |  |  |  |  |

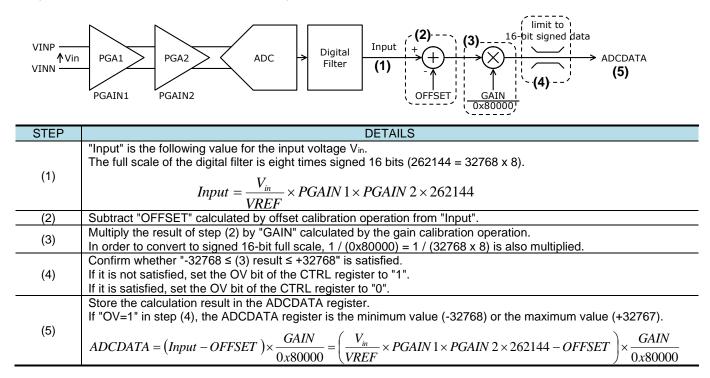

(18) Relationship of conversion data ADCDATA and the analog input voltage V<sub>in</sub> is as the following equation. (It assumed that the offset error and gain error are zero.)

$$ADCDATA = \frac{V_{in}}{2 \times VREF} \times PGAIN 1 \times PGAIN 2 \times 2^{16} = \frac{V_{in}}{VREF} \times PGAIN 1 \times PGAIN 2 \times 2^{15}$$

# **IEXCONF** Register

|          |                                   | Regist | er Address: 0 | x2      |     |         |         |     |  |  |  |  |  |

|----------|-----------------------------------|--------|---------------|---------|-----|---------|---------|-----|--|--|--|--|--|

|          |                                   |        |               | IEXCONF |     |         |         |     |  |  |  |  |  |

| Bit      | [15] [14] [13] [12] [11] [10] [9] |        |               |         |     |         |         |     |  |  |  |  |  |

| Bit Name | IEX2SLP                           |        | IEX2C         |         | -   | IEX2_EN | IEX2    | SEL |  |  |  |  |  |

| R/W      | RW                                |        | RW            |         | -   | RW      | RW      |     |  |  |  |  |  |

| Reset    | 0                                 |        | 0x0           |         | -   | 0       | 0x0     |     |  |  |  |  |  |

| Bit      | [7]                               | [6]    | [5]           | [4]     | [3] | [2]     | [1] [0] |     |  |  |  |  |  |

| Bit Name | IEX1SLP                           |        | IEX1C         |         | -   | IEX1_EN | IEX1SEL |     |  |  |  |  |  |

| R/W      | RW                                |        | RW            |         | -   | RW      | RW      |     |  |  |  |  |  |

| Reset    | 0                                 |        | 0x0           |         | -   | 0       | 0>      | :0  |  |  |  |  |  |

| Bit     | Bit Name | Function                                                                                                                                                                                          |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15]    | IEX2SLP  | <ul> <li>Condition setting of IEX2 at sleep mode by AUTOSLP bit = "1" of OPTION0 register.</li> <li>0: IEX2 current depends on IEX2C</li> <li>1: IEX2 OFF</li> </ul>                              |

| [14:12] | IEX2C    | Current setting of IEX2.           0x0:         0.10mA           0x1:         0.25mA           0x2:         0.50mA           0x3:         1.00mA           0x4 to 0x7: Not used <sup>(17)</sup> . |

| [11]    | -        | ·                                                                                                                                                                                                 |

| [10]    | IEX2_EN  | Setting ON / OFF of IEX2.<br>0: IEX2 OFF (Open)<br>1: IEX2 ON                                                                                                                                     |

| [9:8]   | IEX2SEL  | Connection setting of IEX2.<br>0x0: VIN1P<br>0x1: VIN1N<br>0x2: VIN2P<br>0x3: VIN2N                                                                                                               |

(17) Please do not absolutely use the "Not used" code. It will be the cause of failure.

Datasheet

NA2200

| Bit   | Bit Name | Function                                                                                                                                                             |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]   | IEX1SLP  | <ul> <li>Condition setting of IEX1 at sleep mode by AUTOSLP bit = "1" of OPTION0 register.</li> <li>0: IEX1 current depends on IEX1C</li> <li>1: IEX1 OFF</li> </ul> |

| [6:4] | IEX1C    | Current setting of IEX1.<br>0x0: 0.10mA<br>0x1: 0.25mA<br>0x2: 0.50mA<br>0x3: 1.00mA<br>0x4 to 0x7: Not used <sup>(17)</sup> .                                       |

| [3]   | -        | •                                                                                                                                                                    |

| [2]   | IEX1_EN  | Setting ON / OFF of IEX1.<br>0: IEX1 OFF (Open)<br>1: IEX1 ON                                                                                                        |

| [1:0] | IEX1SEL  | Connection setting of IEX1.<br>0x0: VIN1P<br>0x1: VIN1N<br>0x2: VIN2P<br>0x3: VIN2N                                                                                  |

(17) Please do not absolutely use the "Not used" code. It will be the cause of failure.

# **PGACONF** Register

|          |          | Regis                                                                                                                                                                                                                                                                   | ter Address: 0x                  | 3       |        |     |          |     |  |  |  |  |  |  |  |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------|--------|-----|----------|-----|--|--|--|--|--|--|--|

|          |          |                                                                                                                                                                                                                                                                         |                                  | PGACONF |        |     |          |     |  |  |  |  |  |  |  |

| Bit      | [7]      | [6]                                                                                                                                                                                                                                                                     | [5]                              | [4]     | [3]    | [2] | [1]      | [0] |  |  |  |  |  |  |  |

| Bit Name | -        | -                                                                                                                                                                                                                                                                       | PGA2GAIN                         | -       | PGA1EN |     | PGA1GAIN |     |  |  |  |  |  |  |  |

| R/W      | -        | -                                                                                                                                                                                                                                                                       | RW                               | -       | RW     |     | RW       |     |  |  |  |  |  |  |  |

| Reset    | -        | -                                                                                                                                                                                                                                                                       | - 0 - 0 0x0                      |         |        |     |          |     |  |  |  |  |  |  |  |

|          |          |                                                                                                                                                                                                                                                                         |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

| Bit      | Bit Name |                                                                                                                                                                                                                                                                         |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

| [7:6]    | -        |                                                                                                                                                                                                                                                                         |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

| [5]      | PGA2GAIN | Gain setting of PGA2.                                                                                                                                                                                                                                                   |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

| [4]      | -        | -                                                                                                                                                                                                                                                                       |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

| [3]      | PGA1EN   | 0: PG                                                                                                                                                                                                                                                                   | ON / OFF of P<br>A1 OFF<br>A1 ON | GA1.    |        |     |          |     |  |  |  |  |  |  |  |

| [2:0]    | PGA1GAIN | 1:         PGA1 ON           Gain setting of PGA1.           0x0:         x1           0x1:         x2           0x2:         x4           0x3:         x8           0x4:         x16           0x5:         x32           0x6:         x64           0x7:         x128 |                                  |         |        |     |          |     |  |  |  |  |  |  |  |

# **CLKCONF** Register

|          |         | Regist | er Address: 0 | x4   |   |     |     |  |  |  |  |  |  |  |

|----------|---------|--------|---------------|------|---|-----|-----|--|--|--|--|--|--|--|

|          | CLKCONF |        |               |      |   |     |     |  |  |  |  |  |  |  |

| Bit      |         |        |               |      |   |     |     |  |  |  |  |  |  |  |

| Bit Name | -       | -      | CLK           | (DIV | - | OSR |     |  |  |  |  |  |  |  |

| R/W      | -       | -      | R             | W    | - | RW  |     |  |  |  |  |  |  |  |

| Reset    | -       | -      | 0:            | x0   | - |     | 0x3 |  |  |  |  |  |  |  |

|          |         |        |               |      |   |     |     |  |  |  |  |  |  |  |

| Bit   | Bit Name               | Function                                                                                                                                                                                              |

|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | -                      | -                                                                                                                                                                                                     |

| [5:4] | CLKDIV <sup>(19)</sup> | Setting of the ADC operating clock frequency (FMOD). FOSC is the operating clock of the internal OSC.<br>0x0: FOSC / 2<br>0x1: FOSC / 4<br>0x2: FOSC / 8<br>0x3: FOSC/ 16                             |

| [3]   | -                      | •                                                                                                                                                                                                     |

| [2:0] | OSR                    | Setting of the oversampling ratio of the digital filter         0x0:       64         0x1:       128         0x2:       256         0x3:       512         0x4 to 0x7:       Not used <sup>(17)</sup> |

(17) Please do not absolutely use the "Not used" code. It will be the cause of failure.

(19) Data rate is derived by the following equation. It will be the data rate of a single conversion.

$$DR = F_{OSC} \times \frac{1}{OSR} \times \frac{1}{2^{(CLKDIV+1)}} \times \frac{1}{3}$$

If FOSC is 2.5MHz of (TYP.), Conversion data rate will be set in the table below.

|     |                              | Date Rate [sps]         |                         |                         |  |  |  |  |  |  |  |  |  |  |

|-----|------------------------------|-------------------------|-------------------------|-------------------------|--|--|--|--|--|--|--|--|--|--|

| OSR | CLKDIV=0<br>(Recommendation) | CLKDIV=1 <sup>(*)</sup> | CLKDIV=2 <sup>(*)</sup> | CLKDIV=3 <sup>(*)</sup> |  |  |  |  |  |  |  |  |  |  |

| 512 | 0.814k                       | 0.407k                  | 0.204k                  | 0.102k                  |  |  |  |  |  |  |  |  |  |  |

| 256 | 1.63k                        | 0.814k                  | 0.407k                  | 0.204k                  |  |  |  |  |  |  |  |  |  |  |

| 128 | 3.26k                        | 1.63k                   | 0.814k                  | 0.407k                  |  |  |  |  |  |  |  |  |  |  |

| 64  | 6.51k                        | 3.26k                   | 1.63k                   | 0.814k                  |  |  |  |  |  |  |  |  |  |  |

(\*) This parameter is not production tested.

NA2200

# **OPTION0** Register

|          |            | Reg                          | ister Address:                              | 0x6                                                                 |              |            |                 |             |  |  |  |  |  |  |  |

|----------|------------|------------------------------|---------------------------------------------|---------------------------------------------------------------------|--------------|------------|-----------------|-------------|--|--|--|--|--|--|--|

|          |            |                              |                                             | OPTION0                                                             |              |            |                 |             |  |  |  |  |  |  |  |

| Bit      | [7]        | [6]                          | [5]                                         | [4]                                                                 | [3]          | [2]        | [1]             | [0]         |  |  |  |  |  |  |  |

| Bit Name |            | )                            | LPW_EN                                      | REF_INT_EN                                                          |              | IODE       | CE              | AUTOSLP     |  |  |  |  |  |  |  |

| R / W    | R          |                              | RW                                          | RW                                                                  |              | W          | RC              | RW          |  |  |  |  |  |  |  |

| Reset    | 0x2        |                              | 0                                           | 0                                                                   | 0:           | x0         | 0               | 0           |  |  |  |  |  |  |  |

|          |            | _                            |                                             |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| Bit      | Bit Name   |                              | Function                                    |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| [7:6]    | CHIPID     | Used to identify the chip.   |                                             |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| [5]      | LPW_EN     | ADC CLKD                     | IV setting.<br>Normal Mode<br>Low Power Mo  |                                                                     | D) becomes F | FMOD = FOS | SC / 8 regardl  | ess of      |  |  |  |  |  |  |  |

| [4]      | REF_INT_EN | 0: E<br>1: I                 |                                             |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| [3:2]    | CEMODE     | 0: 0<br>1: 0<br>2: 0<br>3: 0 | 1: Use prohibition<br>2: CRC8               |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| [1]      | CE         | Sum).<br>0: 1<br>1: (        |                                             |                                                                     |              |            |                 |             |  |  |  |  |  |  |  |

| [0]      | AUTOSLP    | 0: (<br>1: (                 | ON (Wait)<br>OFF (Power do<br>When the cust | (0x0), set to ON /<br>own)<br>tomer change AUT<br>the analog block. |              |            | sion start is n | ecessary to |  |  |  |  |  |  |  |

# GAIN1 / GAIN2 Register

|          |      |                   | R    | egiste | er Ad | dress | : 0x8                    | , 0x                           | 9                  |                                        |                   |                |                  |                 |                  |               |                |             |     |        |      |      |        |     |

|----------|------|-------------------|------|--------|-------|-------|--------------------------|--------------------------------|--------------------|----------------------------------------|-------------------|----------------|------------------|-----------------|------------------|---------------|----------------|-------------|-----|--------|------|------|--------|-----|

|          |      |                   |      |        |       |       |                          |                                |                    |                                        | GAIN              | 1/G            | AIN2             |                 |                  |               |                |             |     |        |      |      |        |     |

| Bit      | [23] | [22]              | [21] | [20]   | [19]  | [18]  | [17]                     | [16]                           | [1                 | 5] [14]                                | [13]              | [12]           | [11]             | [10]            | [9]              | [8]           | [7]            | [6]         | [5] | [4]    | [3]  | [2   | ] [1]  | [0] |

| Bit Name |      |                   |      |        |       |       |                          |                                |                    |                                        |                   | GAIN           |                  |                 |                  |               |                |             |     |        |      |      |        |     |

| R/W      |      | RW                |      |        |       |       |                          |                                |                    |                                        |                   |                |                  |                 |                  |               |                |             |     |        |      |      |        |     |

| Reset    |      | 0x00 0x00 0x00    |      |        |       |       |                          |                                |                    |                                        |                   |                |                  |                 |                  |               |                |             |     |        |      |      |        |     |

|          |      |                   |      |        |       |       |                          |                                |                    |                                        |                   |                |                  |                 |                  |               |                |             |     |        |      |      |        |     |

| Bit      |      | Bit Name Function |      |        |       |       |                          |                                |                    |                                        |                   |                |                  |                 |                  |               |                |             |     |        |      |      |        |     |

| [23:0]   |      |                   |      | GAIN   | N     |       | 18-bi<br>The c<br>active | t uns<br>custo<br>e on<br>se o | sign<br>ome<br>ly. | ent de<br>led coo<br>er can<br>iting g | efficie<br>do the | nt, GA<br>exte | AIN [2<br>rnal v | 23:18<br>writin | 8] is a<br>g gai | ilway<br>n co | /s "0<br>effic | ".<br>ient, | whe | en int | erna | l cl | ock is |     |

# **OFFSET1 / OFFSET2 Register**

Register Address: 0xC, 0xD

|          |           | OFFSET1 / OFFSET2 |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

|----------|-----------|-------------------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit      | [23]      | [22]              | [21] | [20] | [19] | [18] | [17] | [16] | [15] | [14] | [13] | [12] | [11] | [10] | [9] | [8] | [7] | [6] | [5] | [4] | [3] | [2] | [1] | [0] |

| Bit Name |           | OFFSET            |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| R/W      |           | RW                |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| Reset    | 0x00 0x00 |                   |      |      |      |      |      |      |      |      |      |      |      |      |     |     | 0x  | 00  |     |     |     |     |     |     |

| Bit    | Bit Name | Function                                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [23:0] | OFFSET   | Offset coefficient derived in offset calibration or the external writing offset coefficient.<br>20-bit signed coefficient, OFFSET [23:20] is sign-extended value. <sup>(20)</sup><br>The customer can do the external writing offset coefficient, when internal clock is active only.<br>In case of writing offset coefficient, please set to "0" AUTOSLP bit of OPTION0 register. |

(20) Sign - extended: If the sign is (-) fill the 1 in the free space. If the sign is (+) fill the "0" in the free space - In the case of -4 in decimal 8- bit is "1111100".

16-bit sign extension is "11111111 1111100".

- In the case of +4 in decimal 8-bit is "00000100"

16-bit sign extension is "00000000 00000100"

The GAINn and OFFSETn registers are used for the coefficients used in gain and offset calibration. "n" is determined by the setting value on the positive input side, CTRL Register 0x0 CHSELP[10:8]. Refer the below table: Data Calibration Coefficient Correspondence Table 3.

Table 3

Data Calibration Coefficient Correspondence Table

| CHSELP Set<br>Value | Positive | Gain n Register | OFFSET n<br>Register |

|---------------------|----------|-----------------|----------------------|

| 0x0                 | VIN1P    | GAIN1           | OFFSET1              |

| 0x1                 | VIN1N    | GAIN1           | OFFSET1              |

| 0x2                 | VIN2P    | GAIN2           | OFFSET2              |

| 0x3                 | VIN2N    | GAIN2           | OFFSET2              |

| 0x4                 | VREFN    | GAIN1           | OFFSET1              |

| 0x5                 | VREFP    | GAIN1           | OFFSET1              |

| 0x6                 | REG      | GAIN1           | OFFSET1              |

| 0x7                 | GND      | GAIN1           | OFFSET1              |

# **TYPICAL APPLICATION CIRCUIT**

**NA2200 Typical Application Circuit**

#### Notes on External Parts

Place a decoupling capacitor  $0.1\mu$ F close to 11pin (REG). A decoupling capacitor should be connected to ground for stability.

The regulator is optimized for NA2200 operation, so do not connect any components other than the decoupling capacitor to 11pin(REG).

It is recommended that 5pin (VREFN) is connected to ground.

The printed circuit board (PCB) layout pattern example of NA2200 is shown below.

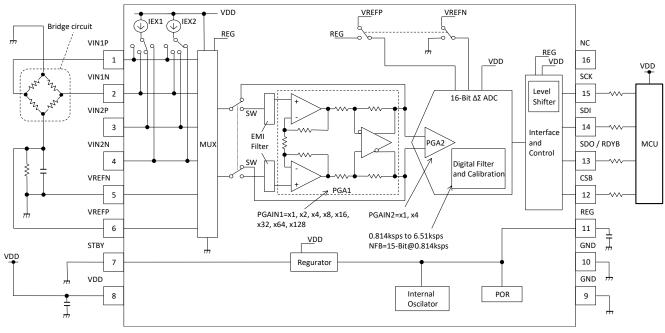

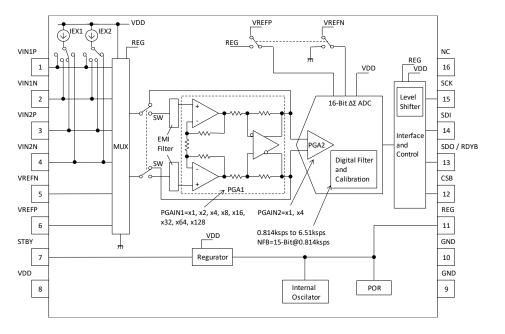

# BLOCK DIAGRAM

#### NA2200 Block Diagram

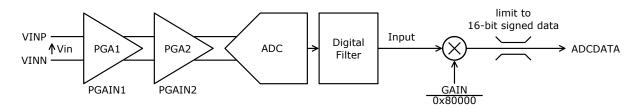

## OPERATING DESCRIPTION

The NA2200 uses a PGA (Programmable Gain Amplifier) to amplify analog signals obtained from sensors and other devices connected to the VIN1P / VIN1N / VIN2P / VIN2N input terminals. Combination of PGA1 / PGA2 can amplify signals up to 512 times. The amplified signal is converted to digital data by a 16-Bit  $\Delta\Sigma$  ADC, and after signal processing such as offset calibration and gain calibration, the digital signal is output to the MCU via SPI communication. A built-in level shifter outputs digital signals at the VDD level, so it can be connected to a 5V MCU. It supports up to 2 inputs in differential mode and up to 4 inputs in single-ended mode.

It has two excitation current sources and can used for temperature controller applications using resistance temperature detectors.

The reference voltage source for the ADC can be set to either an external reference voltage VREFP / VREFN input externally or an internal reference voltage REG using an internal regulator.

In addition to Normal Mode, Low Power Mode (conversion speed 1/4 and current consumption 1/4 compared to Normal Mode), Sleep Mode (OFF except bias and REG circuit), and Standby Mode (all circuit OFF, current consumption 0.1µA or less) can be selected.

## APPLICATION NOTES

#### TERMINAL DESCRIPTION

#### • 1pin (VIN1P), 2pin (VIN1N), 3pin (VIN2P), 4pin (VIN2N), Analog Input terminals, Excitation Current Source Output terminals

Analog input terminals for inputting signals from external sources such as sensors. It supports up to 2 inputs in differential mode and up to 4 inputs in single-ended mode.

CHSELP and CHSELN in CTRL register 0x0 select the analog input channel for data conversion (built-in multiplexer function).

NA2200 has two excitation current sources to provide a constant current to the sensors. IEXCONF register 0x2 selects the analog input channel to which the excitation current source is connected and the current value can be set.

#### • 5pin (VREFN), 6pin (VREFP), Reference Voltage Input terminals

Reference voltage input terminals. Negative input / positive input are supported.

#### • 7pin (STBY), Standby terminal

Standby terminal. NA2200 is in Standby Mode when STBY = VDD.

## • 8pin (VDD), Power Supply terminal

Power supply terminal. The applied DC voltage range is 2.7V to 5.5V.

#### • 9pin (GND), 10pin (GND), Ground terminals

Ground terminals of NA2200.

#### • 11pin (REG), Built-in regulator output terminal for digital power supply

NA2200 has a built-in regulator for digital power supply. 11pin (REG) is the output terminal. A decoupling capacitor should be connected to ground for stability. Place a decoupling capacitor close to 11pin (REG). The regulator is optimized for NA2200 operation, so do not connect any components other than the decoupling capacitor.

#### • 12pin (CSB), SPI chip select terminal

NA2200 serial interface chip select terminal. It is a digital input terminal. When the CSB terminal is high level, SCK and SDI are disabled and communication is not possible. When the CSB terminal is low level, SCK and SDI are enable and communication is possible. After the CSB terminal changes from high to low level, the state of the SPI slave interface is reset and the command byte must be resent.

## • 13pin (SDO/RDYB), SPI serial data output / RDYB terminal

NA2200 serial interface data output / RDYB terminal. It is a digital output terminal. When reading, data from the SDO/RDYB terminal is communicated MSB first. SDO/RDYB is synchronized to the rising edge of SCK. The RDYB bit outputs "1" or "0" depending on whether the ADC is converting or not. (1: conversion in progress or 0: conversion completed)

#### • 14pin (SDI), SPI serial data input terminal

NA2200 serial interface data input terminal. It is a digital input terminal. When writing, data to the SDI terminal is communicated MSB first. SDI is captured on the falling edge of SCK.

#### • 15pin (SCK), SPI serial clock input terminal

NA2200 serial interface clock input terminal. It is a digital input terminal.

# • 16pin (NC), Non connection

Non connection terminal. Ground the terminal.

#### Power up sequence

When the power supply pin VDD reaches a voltage at which the circuit can operate, the internal reset is released by the built-in power-on reset circuit and initialization begins.

After the reset is released, the startup sequence of the NA2200 is completed after a waiting period of about 600µsec.

(The waiting time of about 600µsec does not include the power-on time.)

After the startup sequence is completed, the device transitions to the idle state and is ready for AD conversion operation.

# ■ Effective resolution, Noise Free Bit (NFB)

Data Rate (DR) is speed at the time of single conversion (1 settling). Output code variation  $\sigma$  is the effective resolution in the VIN1P and VIN1N (or VIN2P and VIN2N) connected to VDD/2, 6.6 $\sigma$  is the NFB.

- < Condition >

- FMOD=1.25MHz

- VDD=5.0V, GND=0V

- VREFP=5.0V, VREFN=0V

- Differential input

- CHOP OFF

- Ta=+25°C

# (1) Normal Mode & External REF

| ′   | Nonna | DR vs. Effective resolution (Unit: bit) |      |      |                              |      |      |        |      |      |      |      |      |

|-----|-------|-----------------------------------------|------|------|------------------------------|------|------|--------|------|------|------|------|------|

| OSR | DR    | PGA                                     |      |      |                              |      | F    | PGA ON |      |      |      |      |      |

|     | USK   | [sps]                                   | OFF  | x1   | x2                           | x4   | x8   | X16    | x32  | x64  | x128 | x256 | x512 |

|     | 512   | 0.814k                                  | 16   | 16   | 6 16 16 16 16 16 16 16 16 16 |      |      |        |      |      |      |      |      |

|     | 256   | 1.63k                                   | 16   | 16   | 16                           | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   |

|     | 128   | 3.26k                                   | 16   | 16   | 16                           | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 15   |

|     | 64    | 6.51k                                   | 14.5 | 14.5 | 14.5                         | 14.5 | 14.5 | 14.5   | 14.5 | 14.5 | 14.5 | 14.5 | 12.5 |

#### DR vs. NFB (Unit: bit)

| OSR | DR        | PGA  |      | PGA ON |      |      |      |      |      |      |      |      |

|-----|-----------|------|------|--------|------|------|------|------|------|------|------|------|

| USK | USR [sps] | OFF  | x1   | x2     | x4   | x8   | x16  | x32  | x64  | x128 | x256 | x512 |

| 512 | 0.814k    | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 14.5 | 14   |

| 256 | 1.63k     | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 14.5 | 14   |

| 128 | 3.26k     | 14   | 14   | 14     | 14   | 14   | 14   | 14   | 14   | 14   | 13   | 12.5 |

| 64  | 6.51k     | 11.5 | 11.5 | 11.5   | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 10   |

(2) Low Power Mode & External REF

DR vs. Effective resolution (Unit: bit)

| OSR | DR     | PGA  |      | PGA ON |      |      |      |      |      |      |      |      |

|-----|--------|------|------|--------|------|------|------|------|------|------|------|------|

| USK | [sps]  | OFF  | x1   | x2     | x4   | x8   | X16  | x32  | x64  | x128 | x256 | x512 |

| 512 | 0.203k | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 16   | 16   |

| 256 | 0.407k | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 16   | 16   |

| 128 | 0.814k | 16   | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 14   | 14   |

| 64  | 1.63k  | 14.5 | 14.5 | 14.5   | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 12.5 | 12.5 |

#### DR vs. NFB (Unit: bit)

| OSR DR | PGA    |      | PGA ON |      |      |      |      |      |      |      |      |      |  |  |

|--------|--------|------|--------|------|------|------|------|------|------|------|------|------|--|--|

| USK    | [sps]  | OFF  | x1     | x2   | x4   | x8   | x16  | x32  | x64  | x128 | x256 | x512 |  |  |

| 512    | 0.203k | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 16   | 14.5 | 14.5 |  |  |

| 256    | 0.407k | 16   | 16     | 16   | 16   | 16   | 16   | 16   | 16   | 16   | 14   | 14   |  |  |

| 128    | 0.814k | 14   | 14     | 14   | 14   | 14   | 14   | 14   | 14   | 14   | 11.5 | 11.5 |  |  |

| 64     | 1.63k  | 11.5 | 11.5   | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 10   | 10   |  |  |

Datasheet

NA2200

# (3) Normal Mode & Internal REF

| " | nonna |        |     |    |                                 |           |           |            |            |     |      |      |      |

|---|-------|--------|-----|----|---------------------------------|-----------|-----------|------------|------------|-----|------|------|------|

|   |       |        |     |    | DR ۱                            | vs. Effec | tive reso | olution (l | Unit: bit) |     |      |      |      |

|   | OSR   |        | PGA |    |                                 |           |           | F          | PGA ON     |     |      |      |      |

|   | USK   | [sps]  | OFF | x1 | x2                              | x4        | x8        | X16        | x32        | x64 | x128 | x256 | x512 |

|   | 512   | 0.814k | 16  | 16 | 6 16 16 16 16 16 16 16 16 16 16 |           |           |            |            |     | 16   |      |      |

|   | 256   | 1.63k  | 16  | 16 | 16                              | 16        | 16        | 16         | 16         | 16  | 16   | 16   | 15.5 |

|   | 128   | 3.26k  | 16  | 16 | 16 16 16 16 16 16 16 16 15 15   |           |           |            |            |     |      |      |      |

| _ | 64    | 6.51k  | 14  | 14 | 14                              | 14        | 14        | 14         | 14         | 14  | 14   | 12   | 12   |

## DR vs. NFB (Unit: bit)

| OSR  | DR      | PGA  |      |      |      |      | F    | 'GA ON |      |      |      |      |

|------|---------|------|------|------|------|------|------|--------|------|------|------|------|

| USIX | K [sps] | OFF  | x1   | x2   | x4   | x8   | x16  | x32    | x64  | x128 | x256 | x512 |

| 512  | 0.814k  | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5   | 14.5 | 14   | 13.5 | 13   |

| 256  | 1.63k   | 14   | 14   | 14   | 14   | 14   | 14   | 14     | 14   | 14   | 13   | 13   |

| 128  | 3.26k   | 13   | 13   | 13   | 13   | 13   | 13   | 13     | 13   | 13   | 12   | 12   |

| 64   | 6.51k   | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5   | 11.5 | 11.5 | 9.5  | 9.5  |

(4) Low Power Mode & Internal REF

DR vs. Effective resolution (Unit: bit)

| OSR | DR     | PGA<br>OFF |    | PGA ON |    |    |     |     |     |      |      |      |  |  |  |

|-----|--------|------------|----|--------|----|----|-----|-----|-----|------|------|------|--|--|--|

| USK | [sps]  |            | x1 | x2     | x4 | x8 | X16 | x32 | x64 | x128 | x256 | x512 |  |  |  |

| 512 | 0.203k | 16         | 16 | 16     | 16 | 16 | 16  | 16  | 16  | 16   | 16   | 16   |  |  |  |

| 256 | 0.407k | 16         | 16 | 16     | 16 | 16 | 16  | 16  | 16  | 16   | 16   | 16   |  |  |  |

| 128 | 0.814k | 16         | 16 | 16     | 16 | 16 | 16  | 16  | 16  | 16   | 15   | 15   |  |  |  |

| 64  | 1.63k  | 14         | 14 | 14     | 14 | 14 | 14  | 14  | 14  | 14   | 13.5 | 12.5 |  |  |  |

#### DR vs. NFB (Unit: bit)

| OSR | DR     | PGA  |      |      |      |      | PGA ON |      |      |      |      |      |

|-----|--------|------|------|------|------|------|--------|------|------|------|------|------|

| USK | [sps]  | OFF  | x1   | x2   | x4   | x8   | x16    | x32  | x64  | x128 | x256 | x512 |

| 512 | 0.203k | 14.5 | 14.5 | 14.5 | 14.5 | 14.5 | 14.5   | 14.5 | 14.5 | 14   | 13.5 | 13.5 |

| 256 | 0.407k | 14   | 14   | 14   | 14   | 14   | 14     | 14   | 14   | 14   | 13.5 | 13   |

| 128 | 0.814k | 13   | 13   | 13   | 13   | 13   | 13     | 13   | 13   | 13   | 12.5 | 12   |

| 64  | 1.63k  | 11.5 | 11.5 | 11.5 | 11.5 | 11.5 | 11.5   | 11.5 | 11.5 | 11.5 | 11   | 10   |

NA2200

NA2200

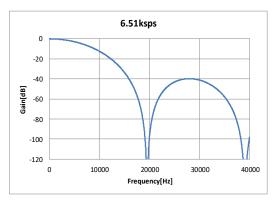

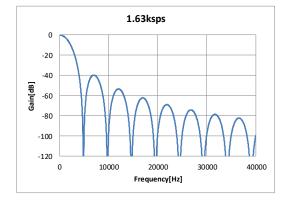

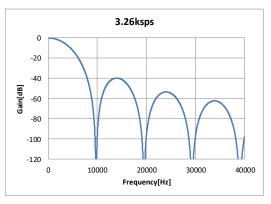

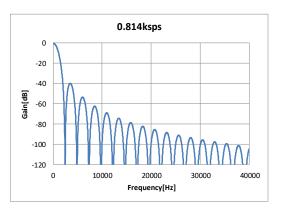

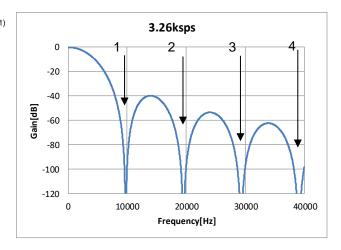

#### Digital filter frequency characteristic

The output of the ΔΣ modulator is converted to a digital value of high resolution by a digital filter (third-order Sinc filter). Frequency characteristics will change depending on the data rate.

When the conversion data rate (DR) is 6.51ksps, 3.26ksps, 1.63ksps, 0.814ksps, frequency characteristics of the digital filter is shown below. Characteristic is the case of FMOD=1.25MHz.

DR=1.63ksps

It has a first notch in the frequency of the data rate x 3. Or later, it has a notch to the integer multiple of the position.<sup>(21)</sup>

- (e.x.) In the case 3.26ksps (Figure of right)

- Position of the notch

- 1. 9.8kHz (3.26kHz x 3 x 1)

- 2. 19.6kHz (3.26kHz x 3 x 2)

- 3. 29.3kHz (3.26kHz x 3 x 3)

- 4. 39.1kHz (3.26kHz x 3 x 4)

- (N) 3.26kHz x 3 x N (N is an integer)

DR=3.26ksps

DR=3.26ksps

(21) Position of the notch varies in proportion to the frequency of the FMOD

FMOD is  $\pm 10\%$  variation. Position of the notch is likely to vary  $\pm 10\%$  from the above figure.

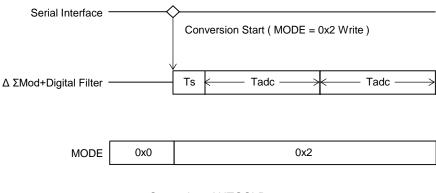

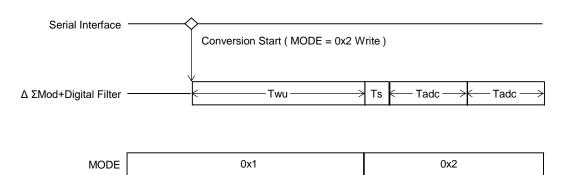

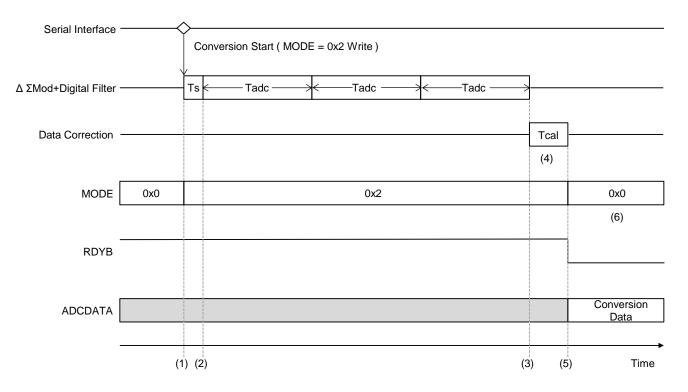

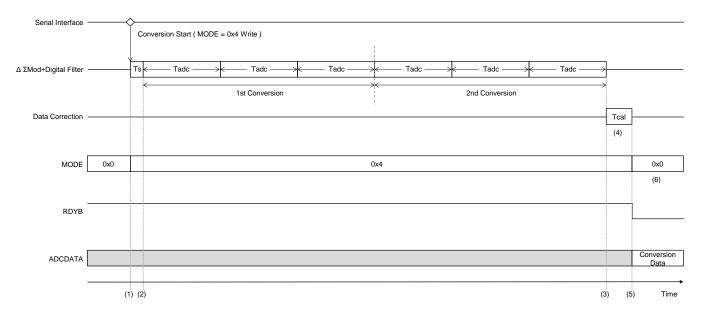

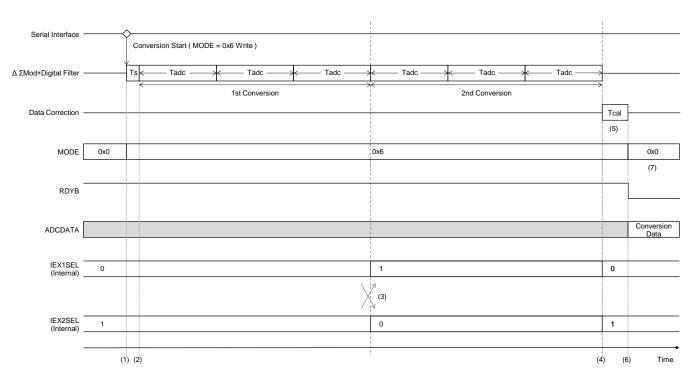

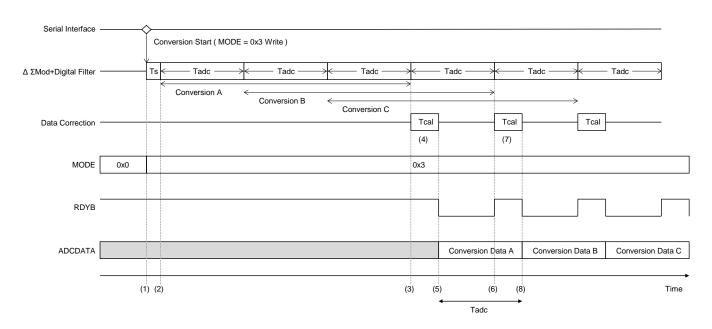

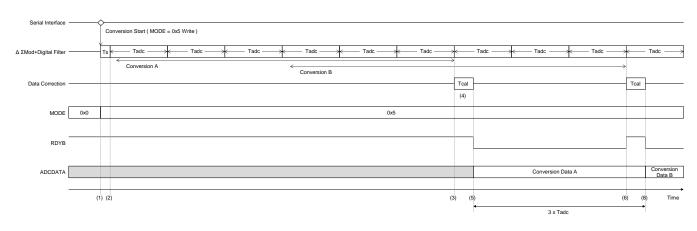

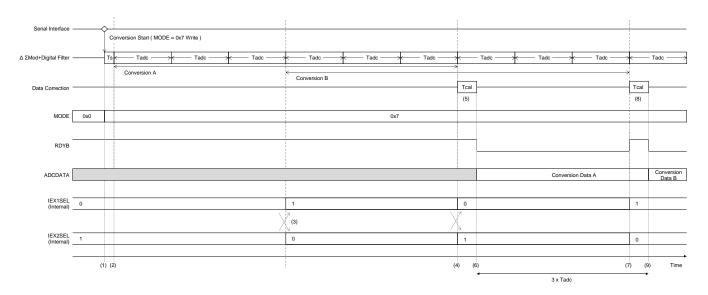

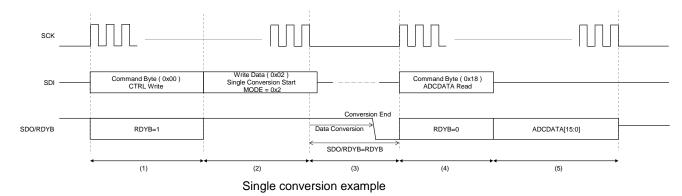

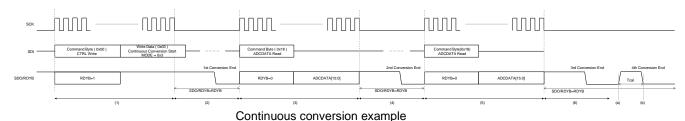

# Conversion Control

Set the conversion operation by MODE bit of CTRL register.

| MODE                 | OPERATION                                  | Power on Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |