12 V, 2 A to 13.5 A, 17 mΩ eFuse Rev. 1 — 18 July 2024

### 1. General description

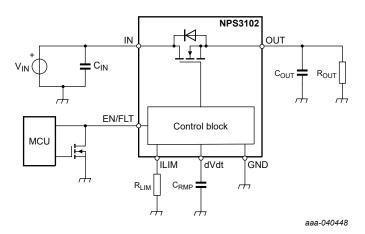

NPS3102A and NPS3102B are low-ohmic (17 m $\Omega$ ), high current (13.5 A), resettable electronic fuses that are targeted for 12 V applications. They are designed to protect downstream loads from exposure to excessive voltage and protect the power supply from load faults and large inrush currents.

Output slew rate is controlled by a capacitor at dVdt pin. Current limit can be adjusted in the 2 A to 13.5 A range using a resistor at ILIM pin. The voltage at ILIM pin can also be used as a measure of the load current in real-time. The devices include a built-in over voltage clamp that will limit the output voltage during input over voltage conditions.

The devices also include a multi-function EN/FLT pin. When the pin is left floating and the voltage at IN is greater than the under voltage lock-out, the devices turn on. During operation, the voltage at the pin can be used as a fault indicator to determine if the devices are operating normally. Pulling the EN/FLT pin low will turn off the devices.

During thermal shutdown, both devices disable the integrated pass-FET if the die temperature crosses the over temperature threshold. The NPS3102A latches off under a thermal shutdown event and requires user reset by toggling the EN/FLT pin or cycling the voltage at the IN pin. The NPS3102B integrates autoretry, which safely attempts to re-enable the pass-FET without the need for user intervention.

### 2. Features and benefits

- Up to 18 V operating range, 21 V absolute maximum

- Integrated 17 mΩ pass MOSFET

- 15 V output voltage clamp

- 2 A to 13.5 A adjustable output current clamp

- · 2 µs short circuit protection response time

- Programmable output rise time control

- Built-In thermal shutdown with fault alert pin

- · Fault response options: latch-off, auto-retry

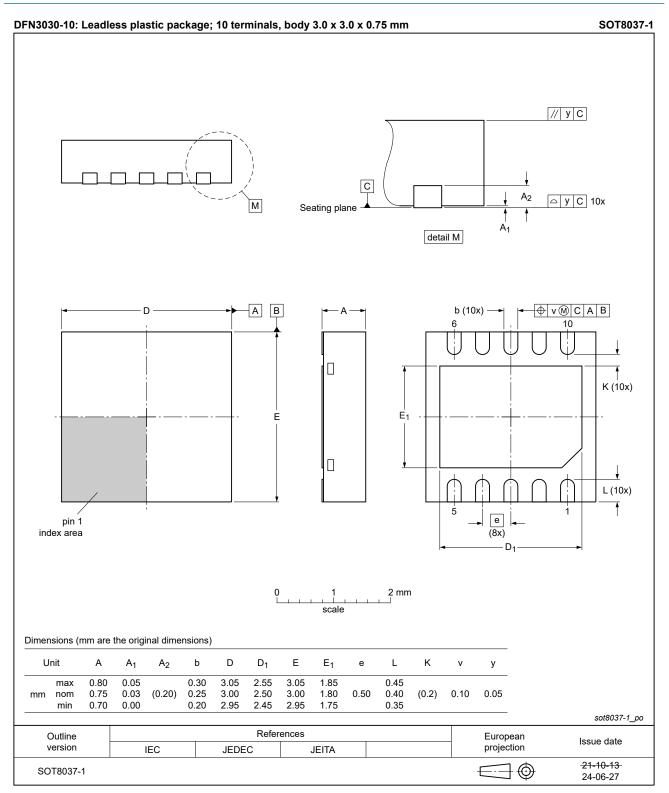

- Leadless plastic package; 10 terminals, body 3.0 x 3.0 x 0.75 mm (DFN3030-10/SOT8037-1)

- ESD protection:

- HBM ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V

- CDM ANSI/ESDA/JEDEC JS-002 class C3

exceeds 1000 V

- Specified from T<sub>i</sub> = -40 °C to +125 °C

### 3. Applications

- Server

- Solid State Drive (SSD) and Hard Disk Drive (HDD)

nexperia

- Mobile infrastructure

- Fan control

- Hot-Swap/Plug

## 4. Ordering information

| Table 1. Ordering information |                   |            |                                                                     |                  |

|-------------------------------|-------------------|------------|---------------------------------------------------------------------|------------------|

| Type number                   | Package           |            |                                                                     |                  |

|                               | Temperature range | Name       | Description                                                         | Version          |

| NPS3102AGB<br>NPS3102BGB      | -40 °C to +125 °C | DFN3030-10 | leadless plastic package; 10 terminals;<br>body 3.0 × 3.0 × 0.75 mm | <u>SOT8037-1</u> |

### 5. Marking

| Table 2. Marking codes |              |  |  |

|------------------------|--------------|--|--|

| Type number            | Marking code |  |  |

| NPS3102AGB             | s2A          |  |  |

| NPS3102BGB             | s2B          |  |  |

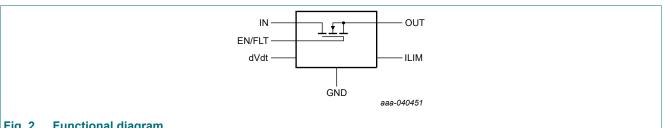

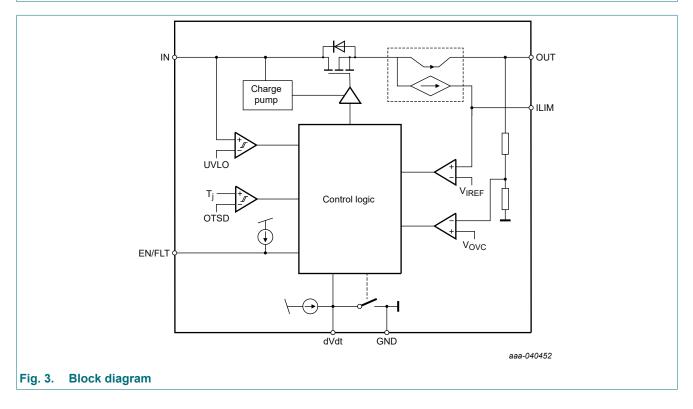

## 6. Block diagram

#### Fig. 2. **Functional diagram**

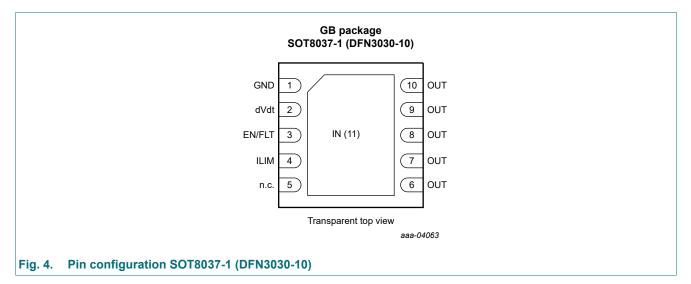

### 7. Pinning information

### 7.1. Pinning

### 7.2. Pin description

#### Table 3. Pin description

| Symbol | Pin            | Description                                                                                                                                                                                                                                                                                                                                        |

|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | 1              | Ground (0 V)                                                                                                                                                                                                                                                                                                                                       |

| dVdt   | 2              | Controls the output voltage rise time once the device has been enabled. Rise times are proportional to the value of the capacitor at this pin. A minimum of 4.7 nF is recommended at this pin. Do not actively drive this pin.                                                                                                                     |

| EN/FLT | 3              | A 3-state, bidirectional interface that serves to enable/disable the output, and alert monitoring circuits when the eFuse enters or exits thermal shutdown. Do not actively drive this pin to any voltage except for GND. Use an open-drain or open-collector pull-down component to set the EN/FLT logic. See <u>Section 13</u> for more details. |

| ILIM   | 4              | Current limit configuration. Connect a resistor between this pin and GND to set the current limit.<br>The voltage at this pin can be monitored for real-time load current information.                                                                                                                                                             |

| n.c.   | 5              | Not connected. Do not connect this pin to a trace on the PCB.                                                                                                                                                                                                                                                                                      |

| OUT    | 6, 7, 8, 9, 10 | Output voltage of the device, connected to the downstream loads.                                                                                                                                                                                                                                                                                   |

| IN     | 11             | Positive input supply voltage to the device.                                                                                                                                                                                                                                                                                                       |

ent feedb

### 8. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                  | Conditions | Min                | Тур | Max                   | Unit |

|---------------------|----------------------------|------------|--------------------|-----|-----------------------|------|

| V <sub>IN</sub>     | input voltage pin IN       |            | -0.3               | -   | 21                    | V    |

| V <sub>OUT</sub>    | output voltage pin<br>OUT  |            | -0.3               | -   | V <sub>IN</sub> + 0.3 | V    |

| V <sub>EN/FLT</sub> | EN/FLT pin voltage         |            | -0.3               | -   | 3                     | V    |

| V <sub>dVdt</sub>   | dVdt pin voltage           |            | -0.3               | -   | 3                     | V    |

| V <sub>ILIM</sub>   | ILIM pin voltage           |            | -0.3               | -   | V <sub>IN</sub>       | V    |

| I <sub>OUT</sub>    | continuous load<br>current |            | internally limited |     |                       | A    |

| Tj                  | junction temperature       |            | -40                |     | Internally<br>Limited | °C   |

| T <sub>stg</sub>    | storage temperature        |            | -65                |     | 150                   | °C   |

### 9. ESD ratings

### Table 5. ESD ratings

| Symbol           | Parameter         | Conditions                          | Min   | Тур | Max  | Unit |

|------------------|-------------------|-------------------------------------|-------|-----|------|------|

| V <sub>ESD</sub> | electrostatic     | HBM ANSI/ESDA/JEDEC JS-001 class 2  | -2000 | -   | 2000 | V    |

|                  | discharge voltage | CDM ANSI/ESDA/JEDEC JS-002 class C3 | -1000 | -   | 1000 | V    |

## **10. Recommended operating conditions**

### Table 6. Operating conditions

| Symbol            | Parameter                                        | Conditions | Min | Тур | Max  | Unit |

|-------------------|--------------------------------------------------|------------|-----|-----|------|------|

| V <sub>IN</sub>   | input voltage pin IN                             |            | 9   | -   | 18   | V    |

| R <sub>LIM</sub>  | external resistor at pin ILIM                    |            | 226 | -   | 1870 | Ω    |

| V <sub>dvdt</sub> | voltage rating of external capacitor at dVdt pin |            | 6.3 | -   | -    | V    |

| C <sub>dvdt</sub> | capacitance at dVdt pin                          |            | 4.7 | -   | -    | nF   |

| Tj                | junction temperature                             |            | -40 | -   | 125  | °C   |

## **11. Thermal characteristics**

#### Table 7. Thermal characteristics

| Symbol           | Parameter                                  | Conditions                              | Min | Тур | Мах | Unit |

|------------------|--------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R <sub>θja</sub> | junction to ambient thermal resistance     | As per JEDEC JESD51-7                   | -   | 62  | -   | °C/W |

|                  |                                            | 4 layers, 1oz copper,<br>4 thermal vias | -   | 38  | -   | °C/W |

| $\Psi_{JT}$      | junction to top characterization parameter |                                         | -   | 3.7 | -   | °C/W |

ment feedback

## 12. Electrical characteristics

#### **Table 8. Electrical characteristics**

At recommended operating conditions; voltages are referenced to GND (ground = 0 V)  $V_{IN} = 12$  V, EN/FLT = open,  $C_{dV/dt} = open$ ,  $R_{LIM} = 604 \Omega$ ,  $R_L = open$ ,  $C_{IN} = 0.1 \mu F$ ,  $C_L = 0.1 \mu F$ , unless otherwise stated.

| Symbol                    |     | Parameter                                                        | Conditions                                                                            | T <sub>j</sub> = -40 °C to 125 °C |        |      | Unit |

|---------------------------|-----|------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------|--------|------|------|

|                           |     |                                                                  |                                                                                       | Min                               | Typ[1] | Max  |      |

| Power consu               | mp  | tion                                                             |                                                                                       |                                   |        |      |      |

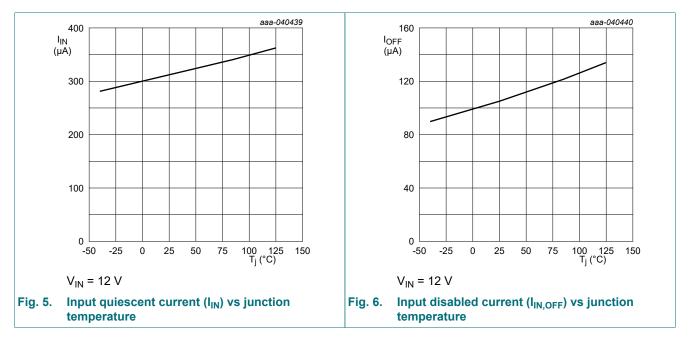

| I <sub>IN</sub>           |     | quiescent current                                                |                                                                                       | -                                 | 320    | 500  | μA   |

| I <sub>OFF</sub>          |     | OFF-state (disabled) current                                     | EN/FLT = GND                                                                          | -                                 | 100    | 200  | μA   |

| I <sub>TSD</sub>          | [2] | thermal shutdown current                                         | T <sub>j</sub> = T <sub>SD</sub> ;<br>EN/FLT is driven to V <sub>FAULT</sub> by eFuse | -                                 | -      | 1000 | μA   |

| Undervoltage              | lo  | ckout                                                            |                                                                                       |                                   |        |      |      |

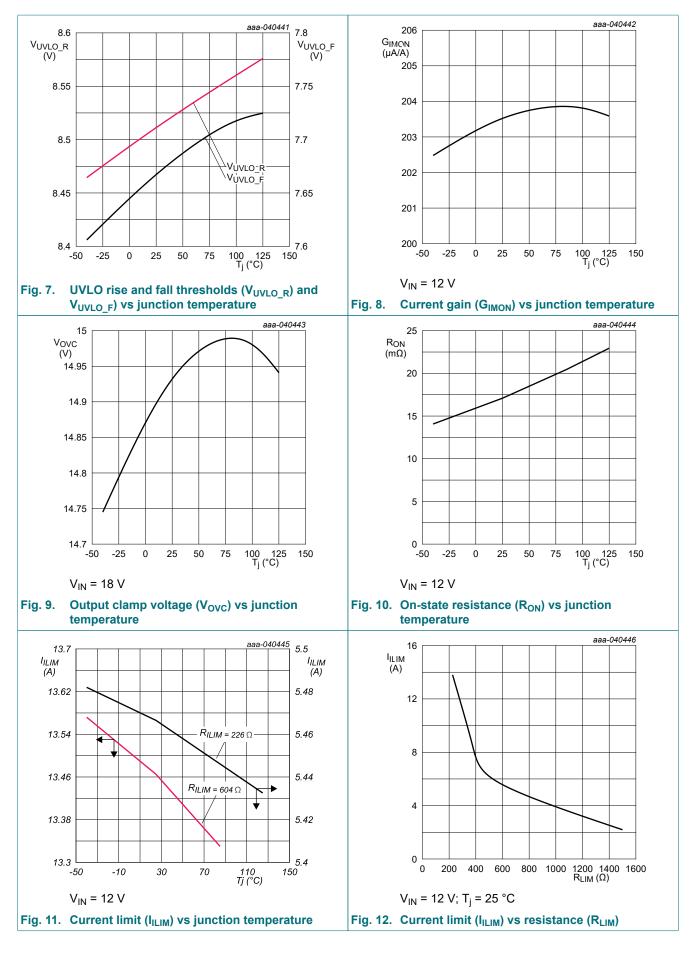

| V <sub>UVLO_R</sub>       |     | undervoltage lockout<br>rising threshold                         | EN/FLT changes from $V_{\text{EN}\_\text{UVLO}}$ to $V_{\text{IPU}}$                  | 7.8                               | 8.4    | 8.9  | V    |

| V <sub>UVLO_F</sub>       |     | undervoltage lockout<br>falling threshold                        | EN/FLT changes from $V_{\text{IPU}}$ to $V_{\text{EN}\_\text{UVLO}}$                  | 7.0                               | 7.6    | 8.1  | V    |

| V <sub>UVLO_HYS</sub>     |     | undervoltage lockout<br>hysteresis                               |                                                                                       | -                                 | 0.8    | -    | V    |

| Overvoltage a             | and | overcurrent protection                                           |                                                                                       |                                   |        |      |      |

| V <sub>OVC</sub>          |     | output voltage clamp                                             | V <sub>CC</sub> = 18 V; R <sub>L</sub> = 100 Ω;                                       | 13.5                              | 15     | 16   | V    |

| I <sub>ILIM</sub>         | [2] | output hold/limit current                                        | $R_{LIM}$ = 226 $\Omega$ ; $V_{IN}$ - $V_{OUT}$ = 0.5 V                               | 12.4                              | 13.8   | 15.1 | A    |

|                           |     |                                                                  | R <sub>LIM</sub> = 604 Ω; V <sub>IN</sub> - V <sub>OUT</sub> = 0.5 V                  | 5                                 | 5.55   | 6.1  | А    |

| I <sub>ILIM_R_OPEN</sub>  |     | output hold/limit current -<br>open ILIM                         | R <sub>LIM</sub> = Open                                                               | -                                 | 0      | -    | A    |

| I <sub>ILIM_R_SHORT</sub> | [2] | output hold/limit current -<br>short ILIM                        | R <sub>LIM</sub> = 0 Ω                                                                | -                                 | 20     | 24   | A    |

| G <sub>IMON</sub>         |     | current monitor gain                                             | I <sub>ILIM</sub> / I <sub>OUT</sub>                                                  | 184                               | 203    | 216  | μA/A |

| Power MOSF                | ET  |                                                                  |                                                                                       |                                   |        |      |      |

| R <sub>ON</sub>           |     | ON-state resistance                                              |                                                                                       | -                                 | 17     | 30   | mΩ   |

| I <sub>LKG</sub>          |     | leakage current (from IN to                                      | EN/FLT = GND; R <sub>L</sub> = 10 kΩ; T <sub>j</sub> = 25 °C                          | -                                 | 0.1    | 6    | μA   |

|                           |     | OUT)                                                             | EN/FLT = GND; R <sub>L</sub> = 10 kΩ;<br>T <sub>j</sub> = -40 °C to +85 °C            | -                                 | -      | 30   |      |

|                           |     |                                                                  | EN/FLT = GND; R <sub>L</sub> = 10 kΩ;<br>T <sub>j</sub> = -40 °C to +125 °C           | -                                 | -      | 100  |      |

| <b>Bi-directional</b>     | en  | able and fault functionality                                     |                                                                                       |                                   |        |      |      |

| V <sub>IL</sub>           |     | input voltage to reset eFuse                                     | EN/FLT pin pulled low externally                                                      | -                                 | -      | 0.4  | V    |

| V <sub>IPU</sub>          |     | EN/FLT voltage in normal operation                               | EN/FLT pin voltage set by NPS3102                                                     | 2.2                               | 2.35   | 2.5  | V    |

| V <sub>FAULT</sub>        |     | EN/FLT voltage due to thermal shutdown                           | EN/FLT pin voltage set by NPS3102                                                     | 0.7                               | 0.9    | 1.1  | V    |

| V <sub>EN_UVLO</sub>      |     | EN/FLT voltage when<br>V <sub>IN</sub> < V <sub>UVLO_F</sub>     | EN/FLT pin voltage set by NPS3102                                                     | -                                 | -      | 0.3  | V    |

| IIL                       |     | current sourced out of<br>EN/FLT pin when in thermal<br>shutdown |                                                                                       | -                                 | 17     | 25   | μA   |

| N                         | [2] | fault signal fanout                                              | number of devices that can be paralleled                                              | -                                 | -      | 3    | -    |

### 12 V, 2 A to 13.5 A, 17 mΩ eFuse

| Symbol               | Parameter                      | Conditions             | T <sub>j</sub> = -4 | 10 °C to 1 | 25 °C | Unit |

|----------------------|--------------------------------|------------------------|---------------------|------------|-------|------|

|                      |                                |                        | Min                 | Typ[1]     | Мах   |      |

| Thermal shutdo       | wn                             |                        |                     |            |       |      |

| T <sub>SD</sub> [2   | termal shutdown<br>temperature | rising T <sub>j</sub>  | 150                 | 185        | 200   | °C   |

| T <sub>HYST</sub> [2 | temperature hysteresis         | falling T <sub>j</sub> | -                   | 30         | -     | °C   |

[1] Typical values are measured at T<sub>j</sub> = 25 °C.

[2] Not production tested. Guaranteed by Design and/or Characterization.

#### Table 9. Dynamic characteristics

$V_{CC}$  = 12 V, EN/FLT = open,  $C_{dV/dt}$  = open,  $R_{LIM}$  = 604  $\Omega$ ,  $R_L$  = open,  $C_{IN}$  = 0.1  $\mu$ F,  $C_L$  = 0.1  $\mu$ F, unless otherwise stated.

| Symbol               | Parameter                               | Conditions                                                                                        | Т <sub>ј</sub> = - | Unit |     |      |

|----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|------|-----|------|

|                      |                                         |                                                                                                   | Min                | Тур  | Max |      |

| t <sub>ONDLY</sub>   | EN on delay time                        | $V_{ENFLT}$ = $V_{IPU}$ to $V_{OUT}$ = 10% of $V_{IN}$ ;<br>$C_{OUT}$ = 10 µF                     | -                  | 170  | -   | μs   |

| t <sub>OFFDLY</sub>  | EN off delay time                       | $V_{\text{ENFLT}}$ < V_{IL} to V_{\text{OUT}}=90% of V_IN; C_{OUT} = 10 $\mu\text{F}$             | -                  | 18   | -   | μs   |

| SR                   | output slew rate                        | C <sub>dvdt</sub> =10 nF; C <sub>OUT</sub> = 10 μF                                                | -                  | 3.3  | -   | V/ms |

|                      |                                         | C <sub>dvdt</sub> =33 nF; C <sub>OUT</sub> = 10 μF                                                | -                  | 1    | -   | V/ms |

| t <sub>ovc</sub>     | output voltage clamp<br>response time   | $V_{\text{IN}}$ rises above $V_{\text{OVC}}$ to peak $V_{\text{OUT}};R_{\text{L}}$ = 100 $\Omega$ | -                  | 5    | -   | μs   |

| t <sub>ILIM</sub>    | output current clamp response time      | $I_{OUT}$ > $I_{LIM}$ + 20% to $I_{OUT}$ within 5% of $I_{ILIM};$ $R_L$ = 1.5 $\Omega$            | -                  | 20   | -   | μs   |

| t <sub>SC</sub>      | output short circuit response time      | $I_{OUT}$ > $I_{LIM}$ + 20% to $I_{OUT}$ peak; $R_L$ = 0.1 $\Omega$                               | -                  | 2    | -   | μs   |

| t <sub>TSD_ARI</sub> | thermal shutdown<br>auto-retry interval | $\frac{NPS3102B}{T_j} = T_{SD} - T_{HYST}$                                                        | -                  | 1    | 2   | ms   |

### 12.1. Typical characteristics graphs

#### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2024. All rights reserved

### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

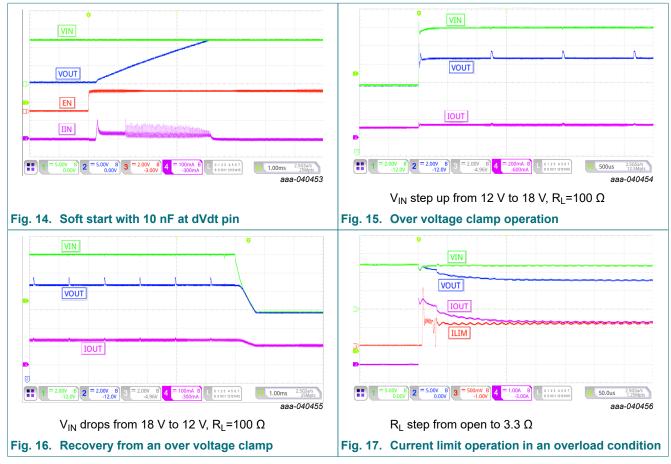

### 12.2. Typical waveforms

$V_{IN}$  = 12 V, EN/FLT = open,  $C_{dV/dt}$  = 10 nF,  $R_{LIM}$  = 1.5 k $\Omega$ ,  $R_L$  = open,  $C_{IN}$  = 10  $\mu$ F,  $C_L$  = 10  $\mu$ F,  $T_j$  = 25 °C unless otherwise stated.

NPS3102

12 V, 2 A to 13.5 A, 17 m $\Omega$  eFuse

## **13. Feature description**

### **Basic operation**

NPS3102 is an electronic fuse device, integrating a low ohmic pass FET along with several system protection features to ensure safe power delivery to a downstream load.

NPS3102 starts its operation by monitoring the voltage on its IN pin and its EN/FLT pin. Once the pin voltages cross their respective thresholds ( $V_{UVLO_R}$  and  $V_{IPU}$ ), NPS3102 will enable the pass FET, delivering power to the load that is connected to the OUT pins. The power ramp is regulated by the configuration of the dVdt pin.

In normal operation, NPS3102 monitors the load current and input voltage, using both characteristics to regulate the pass FET configuration. If the load current crosses the programmed over-current limit threshold ( $I_{ILIM}$ ) or if the load voltage crosses the over-voltage limit threshold ( $V_{OVC}$ ), the device will reduce the conductivity of the pass FET to restrict load current and voltage to the respective threshold values. NPS3102 has a built-in mechanism to provide a rapid protection response to rapid over-current events (i.e., short-circuit).

NPS3102 also integrates a junction temperature monitoring block that will disconnect power delivery before the junction temperature rises to a point where it would be permanently damage the device.

#### Start-up

NPS3102 starts up when the input voltage  $V_{IN}$  exceeds the rising under-voltage lockout threshold ( $V_{UVLO_R}$ ) and the voltage at the EN/FLT pin reaches  $V_{IPU}$ . Both  $V_{IN}$  and  $V_{EN/FLT}$  are continuously monitored. If the input voltage falls below  $V_{UVLO_F}$  or if the EN/FLT pin voltage drops below  $V_{IL}$ , the device turns off.

### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

#### Soft start

Once the device starts up, the device starts charging the output capacitor at a slew rate determined by the capacitor connected at the dVdt pin. There are a few modes of operation during the soft start period.

- While the EN/FLT pin is held low, the internal charge pump is turned off.

- When the EN/FLT pin exceeds V<sub>IPU</sub>, the internal charge pump is turned on in a low power mode. This mode lasts for approximately 1 ms. This mode is intended to act as a fail-safe to limit the output slew rate in case there is insufficient capacitance at the dVdt pin.

- After the 1 ms time, the charge pump is switched to a high power mode.

Once the charge pump shifts to the high power mode, the device uses an internal resistor divider to step down the output voltage and compares this voltage to the voltage at the dVdt pin.

- If the slew rate of the output voltage is less than the slew rate of the dVdt pin voltage, the charge pump is turned on in the strong mode.

- If the slew rate of the output voltage is more than the slew rate of the dVdt pin voltage, the charge pump is turned off.

Thus, by turning the charge pump off and off, the device regulates the output slew rate to match the slew rate of the dVdt pin.

The capacitor that is required at the dVdt pin can be computed based on the rise time desired for the output voltage.

$$C_{dVdt} = (3.4 \times 10^{-6}) \times t_R$$

where  $C_{dVdt}$  is the capacitor at the dVdt pin and  $t_R$  is the desired 10% - 90% rise time of the output voltage.

Fig. 14 shows the start-up waveform with a 10 µF load capacitor and a 10 nF capacitor at the dVdt pin.

Note that the maximum capacitor at dVdt pin is determined by the load capacitance.

$$C_{dVdt,max} = \frac{C_{OUT}}{60}$$

where  $C_{OUT}$  is the total output capacitance including those of any downstream loads. For example, a 10  $\mu$ F load capacitance leads to a maximum capacitance of 167 nF at the dVdt pin.

#### **Normal operation**

Once the device completes inrush, the pass FET is completely turned on to achieve a low on-state resistance. The device constantly monitors the output voltage and the current through the device.

#### Output over-voltage clamp

The over-voltage protection in the NPS3102 is designed to be fast acting and consume low power in normal operation. When the NPS3102 is enabled, the over-voltage comparator continuously monitors the OUT pin voltage. Once the OUT pin voltage rises above the threshold value  $V_{OVC}$ , the internal over-voltage comparator quickly turns off the pass-FET and clamps its gate voltage.

As the output voltage droops due to the load, the IC detects that the output is lower than the clamp voltage. At this point, the device releases the over-voltage circuitry and turns on the pass-FET. This causes the output to rise and detect over voltage (if the input is still above the over voltage limit) and restarts the clamp circuit.

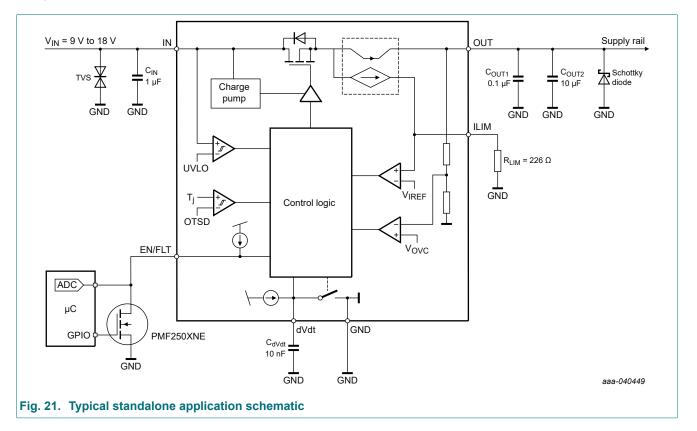

Activation of the over-voltage clamp elevates the power dissipation of the pass FET due to the increased voltage difference between the IN and OUT pins. This increased power dissipation will also elevate the NPS3102 junction temperature, depending on the load current. A prolonged over-voltage condition can increase the junction temperature high enough to trigger a thermal shutdown (see <u>Thermal shutdown protection</u>).

Fig. 15 shows the device entering over voltage protection with a 100 mA load. When the input voltage jumps from 12 V to 18V, the output voltage clamps to 15 V. The short spikes seen in the output voltage are due to the periodic release of the over voltage circuitry as described. Fig. 16 shows the recovery of the part when the input over voltage condition disappears. In both cases, there is no disruption to the load.

#### Current monitoring and over current protection

During normal operation, the device constantly monitors the output current ( $I_{OUT}$ ). The current is mirrored and sourced out of the ILIM pin. The ratio of the current sourced out of the ILIM pin and the current through the pass FET is  $G_{IMON}$ . A resistor to ground at ILIM pin ( $R_{LIM}$ ) converts this current into a voltage ( $V_{ILIM}$ ), which can be used a real time measurement of the load current.

$$I_{OUT} = \frac{V_{ILIM}}{G_{IMON} \times R_{LIM}}$$

$R_{LIM}$  is chosen to program the over current limit ( $I_{ILIM}$ ).

$$R_{LIM} = \frac{0.63V}{G_{IMON} \times I_{LIM}}$$

When the load current exceeds the programmed I<sub>ILIM</sub> value, the device limits the current to I<sub>ILIM</sub>. This is done in a hysteretic manner by turning the pass FET on and off. The FET turn off is done quickly to ensure no large over current conditions occur, whereas the FET turn-on is controlled so that the hysteresis frequency does not become too large. The device remains in this mode until the overload condition resolves or the device hits its over temperature shut down limit (see <u>Thermal shutdown protection</u>).

<u>Fig. 17</u> shows the behavior of the device to an over current event. In this case,  $R_{LIM}$  is set to 1.5 k $\Omega$ , which is about a 2 A current limit. When a 3 A over current event occurs, the device limits the output current to the programmed value. This also causes the output voltage drop and increases the power dissipation in the device (in this case, to approximately 8 W).

The NPS3102 is protected against ILIM pin open or short to ground conditions. If the ILIM pin is left open, the device will not allow any current to pass. If ILIM pin is shorted to ground, then the over current limit is set to 22 A internally. In either case, the device will not get damaged.

### Short circuit protection

When the output of the NPS3102 is shorted to ground, the current through the device increases rapidly. Short circuit protection comparator is activated when the voltage at ILIM pin exceeds 1.2 V. At this point, the device pulls down the gate of the NFET rapidly to prevent high peak currents and limit the output current to the programmed value.

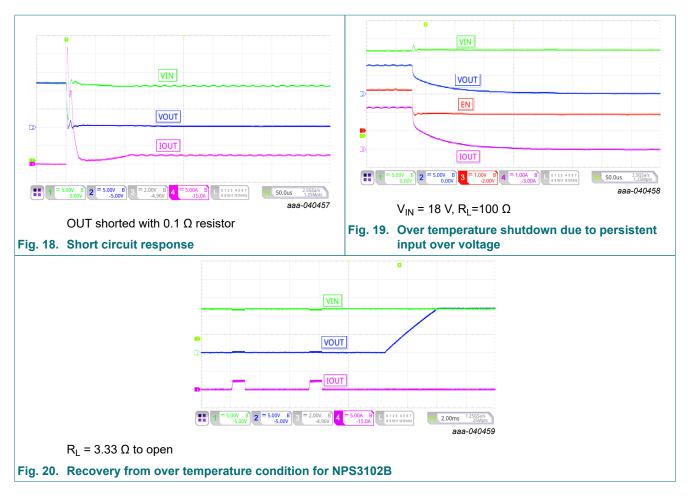

<u>Fig. 18</u> shows the behavior of the device to a short circuit condition which is initiated by shorting the output with a 0.1  $\Omega$  load. The device reduces the gate voltage to the FET within 2 µs, which causes the load current to drop. Once the load current drops to a safe value, the output current limit circuit is engaged.

### **Bi-directional enable/fault functionality**

The EN/FLT pin is a bi-directional I/O. The pin has a weak pull-up internal to the device. This pin can be used to control the device, monitor the status of the device, and connect multiple devices in parallel.

To use this pin as a control input, connect it to an open-drain FET or a GPIO pin of a micro-controller configured as an opendrain output. Pulling the pin down to GND (less than  $V_{IL}$ ) turns off the NPS3102. Turning off the pull-down FET turns on the NPS3102.

The pin can be used as a status pin by monitoring the voltage at the pin.

Low level (VIL) - A voltage below this level indicates NPS3102 has been turned off.

Mid level (V<sub>FAULT</sub>) – A voltage within this range indicates NPS3102 is in Thermal Shutdown.

High level ( $V_{IPU}$ ) – A voltage above this level indicates NPS3102 has been turned ON.

In cases where multiple NPS3102s are used in parallel, the EN/FLT pins of all the ICs need to be connected together to ensure proper operation. NPS3102 is designed to allow up to 3 devices to be connected in parallel (see <u>Paralleling eFuses</u>).

#### Thermal shutdown protection

The NPS3102 has internal SOA management to prevent an elevated junction temperature  $(T_j)$  from permanently damaging the pass FET. In normal operation, the NPS3102 continuously monitors its internal junction temperature. If it crosses the over temperature threshold  $(T_{SD})$ , the pass FET is disabled and the load is disconnected. The EN/FLT pin will be driven internally to V<sub>FAULT</sub> while the NPS3102 remains in thermal shutdown (see <u>Bi-directional enable/fault functionality</u>).

#### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

In NPS3102A, there are two options to exit thermal shutdown and attempt to resume normal operation

- power cycle the IN pin, or

- toggle the EN/FLT pin.

Note that if  $T_i$  has not fallen below ( $T_{SD} - T_{HYST}$ ), NPS3102 will re-enter thermal shutdown.

If user-trigger to resume normal operation is not a viable option, then NPS3102B is recommended due to its auto-retry feature. This feature enables the NPS3102B to automatically resume normal operation once  $T_j$  has dropped to ( $T_{SD} - T_{HYST}$ ). Once  $T_j$  has sufficiently dropped, the device will wait for an additional delay of  $t_{TSD\_ARI}$ , and then attempt to reenable the pass FET. The pin voltage will return to  $V_{IPU}$ .

- The junction temperature of the NPS3102 can exceed its internal limit TSD in a few scenarios.

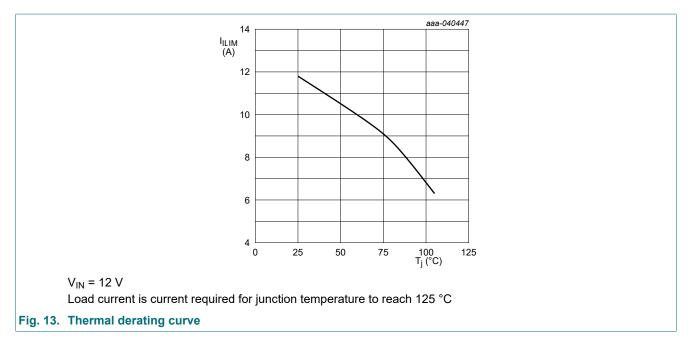

- The rms current through the device exceeds the maximum current in the temperature de-rating curve (see Fig. 13)

- The device is in over current protection mode causing excessive power dissipation

- The device is in the over voltage clamp mode with a load current causing excess power dissipation

- · Start-up with a large load capacitor which causes excessive power dissipation.

Behavior of the NPS3102 to an over temperature condition is shown in Fig. 19. In this case, a persistent over current condition causes the device to heat up and shut down. When the device shuts down, the EN/FLT pin is pulled to  $V_{FAULT}$  to indicate that the device is in thermal shutdown.

Fig. 20 shows the recovery of the NPS3102B device from a persistent overload condition. The device keeps trying to restart until both the over temperature condition and overload conditions disappear. At this point, the device enters soft start and ramps up the load capacitor.

## **14.** Application information

#### **Basic operation**

The NPS3102 is an electronic fuse intended to overcome the disadvantages of one shot fuses, PTC fuses or discrete protection circuits. It protects the downstream components against overvoltage and limits the maximum current flow during a fault ensuring maximal safety. With an input voltage range of 9 V to 18 V and a programmable current limit between 2 A and 13.5 A, it can be used in a broad range of applications where protection is needed.

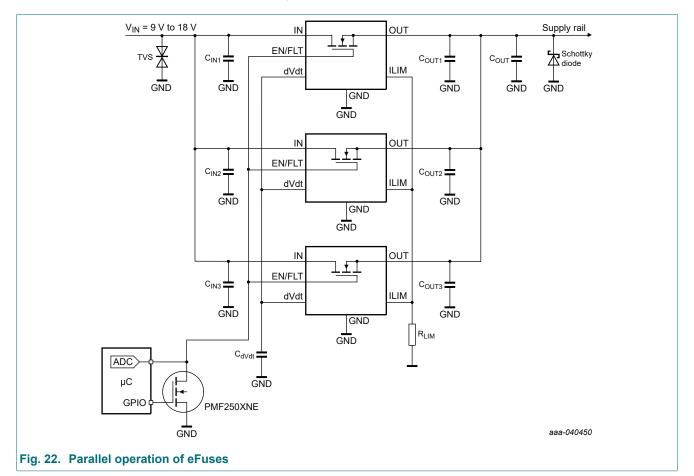

### **Typical standalone application**

Fig. 21 depicts a standard standalone application. This application is designed to limit the current to 13.5 A and an output voltage rise time of 3 ms.

The current limit threshold is controlled by the value of R<sub>LIM</sub> and can be calculated by:

$$R_{LIM} = \frac{0.63V}{G_{IMON} \times I_{LIM}} = \frac{0.63V}{203\frac{\mu A}{A} \times 13.5A} = 229\Omega$$

Rounded to an E96 resistor value this result in 226  $\Omega$ .

Both  $C_{IN}$  and  $C_{OUT}$  are needed for decoupling and transient suppression. The input transient voltage suppressor protects the eFuse against large voltage transients that might exceed the recommended voltage operating range during switching of load circuitry. These transients might occur due to parasitic inductance from the supply connection to the input of the eFuse. The Schottky diode on the output protects the eFuse from negative voltage transients. Both the TVS and the Schottky diode can be omitted, but for robustness, these are recommended.  $C_{dVdt}$  sets the output slew rate to 3 ms as per the equation below.

$$C_{dVdt} = (3.4 \times 10^{-6}) \times t_R = (3.4 \times 10^{-6}) \times 3ms = 10.2nF$$

Rounding the value to a standard value results in a 10 nF capacitor at dVdt pin. It is recommended to choose either a  $\geq$ 6.3 V rated NP0/C0G or a  $\geq$ 10 V rated X7R capacitor to minimize capacitance change due to DC bias. The minimum slew rate achievable is 1 ms, which occurs when the dVdt pin is left floating.

#### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

The bi-directional EN/FLT pin is used to disable the device using an open drain NMOS which in turn is controlled by a micro controller. During normal operation, the voltage of the EN/FLT pin can be monitored using an ADC to monitor fo fault situations. The voltage across R<sub>LIM</sub> can be used as a real time current monitor and can also be connected to an ADC. When using an analog switch both signals can be monitored sequentially.

If the input range of the ADC is lower than the maximum voltages at either EN/FLT or ILIM pins, the voltages need to be stepped down using external buffers. The pins are not capable of sourcing more than 1 µA to external circuitry.

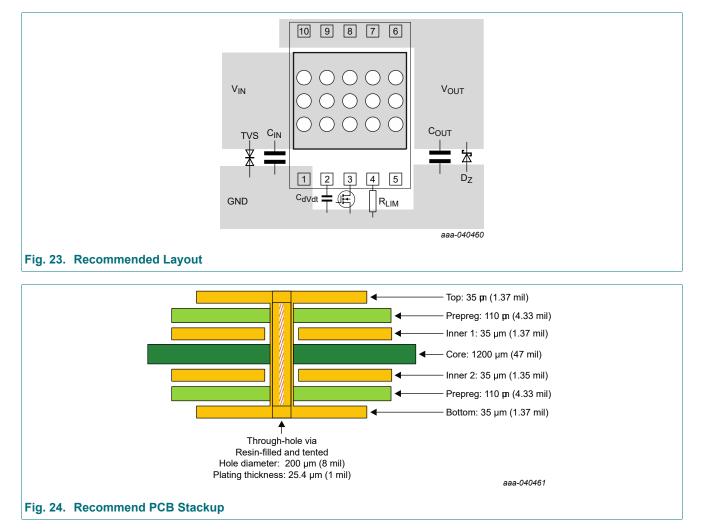

#### **Paralleling eFuses**

If the current rating of a single eFuse is insufficient, or if there is a need to distribute power dissipation across the PCB, it is possible to parallel a maximum of three eFuses. Fig. 22 illustrates the appropriate connection of these devices.

Several considerations must be taken into account:

- The current charging the dVdt capacitor will be three times the value of a single device, resulting in a ramp rate that is three times faster, if the capacitor is not adjusted accordingly.

- The current through the current-limiting resistor will be three times the value of a single device. Since the voltage across this resistor triggers the current-limiting circuit, it should be one-third of the value of a single device.

- EN/FLT pins should be tied together. In the event that one device enters thermal shutdown, the voltage on this pin will trigger the other eFuses to enter thermal shutdown as well.

- Each device should have its own decoupling capacitors at input and output pins.

- Careful attention must be paid to the layout. The distribution of current will significantly depend on the added series resistance, which should be equal for every eFuse. Failure to comply may result in variations in power dissipation per product, potentially leading to thermal shutdown of the system.

© Nexperia B.V. 2024. All rights reserved

### **PCB Layout**

<u>Fig. 23</u> depicts a proven layout example. Both  $C_{IN}$  and  $C_{OUT}$  should be as close as possible to the device to keep the inductivity of the current loop as low as possible. Transient protection devices can be placed next to these capacitors.

To prevent unwanted activation of the thermal protection, it is advised to connect as much as possible copper area to the exposed pad of the device using thermal via's in the pad distributing the dissipated power to the  $V_{CC}$  plane.

To optimize the thermal performance of the device, it is important to design the board stack-up and copper areas on each layer correctly. A stack-up example based on the NPS3102 evaluation module is shown in Fig. 24. The minimum copper areas connected to the thermal pad of the IC for each layer is listed in Table 10. Using this PCB stack-up and a similar layout, it is possible to achieve a junction to ambient thermal impedance of 33 °C/W.

#### Table 10. Recommended copper area in each layer

| Layer   | Minimum Copper area connected to thermal pad | Number of vias in thermal pad       |

|---------|----------------------------------------------|-------------------------------------|

| Тор     | 30 mm <sup>2</sup>                           | 15 vias arranged in a 5 x 3 pattern |

| Inner 1 | 100 mm <sup>2</sup>                          |                                     |

| Inner 2 | 20 mm <sup>2</sup>                           |                                     |

| Bottom  | 50 mm <sup>2</sup>                           |                                     |

### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

## 15. Package outline

#### Fig. 25. Package outline SOT8037-1 (DFN3030-10)

nt feed

## 16. Abbreviations

| Table 11. Abbre | Table 11. Abbreviations |  |  |  |  |

|-----------------|-------------------------|--|--|--|--|

| Acronym         | Description             |  |  |  |  |

| DUT             | Device Under Test       |  |  |  |  |

| ESD             | ElectroStatic Discharge |  |  |  |  |

| PCB             | Printed-Circuit Board   |  |  |  |  |

| TDB             | To Be Determined        |  |  |  |  |

## 17. Revision history

### Table 12. Revision history

| Data sheet ID | Release date | Data sheet status  | Change notice | Supersedes |

|---------------|--------------|--------------------|---------------|------------|

| NPS3102 v.1   | 20240718     | Product data sheet | -             | -          |

## 18. Legal information

#### Data sheet status

| Document status [1][2]            | Product<br>status [3] | Definition                                                                                  |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Objective [short]<br>data sheet   | Development           | This document contains data from<br>the objective specification for<br>product development. |

| Preliminary [short]<br>data sheet | Qualification         | This document contains data from the preliminary specification.                             |

| Product [short]<br>data sheet     | Production            | This document contains the product specification.                                           |

Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <u>https://www.nexperia.com</u>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

#### 12 V, 2 A to 13.5 A, 17 mΩ eFuse

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <u>http://www.nexperia.com/profile/terms</u>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

© Nexperia B.V. 2024. All rights reserved

### 12 V, 2 A to 13.5 A, 17 m $\Omega$ eFuse

## Contents

| 1.  | General description               | 1 |

|-----|-----------------------------------|---|

| 2.  | Features and benefits             | 1 |

| 3.  | Applications                      | 1 |

| 4.  | Ordering information              | 2 |

| 5.  | Marking                           | 2 |

| 6.  | Block diagram                     | 2 |

| 7.  | Pinning information               | 3 |

| 7.1 | . Pinning                         | 3 |

| 7.2 | Pin description                   | 3 |

| 8.  | Limiting values                   | 4 |

| 9.  | ESD ratings                       | 4 |

| 10. | Recommended operating conditions  | 4 |

| 11. | Thermal characteristics           | 4 |

| 12. | Electrical characteristics        | 5 |

| 12. | 1. Typical characteristics graphs | 6 |

| 12. | 2. Typical waveforms              | 8 |

| 13. | Feature description               | 9 |

| 14. | Application information1          | 3 |

| 15. | Package outline1                  | 6 |

| 16. | Abbreviations1                    | 7 |

| 17. | Revision history1                 | 7 |

| 18. | Legal information1                | 8 |

|     |                                   |   |

© Nexperia B.V. 2024. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 18 July 2024