# PolarFire SoC MSS Technical Reference Manual

#### Introduction (Ask a Question)

The PolarFire® SoC family offers the industry's first RISC-V based SoC FPGAs. The PolarFire SoC family combines a powerful 64-bit 5x core RISC-V Microprocessor Sub-System (MSS), based on SiFive's U54-MC family, with the PolarFire FPGA fabric in a single device. Packed with this powerful combination, PolarFire SoC devices offer the scalable features of FPGAs and high-performance of ASICs. Only the FPGA fabric resources vary and the MSS remains the same across PolarFire SoC device variants, making these devices ideal for a variety of applications. PolarFire SoC FPGAs are ideal for running full-fledged Operating Systems (like Linux®) using MSS.

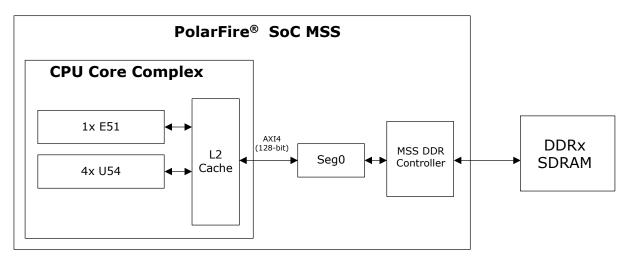

This manual covers the PolarFire SoC MSS architecture and its functional blocks—the CPU Core Complex, AXI Switch, MSS peripherals, Fabric interfaces, and MSS DDR controller. For information about configuring MSS, see Standalone MSS Configurator User Guide for PolarFire SoC. For information about PolarFire SoC software development and tool flow, and MSS booting, see PolarFire SoC Software Development and Tool Flow User Guide.

**Important:** The AXI protocol standard uses the terminology "Master" and "Slave". The equivalent Microchip terminology is "Initiator" and "Target", respectively.

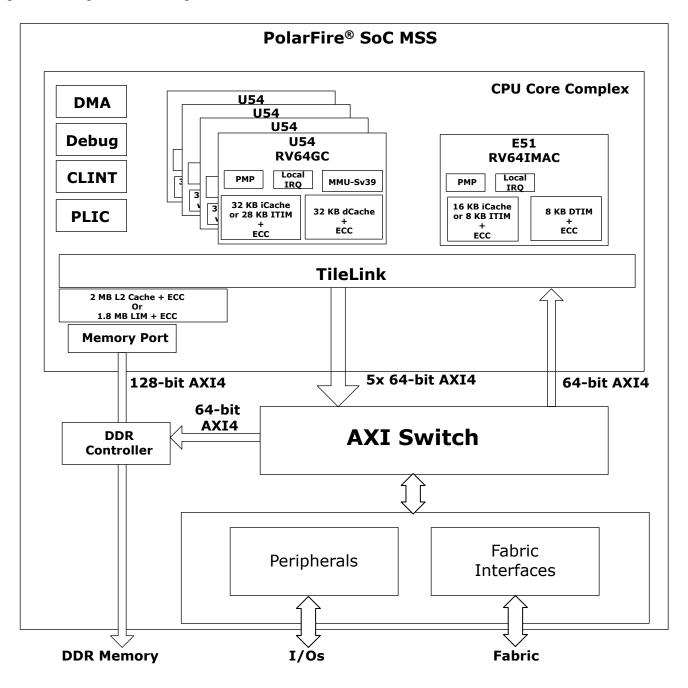

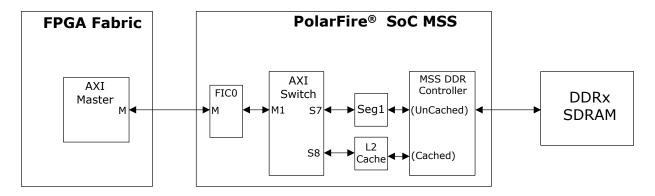

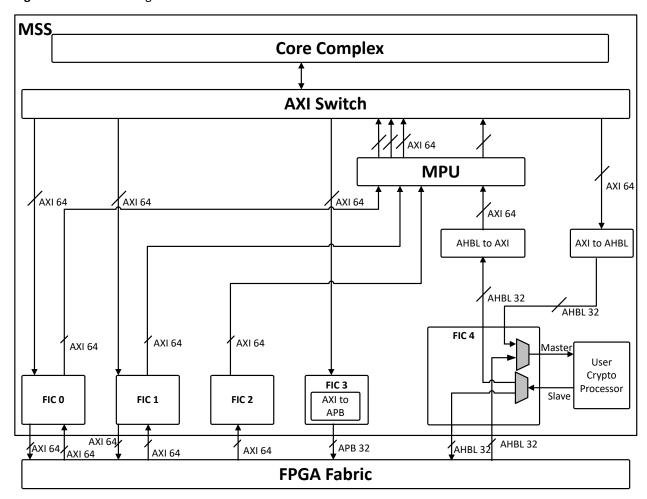

The following figure shows the MSS block at a high-level. For more details, see Figure 2-1.

Figure 1. MSS High-Level Block Diagram

**Important:** As shown in the preceding figure, TileLink is used for memory coherence in the CPU Core Complex. TileLink is also referred as "Coherent Switch" in other documents.

# References (Ask a Question)

- For information about MSS simulation, see MSS Simulation User Guide for PolarFire SoC.

- For information about configuring MSS and its peripherals, see Standalone MSS Configurator User Guide for PolarFire SoC.

- For information about PolarFire SoC software development and tool flow, see PolarFire SoC Software Development and Tool Flow User Guide.

- For information about PolarFire SoC baremetal and Linux sample projects, see PolarFire SoC GitHub.

- For information about MSS power-up, see PolarFire Family Power-Up and Resets User Guide.

- For information about Embedded software development, see SoftConsole User Guide (to be published).

- For information about other PolarFire SoC FPGA features, see the PolarFire SoC Documentation web page.

# **Table of Contents**

| Intr | roduction                                      | 1   |  |  |  |

|------|------------------------------------------------|-----|--|--|--|

| Ref  | ferences                                       | 2   |  |  |  |

| 1.   | PolarFire SoC MSS Features                     | 6   |  |  |  |

| 2.   | Detailed Block Diagram                         | 7   |  |  |  |

| 3.   | Functional Blocks                              | 9   |  |  |  |

|      | 3.1. CPU Core Complex                          |     |  |  |  |

|      | 3.2. AXI Switch                                |     |  |  |  |

|      | 3.3. Fabric Interface Controllers (FICs)       |     |  |  |  |

|      | 3.4. Memory Protection Unit                    |     |  |  |  |

|      | 3.5. Segmentation Blocks                       |     |  |  |  |

|      | 3.6. AXI-to-AHB                                |     |  |  |  |

|      | 3.7. AHB-to-APB                                | 46  |  |  |  |

|      | 3.8. Asymmetric Multi-Processing (AMP) APB Bus | 47  |  |  |  |

|      | 3.9. MSS I/Os                                  | 48  |  |  |  |

|      | 3.10. User Crypto Processor                    | 48  |  |  |  |

|      | 3.11. MSS DDR Memory Controller                | 48  |  |  |  |

|      | 3.12. Peripherals                              | 58  |  |  |  |

| 4.   | System Registers                               | 107 |  |  |  |

| 5.   | Interrupts                                     | 108 |  |  |  |

|      | 5.1. Interrupt CSRs                            | 112 |  |  |  |

|      | 5.2. Supervisor Mode Interrupts                | 115 |  |  |  |

|      | 5.3. Interrupt Priorities                      | 118 |  |  |  |

|      | 5.4. Interrupt Latency                         | 119 |  |  |  |

|      | 5.5. Platform Level Interrupt Controller       | 119 |  |  |  |

|      | 5.6. Core Local Interrupt Controller           | 124 |  |  |  |

| 6.   | Fabric Interface Controller                    | 125 |  |  |  |

|      | 6.1. Overview                                  | 125 |  |  |  |

|      | 6.2. FIC Reset                                 | 126 |  |  |  |

|      | 6.3. Timing Diagrams                           | 126 |  |  |  |

|      | 6.4. Configuring FICs                          | 127 |  |  |  |

| 7.   | Boot Process                                   | 128 |  |  |  |

|      | 7.1. Boot Modes Fundamentals                   | 128 |  |  |  |

| 8.   | Resets                                         | 138 |  |  |  |

| 9.   | Clocking                                       | 139 |  |  |  |

| 10.  | MSS Memory Map                                 | 140 |  |  |  |

| 11.  | Appendix A: Acronyms                           | 143 |  |  |  |

| 12   | Revision History                               |     |  |  |  |

|      |                                                |     |  |  |  |

| Microchip FPGA Support                    | 150 |

|-------------------------------------------|-----|

|                                           |     |

| Microchip Information                     | 150 |

| The Microchip Website                     | 150 |

| Product Change Notification Service       | 150 |

| Customer Support                          |     |

| Microchip Devices Code Protection Feature | 150 |

| Legal Notice                              | 151 |

| Trademarks                                | 151 |

| Quality Management System                 | 152 |

| Worldwide Sales and Service               | 153 |

# 1. PolarFire SoC MSS Features (Ask a Question)

The following table lists the features of PolarFire SoC MSS.

Table 1-1. MSS Features

| Feature                                       | Description                                                                                                                                                                                                                       |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3.1.1. E51 RISC-V Monitor Core (1x)           | RV64IMAC, 625 MHz, 16 KB L1 iCache or 8 KB ITIM, and 8 KB DTIM. Machine (M) and User (U) modes                                                                                                                                    |  |

| 3.1.2. U54 RISC-V Application Cores (4x)      | RV64GC <sup>1</sup> , 625 MHz, 32 KB L1 iCache or 28 KB ITIM. 32 KB dCache, Sv39 MMU, M, Supervisor (S), and U modes                                                                                                              |  |

| 3.1.5. L2 Cache                               | 2 MB L2 cache or 1.875 MB LIM with ECC                                                                                                                                                                                            |  |

| BootFlash                                     | 128 KB eNVM                                                                                                                                                                                                                       |  |

| 3.1.4. Physical Memory Protection             | PMP block per processor core with 16x regions with a granularity of 4 bytes                                                                                                                                                       |  |

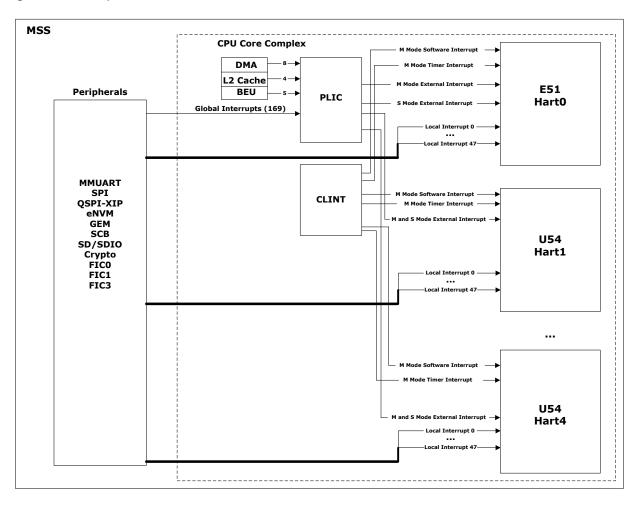

| 5. Interrupts                                 | 48 local interrupts per processor core (M and S mode)<br>169 external interrupts (platform level) (M and S mode)<br>Software and Timer local interrupt per processor core (M mode)                                                |  |

| 3.1.10. DMA Engine                            | 4x independent DMA channels                                                                                                                                                                                                       |  |

| 3.1.12. Bus Error Unit (BEU)                  | BEU per processor core for L1 iCache/dCache ECC and TileLink bus errors                                                                                                                                                           |  |

| 3.1.1.5. Hardware Performance Monitor         | Performance monitoring CSRs per processor core                                                                                                                                                                                    |  |

| 3.1.8. TileLink                               | TileLink B64 and D128 switch for I/O and memory coherency                                                                                                                                                                         |  |

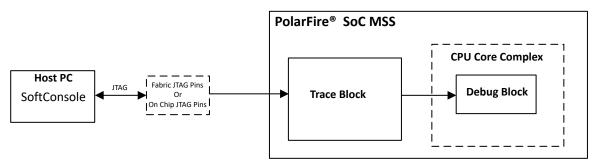

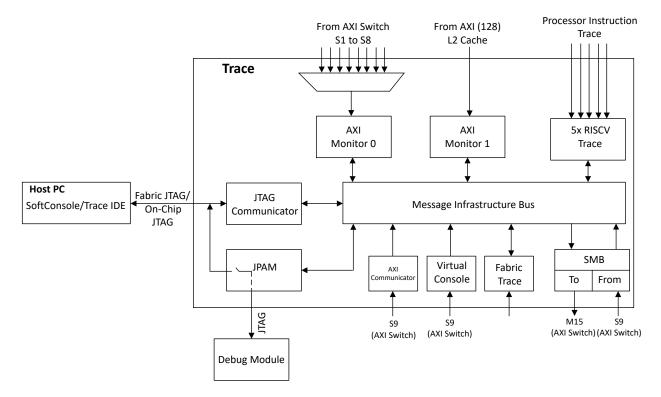

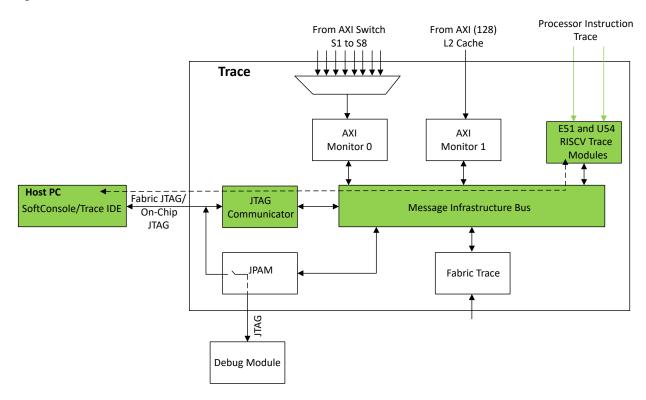

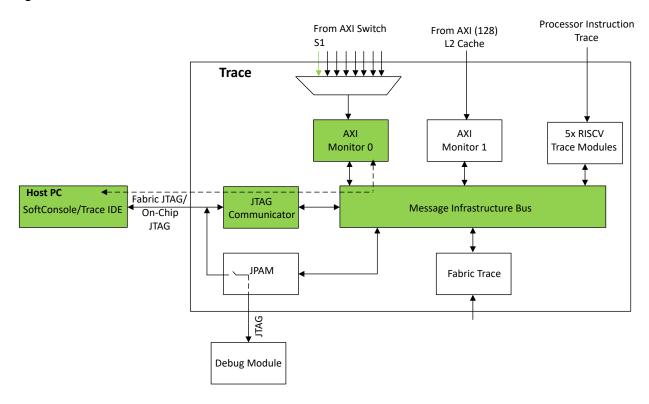

| 3.1.13. Debug<br>3.1.14. Trace                | JTAG based debug block for debugging all processor cores<br>Trace block for instruction trace for all processor cores                                                                                                             |  |

| 3.4. Memory Protection Unit                   | MPU block for each external AXI Master                                                                                                                                                                                            |  |

| 3.3. Fabric Interface Controllers (FICs)      | 64-bit AXI4 FIC (3x), 32-bit APB FIC (1x)                                                                                                                                                                                         |  |

| 3.10. User Crypto Processor                   | Athena F5200 TeraFire Crypto Processor (1x), 200 MHz                                                                                                                                                                              |  |

| Secure Boot                                   | Support for all U54 cores and E51 core                                                                                                                                                                                            |  |

| Anti-tamper Protection                        | Anti-tamper mesh for the MSS to detect tamper events                                                                                                                                                                              |  |

| 3.11. MSS DDR Memory Controller (1x) with ECC | MSS DDR memory controller with support for DDR3, DDR3L, DDR4, LPDDR3, and LPDDR4 memory devices.                                                                                                                                  |  |

| 3.12. Peripherals                             | Gigabit Ethernet MAC (GEM 2x), USB OTG 2.0 controller (1x), QSPI-XIP (1x), SPI (2x), eMMC 5.1 (1x), SD (1x), and SDIO (1x), MMUART (5x), I2C (2x), CAN (2x), GPIO (3x), RTC (1x), FRQMeter, Watchdogs (5x), and Timer (2x32 bit). |  |

| 3.9. MSS I/Os                                 | 38 MSS I/Os to support peripherals.                                                                                                                                                                                               |  |

#### Note:

1. In RV64GC "G" = "IMAFD"

# 2. Detailed Block Diagram (Ask a Question)

The MSS includes the following blocks:

- 3.1. CPU Core Complex

- 3.2. AXI Switch

- 3.3. Fabric Interface Controllers (FICs)

- 3.4. Memory Protection Unit

- 3.5. Segmentation Blocks

- 3.6. AXI-to-AHB

- 3.7. AHB-to-APB

- 3.8. Asymmetric Multi-Processing (AMP) APB Bus

- 3.9. MSS I/Os

- 3.10. User Crypto Processor

- 3.11. MSS DDR Memory Controller

- 3.12. Peripherals

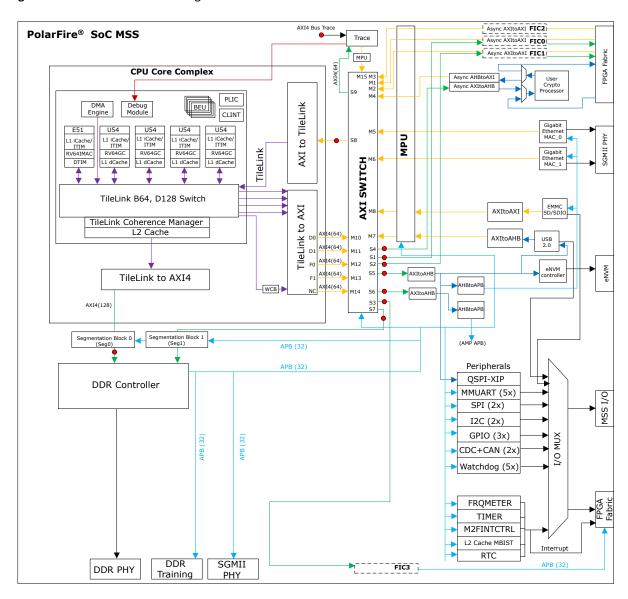

The following figure shows the functional blocks of the MSS in detail, the data flow from the CPU Core Complex to peripherals and vice versa.

Figure 2-1. MSS Detailed Block Diagram

# Notes: All AXI buses with red dot are fed into the Trace Block for monitoring The direction of arrows indicates control (master to slave). The flow of data is bi-directional: AXI 32/64-bit, AXI 64-bit, AHB 32-bit, APB 32-bit. AXI Master AXI Slave AHB APB

# 3. Functional Blocks (Ask a Question)

This section describes functional blocks of PolarFire SoC MSS.

# 3.1 CPU Core Complex (Ask a Question)

# 3.1.1 E51 RISC-V Monitor Core (Ask a Question)

The following table describes the features of E51.

Table 3-1. E51 RISC-V Monitor Core Features

| Feature     | Description                                                                     |

|-------------|---------------------------------------------------------------------------------|

| ISA         | RV64IMAC                                                                        |

| iCache/ITIM | 16 KB 2-way set-associative/8 KB ITIM                                           |

| DTIM        | 8 KB                                                                            |

| ECC Support | Single-Error Correction and Double-Error Detection (SECDED) on iCache and DTIM. |

| Modes       | Machine Mode, User Mode                                                         |

Typically, in a system, the E51 is used to execute the following:

- Bootloader to boot the operating system on U54 cores

- Bare-metal user applications

- Monitoring user applications on U54 cores

**Note:** Load-Reserved and Store-Conditional atomic instructions (Ir, sc) are not supported on the E51 processor core.

#### 3.1.1.1 Instruction Fetch Unit (Ask a Question)

The instruction fetch unit consists of a 2-way set-associative 16 KB instruction cache that supports 64-byte cache line size with an access latency of one clock cycle. The instruction cache is asynchronous with the data cache. Writes to memory can be synchronized with the instruction fetch stream using the FENCE. I instruction.

#### 3.1.1.2 Execution Pipeline (Ask a Question)

The E51 execution unit is a single-issue, in-order core with 5-stage execution pipeline. The pipeline comprises following five stages:

- 1. Instruction fetch

- 2. Instruction decode and register fetch

- 3. Execution

- 4. Data memory access

- 5. Register write back.

The pipeline has a peak execution rate of one instruction per clock cycle.

#### 3.1.1.3 ITIM (Ask a Question)

The 16 KB iCache can be partially reconfigured into 8 KB ITIM. The 8 KB ITIM address range is listed in Table 10-1. ITIM is allocated in quantities of cache blocks, so it is not necessary to use the entire 8 KB as ITIM. Based on the requirement, part of the iCache can be configured as 2-way set associative and part of the cache can be configured as ITIM.

#### 3.1.1.4 DTIM (Ask a Question)

E51 includes an 8 KB DTIM, the address range of the DTIM is listed in Table 10-1. The DTIM has an access latency of two clock cycles for full words and three clock cycles for smaller words. Misaligned accesses are not supported in hardware and result in a trap.

# 3.1.1.5 Hardware Performance Monitor (Ask a Question)

The CSRs described in the following table implement the hardware performance monitoring scheme.

Table 3-2. Hardware Performance Monitoring CSRs

| table 5 21 Halfa Walfe Fellow Manage Meditabiling costs |                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CSR                                                     | Function                                                                                                                                                                                                                                                                          |  |  |  |

| mcycle                                                  | Holds a count of the number of clock cycles executed by a Hart since some arbitrary time in the past. The arbitrary time is the time since power-up.                                                                                                                              |  |  |  |

| minstret                                                | Holds a count of the number of instructions retired by a Hart since some arbitrary time in the past. The arbitrary time is the time since power-up.                                                                                                                               |  |  |  |

| mhpmevent3 and<br>mhpmevent4                            | Event Selectors: Selects the events as described in Table 3-3, and increments the corresponding mhpmcounter3 and mhpmcounter4 counters.  The event selector register mhpmevent3 and mhpmevent4 are partitioned into two fields: event class and event mask as shown in Table 3-3. |  |  |  |

|                                                         | The lower 8 bits select an event class, and the upper bits form a mask of events in that class. The counter increments if the event corresponding to any set mask bit occurs.                                                                                                     |  |  |  |

|                                                         | For example, if mhpmevent3 is set to 0x4200, mhpmcounter3 increments when either a load instruction or a conditional branch instruction retires.                                                                                                                                  |  |  |  |

|                                                         | <b>Note:</b> In-flight and recently retired instructions may or may not be reflected when reading or writing the performance counters, or writing the event selectors.                                                                                                            |  |  |  |

| mhpmcounter3 and mhpmcounter4                           | 40-bit event counters                                                                                                                                                                                                                                                             |  |  |  |

Table 3-3. mhpmeventx Register

| Table 3-3. mhpmeventx Register                  |                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Event Class                                     | mhpmeventx[8:18] Bit Field Description Events                                                                                                                                                                                                                                                                                                                                              |

| mhpmeventx[7:0] = 0: Instruction Commit Events  | 8: Exception taken 9: Integer load instruction retired 10: Integer store instruction retired 11: Atomic memory operation retired 12: System instruction retired 13: Integer arithmetic instruction retired 14: Conditional branch retired 15: JAL instruction retired 16: JALR instruction retired 17: Integer multiplication instruction retired 18: Integer division instruction retired |

| mhpmeventx[7:0] = 1: Micro-architectural Events | 8: Load-use interlock 9: Long-latency interlock 10: CSR read interlock 11: Instruction cache/ITIM busy 12: Data cache/DTIM busy 13: Branch direction misprediction 14: Branch/jump target misprediction 15: Pipeline flush from CSR write 16: Pipeline flush from other event 17: Integer multiplication interlock                                                                         |

| continued                                 |                                                                 |  |

|-------------------------------------------|-----------------------------------------------------------------|--|

| Event Class                               | mhpmeventx[8:18] Bit Field Description Events                   |  |

| mhpmeventx[7:0] = 2: Memory System Events | 8: Instruction cache miss<br>9: Memory-mapped I/O access        |  |

|                                           | 10: Data cache write back                                       |  |

|                                           | 11: Instruction TLB miss                                        |  |

|                                           | 12: Data TLB miss                                               |  |

|                                           | <b>Note:</b> Only L1 cache performance monitoring is supported. |  |

#### 3.1.1.6 ECC (Ask a Question)

By default, the E51 iCache and DTIM implement SECDED for ECC. The granularity at which this protection is applied (the codeword) is 32-bit (with an ECC overhead of 7 bits per codeword). The ECC feature of L1 cache is handled internally, user control is not supported.

When a single-bit error is detected in the L1 iCache, the error is corrected automatically, and the cache line is flushed and written back to the next level of memory hierarchy. When a single bit error is detected in the L1 DTIM, the error is corrected automatically and written back to L1 DTIM.

# 3.1.1.6.1 ECC Reporting (Ask a Question)

ECC events are reported by the BEU block for a given core. The BEU can be configured to generate interrupts either globally via the Platform-Level Interrupt Controller (PLIC) or locally to the specific Hart where the ECC event occurred. When BEU interrupts are enabled, software can be used to monitor and count ECC events.

To detect uncorrectable ECC errors in the L1 cache memories, interrupts must be enabled in the BEU. The BEU must be configured to generate a local interrupt to halt the execution of a Hart when an uncorrectable instruction is detected. For more information about configuring ECC reporting, see 3.1.12. Bus Error Unit (BEU).

#### 3.1.2 U54 RISC-V Application Cores (Ask a Question)

The following table describes the features of the U54 application cores.

Table 3-4. U54 RISC-V Application Cores Features

| Feature     | Description                                  |

|-------------|----------------------------------------------|

| ISA         | RV64GC (1)                                   |

| iCache/ITIM | 32 KB 8-way set-associative/28 KB ITIM       |

| dCache      | 32 KB 8-way set-associative                  |

| ECC Support | ECC on iCache, ITIM, and dCache              |

| MMU         | 40-bit MMU compliant with Sv39               |

| Modes       | Machine mode, Supervisor mode, and User mode |

#### Note:

1. In RV64GC, "G" = "IMAFD".

Typically, in a system, the U54 cores are used to execute any of the following:

- · Bare-metal user applications

- Operating systems

**Note:** Load-Reserved and Store-Conditional atomic instructions (lr, sc) are supported on U54 processor cores.

#### 3.1.2.1 Instruction Fetch Unit (Ask a Question)

The instruction fetch unit consists of an 8-way set-associative 32 KB iCache/28 KB ITIM that supports 64-byte cache line size with an access latency of one clock cycle. The U54s implement the standard Compressed (C) extension of the RISC-V architecture which allows 16-bit RISC-V instructions.

## 3.1.2.2 Execution Pipeline (Ask a Question)

The U54 execution unit is a single-issue, in-order core with 5-stage execution pipeline. The pipeline comprises following five stages:

- 1. Instruction fetch

- 2. Instruction decode and register fetch

- 3. Execution

- 4. Data memory access

- 5. Register write back.

The pipeline has a peak execution rate of one instruction per clock cycle, and is fully bypassed so that most instructions have a one-cycle result latency.

Most CSR writes result in a pipeline flush with a five-cycle latency.

#### 3.1.2.3 Instruction Cache (Ask a Question)

The iCache memory consists of a dedicated 32 KB 8-way set-associative, Virtually Indexed Physically Tagged (VIPT) instruction cache memory with a line size of 64 bytes. The access latency of any block in the iCache is one clock cycle. iCache is not coherent with the platform memory system. Writes to iCache must be synchronized with the instruction fetch stream by executing the FENCE. I instruction.

A cache line fill triggers a burst access outside the CPU Core Complex. The U54 processor core caches instructions from executable addresses, with the exception of ITIM. See 3.1.3. CPU Memory Map for all executable address regions, which are denoted by the attribute X. Trying to execute an instruction from a non-executable address results in a trap.

#### 3.1.2.4 ITIM (Ask a Question)

iCache can be partially configured as ITIM, which occupies a 28 KB of address range in 3.1.3. CPU Memory Map. ITIM provides high-performance, predictable instruction delivery. Fetching an instruction from ITIM is as fast as an iCache hit, without any cache misses. ITIM can hold data and instructions. Load and store operations to ITIM are not as efficient as load and store operations to E51 DTIM.

The iCache can be configured as ITIM for any ways in units of cache lines (64 B bytes). A single iCache way must remain as instruction cache. ITIM is allocated simply by storing to it. A store to the nth byte of the ITIM memory map reallocates the first (n + 1) bytes of iCache as ITIM, rounded up to the next cache line.

ITIM can be deallocated by storing zero to the first byte after the ITIM region, that is 28 KB after the base address of ITIM as indicated in 3.1.3. CPU Memory Map. The deallocated ITIM space is automatically returned to iCache.

Software must clear the contents of ITIM after allocating it. It is unpredictable whether ITIM contents are preserved between deallocation and allocation.

#### 3.1.2.5 Data Cache (Ask a Question)

The U54 dCache has an 8-way set-associative 32 KB write-back, VIPT data cache memory with a line size of 64 bytes. Access latency is two clock cycles for words and double-words, and three clock cycles for smaller quantities. Misaligned accesses are not supported in hardware and result in a trap. dCache is kept coherent with a directory-based cache coherence manager, which resides in the L2 cache.

Stores are pipelined and committed on cycles where the data memory system is otherwise idle. Loads to addresses currently in the store pipeline result in a five-cycle latency.

### 3.1.2.6 Atomic Memory Operations (Ask a Question)

The U54 core supports the RISC-V standard Atomic (A) extension on regions of the Memory Map denoted by the attribute A in 3.1.3. CPU Memory Map. Atomic memory operations to regions that do not support them generate an access exception precisely at the core.

The load-reserved and store-conditional instructions are only supported on cached regions, hence generate an access exception on DTIM and other uncached memory regions.

See The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1 for more information on the instructions added by this extension.

#### 3.1.2.7 Floating Point Unit (Ask a Question)

The U54 FPU provides full hardware support for the IEEE 754-2008 floating-point standard for 32-bit single-precision and 64-bit double-precision arithmetic. The FPU includes a fully pipelined fused-multiply-add unit and an iterative divide and square-root unit, magnitude comparators, and float-to-integer conversion units, all with full hardware support for subnormals and all IEEE default values.

#### 3.1.2.8 MMU (Ask a Question)

The U54 has support for virtual memory using a Memory Management Unit (MMU). The MMU supports the Bare and Sv39 modes as described in The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.

The U54 MMU has a 39-bit virtual address space mapped to a 48-bit physical address space. A hardware page-table walker refills the address translation caches. Both instruction and data address translation caches are fully associative, and have 32 entries. The MMU supports 2 MB megapages and 1 GB gigapages to reduce translation overheads for large contiguous regions of virtual and physical address space.

U54 cores do not automatically set the Accessed (A) and Dirty (D) bits in a Sv39 PTE. The U54 MMU raises a page fault exception for a read to a page with PTE.A=0 or a write to a page with PTE.D=0.

#### 3.1.2.9 ECC (Ask a Question)

By default, the iCache, ITIM, and dCache implement SECDED for ECC. ECC is applied at the 32-bit codeword level, with an ECC overhead of 7 bits per codeword. The ECC feature of L1 cache is handled internally, user control is not supported.

When a single-bit error is detected in the ITIM, the error is corrected automatically and written back to the SRAM. When a single-bit error is detected in the L1 instruction cache, the error is corrected automatically and the cache line is flushed. When a single-bit error is detected in the L1 data cache, the data cache automatically implements the following sequence of operations:

- 1. Corrects the error.

- 2. Invalidates the cache line.

- 3. Writes the line back to the next level of the memory hierarchy.

The ECC reporting scheme is same as described in 3.1.1.6.1. ECC Reporting.

# 3.1.2.10 Hardware Performance Monitor (Ask a Question)

The scheme is same as described in 3.1.1.5. Hardware Performance Monitor.

#### 3.1.3 CPU Memory Map (Ask a Question)

The overall physical memory map of the CPU Core Complex is shown in 10. MSS Memory Map. The CPU Core Complex is configured with a 38-bit physical address space.

#### 3.1.4 Physical Memory Protection (Ask a Question)

Exclusive access to memory regions for a processor core (Hart) can be enabled by configuring its PMP registers. Each Hart supports a Physical Memory Protection (PMP) unit with 16 PMP regions. The PMP unit in each processor core includes the following control and status registers (CSRs) to enable the PMP:

- 3.1.4.1. PMP Configuration Register (pmpcfg)– used for setting privileges (R, W, and X) for each PMP region.

- 3.1.4.2. PMP Address Register (pmpaddr) used for setting the address range for each PMP region.

# 3.1.4.1 PMP Configuration Register (pmpcfg) (Ask a Question)

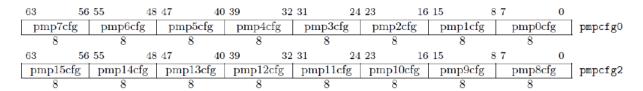

pmpcfg0 and pmpcfg2 support eight PMP regions each as shown in Figure 3-1. These two registers hold the configurations for the 16 PMP regions. Each PMP region is referred as pmpicfg. In pmpicfg, i ranges from 0 to 15 (pmp0cfg, pmp1cfg ... pmp15cfg). PolarFire SoC supports RV64. For RV64, pmpcfg1 and pmpcfg3 are not used.

Figure 3-1. RV64 PMP Configuration CSR Layout

Figure 3-2 shows the layout of a pmpicfg register. The R, W, and X bits, when set, indicate that the PMP entry permits read, write, and instruction execution, respectively. When one of these bits is cleared, the corresponding access type is denied. The Address-Matching (A) field encodes the Address-Matching mode of the associated PMP address register. The Locking and Privilege mode (L) bit indicates that the PMP entry is locked.

Figure 3-2. PMP Configuration Register Format

| 7 | [6:5]    | [4:3] | 2 | 1 | 0 |

|---|----------|-------|---|---|---|

| L | Reserved | Α     | X | W | R |

The A field in a PMP entry's configuration register encodes the address-matching mode of the associated PMP address register. When A=0, this PMP entry is disabled and matches no addresses. Three address-matching modes are supported—Top of Range (TOR), naturally aligned four-byte regions (NA4), naturally aligned power-of-two regions (NAPOT) as listed in the following table.

Table 3-5. Encoding of A field in PMP Configuration Registers

| Address Matching | Name  | Description                                      |

|------------------|-------|--------------------------------------------------|

| 0                | OFF   | No region (disabled)                             |

| 1                | TOR   | Top of range                                     |

| 2                | NA4   | Naturally aligned four-byte region               |

| 3                | NAPOT | Naturally aligned power-of-two region, ≥ 8 bytes |

NAPOT ranges make use of the low-order bits of the associated address register to encode the size of the range, as listed in Table 3-6.

Table 3-6. NAPOT Range Encoding

| and the state of t |                |                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------|--|--|

| pmpaddr<br>(Binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | pmpcfg.A Value | Match Type and Size     |  |  |

| aaaaaaaa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NA4            | 4-byte NAPOT range      |  |  |

| aaaaaaa0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 8-byte NAPOT range      |  |  |

| aaaaaa01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 16-byte NAPOT range     |  |  |

| aaaaa011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 32-byte NAPOT range     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                         |  |  |

| aa011111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 2XLEN-byte NAPOT range  |  |  |

| a0111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 2XLEN+1byte NAPOT range |  |  |

| 01111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NAPOT          | 2XLEN+2byte NAPOT range |  |  |

#### 3.1.4.1.1 Locking and Privilege Mode (Ask a Question)

The L bit indicates that the PMP entry is locked, that is, writes to the Configuration register (pmpicfg) and associated address registers (pmpaddr) are ignored. Locked PMP entries can only be unlocked with a system reset. In addition to locking the PMP entry, the L bit indicates whether the R/W/X permissions are enforced on Machine (M) mode accesses. When the L bit is set, these permissions are enforced for all privilege modes. When the L bit is clear, any M-mode access matching the PMP entry succeeds; the R/W/X permissions apply only to Supervisor (S) and User (U) modes.

#### 3.1.4.2 PMP Address Register (pmpaddr) (Ask a Question)

The PMP address registers are CSRs named from pmpaddr0 to pmpaddr15. Each PMP address register encodes the bits [55:2] of a 56-bit physical address as shown in the following figure.

Figure 3-3. RV64 PMP Address Register Format

| [63:54]  | [53:0]         |  |

|----------|----------------|--|

| Reserved | Address [55:2] |  |

| WIRI     | WARL           |  |

**Note:** Bits [1:0] of PMP address region are not considered because minimum granularity is four bytes.

For more information about the RISC-V physical memory protection, see The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10.

#### 3.1.5 L2 Cache (Ask a Question)

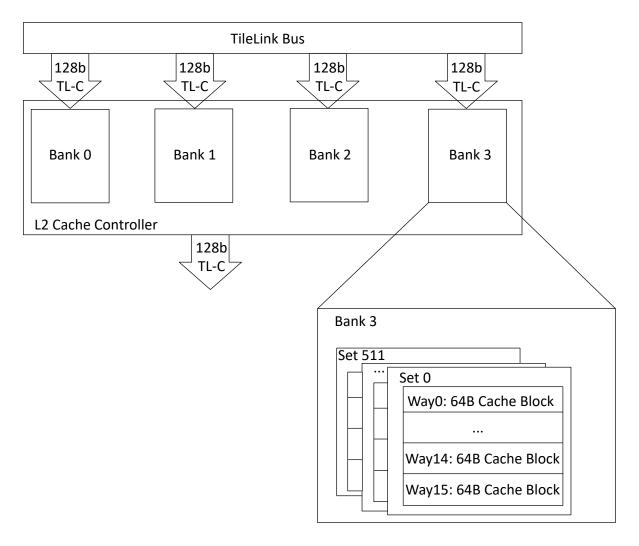

The shared 2 MB L2 cache is divided into four address-interleaved banks to improve performance. Each bank is 512 KB in size, and is a 16-way set-associative cache. The L2 also supports runtime reconfiguration between cache and scratchpad RAM.

#### 3.1.6 L2 Cache Controller (Ask a Question)

The L2 cache controller offers extensive flexibility as it allows for several features in addition to the Level 2 cache functionality such as memory-mapped access to L2 cache RAM for disabled cache ways, scratchpad functionality, way masking and locking, and ECC support with error tracking statistics, error injection, and interrupt signaling capabilities.

**Note:** L2 cache controller supports single-bit ECC via ECC registers. Dual-bit ECC is implemented by default and is not visible to the user.

#### 3.1.6.1 Functional Description (Ask a Question)

The L2 cache controller is configured into four banks, each bank contains 512 sets of 16 ways and each way contains a 64 byte block. This subdivision into banks facilitates increased available

bandwidth between CPU masters and the L2 cache as each bank has its own 128-bit TL-C (TileLink Cached) inner port. Hence, multiple requests to different banks may proceed in parallel.

The outer port of the L2 cache controller is a 128-bit TL-C port shared amongst all banks and connected to a DDR controller (see Figure 2-1). The overall organization of the L2 cache controller is shown in the following figure.

Figure 3-4. L2 Cache Controller

# 3.1.6.1.1 Way Enable and the L2 LIM (Ask a Question)

Similar to ITIM, L2 cache can be configured as LIM, or as a cache which is controlled by the L2 cache controller to contain a copy of any cacheable address.

When cache ways are disabled, they are addressable in the L2-LIM address space in 10. MSS Memory Map. Fetching instructions or data from the L2-LIM provides deterministic behavior equivalent to an L2 cache hit, with no possibility of a cache miss. Accesses to L2-LIM are always given priority over cache way accesses which target the same L2 cache bank.

After reset, all ways are disabled, except way0. Cache ways can be enabled by writing to the WayEnable register described in 3.1.6.3.2. Way Enable Register (WayEnable). Once a cache way is enabled, it cannot be disabled unless the Core Complex is reset. The highest numbered L2 cache way is mapped to the lowest L2-LIM address space, and way 1 occupies the highest L2-LIM address

range. When L2 cache ways are enabled, the size of the L2-LIM address space shrinks. The mapping of L2 cache ways to L2-LIM address space is shown in the following figure.

Bank 3 Bank 2 Bank 1 Reserved Bank 0 0x081E 0000 Set 511 Set 0 Way 1 Way0: 64B Cache Block 0x081C 0000 Way1: 64B Cache Block Way14: 64B Cache Block 0x0804 0000 Way15: 64B Cache Block Way 14 0x0802 0000 Way 15 0x0800 0000

Figure 3-5. Mapping of L2 Cache Ways to L2-LIM Addresses

#### 3.1.6.1.2 Way Masking and Locking (Ask a Question)

The L2 cache controller controls the amount of cache allocated to a CPU master using the <code>WayMaskX</code> register described in 3.1.6.3.13. Way Mask Registers (WayMaskX). <code>WayMaskX</code> registers only affect allocations and reads can still occur to ways which are masked. To lock down specific cache ways, mask them in all <code>WayMaskX</code> registers. In this scenario, all masters will be able to read data in the locked cache ways but not be able to evict.

#### 3.1.6.1.3 L2 Cache Power Control (Ask a Question)

Shutdown controls are provided for the 2 MB L2 cache memory with configuration support for either 512 KB, 1 MB, or 1,512 KB of L2 cache. This enables less static power consumption. The following 4-bit control register is provided for shutting down L2 cache blocks.

Table 3-7. L2 Cache Power Down

| Register               | Bits  | Description                                           |

|------------------------|-------|-------------------------------------------------------|

| L2_SHUTDOWN_CR (0x174) | [3:0] | Configured to shutdown L2 cache blocks of Bank 0 to 3 |

The above 4-bit control register powers down L2 cache blocks as per the physical RAM construction represented in the following table. Each bank contains 512 KB, constructed from thirty two 2048x64 RAMs (cc\_ram\_x), where the size of each RAM is 16 KB.

**Note:** Actual RAM width is 72 bits as an additional 8 ECC bits are used per 64-bit word.

Table 3-8. L2 RAM Shutdown

|  | L2_SHUTDOWN_CR[3] | L2_SHUTDOWN_CR[2] | L2_SHUTDOWN_CR[1] | L2_SHUTDOWN_CR [0] |

|--|-------------------|-------------------|-------------------|--------------------|

|--|-------------------|-------------------|-------------------|--------------------|

|        | cc_ram_24              | cc_ram_16              | cc_ram_8              | cc_ram_0             |

|--------|------------------------|------------------------|-----------------------|----------------------|

|        | cc ram 25              | cc ram 17              | cc ram 9              | cc ram 1             |

|        | cc ram 26              | cc ram 18              | cc ram 10             | cc ram 2             |

|        | cc_ram_27              | cc ram 19              | cc_ram_11             | cc_ram_3             |

| Bank 0 | cc ram 28              | cc ram 20              | cc ram 12             | cc_ram_4             |

|        | cc_ram_29              | cc_ram_21              | cc ram 13             | cc_ram_5             |

|        | cc_ram_30              | cc_ram_22              | cc ram 14             | cc_ram_6             |

|        | cc ram 31              | cc_ram_23              | cc ram 15             | cc_ram_7             |

|        | cc_ram_24              | cc_ram_16              | cc_ram_8              | cc_ram_0             |

|        | cc ram 25              | cc ram 17              | cc ram 9              | cc ram 1             |

|        | cc ram 26              | cc ram 18              | cc ram 10             | cc ram 2             |

|        | cc ram 27              | cc_ram_19              | cc_ram_11             | cc_ram_3             |

| Bank 1 | cc_ram_28              | cc ram 20              | cc ram 12             | cc_ram_4             |

|        | cc ram 29              | cc ram 21              | cc_ram_13             | cc_ram_5             |

|        | cc_ram_30              | cc_ram_22              | cc_ram_14             | cc_ram_6             |

|        | cc_ram_31              | cc_ram_23              | cc_ram_15             | cc_ram_7             |

|        | cc_ram_24              | cc_ram_16              | cc_ram_8              | cc_ram_0             |

|        | cc_ram_25              | cc_ram_17              | cc_ram_9              | cc_ram_1             |

|        | cc_ram_26              | cc_ram_17              | cc_ram_10             | cc_ram_2             |

|        | cc_ram_27              | cc_ram_10              | cc ram 11             | cc_ram_2             |

| Bank 2 | cc_ram_28              | cc_ram_19              | cc ram 12             | cc_ram_3             |

|        | cc_ram_29              | cc_ram_21              | cc_ram_12             | cc_ram_5             |

|        | cc_ram_30              | cc_ram_22              | cc_ram_14             | cc_ram_6             |

|        | cc_ram_31              | cc_ram_23              | cc_ram_14             | cc_ram_7             |

|        | cc_ram_24              | cc_ram_16              | cc_ram_8              | cc_ram_0             |

|        |                        |                        |                       |                      |

|        | cc_ram_25<br>cc_ram_26 | cc_ram_17<br>cc_ram_18 | cc_ram_9<br>cc_ram_10 | cc_ram_1<br>cc_ram_2 |

|        | cc_ram_27              | cc_ram_18              | cc_ram_10             | cc_ram_2             |

| Bank 3 |                        |                        |                       |                      |

|        | cc_ram_28              | cc_ram_20              | cc_ram_12             | cc_ram_4             |

|        | cc_ram_29              | cc_ram_21              | cc_ram_13             | cc_ram_5             |

|        | cc_ram_30              | cc_ram_22              | cc_ram_14             | cc_ram_6             |

|        | cc_ram_31              | cc_ram_23              | cc_ram_15             | cc_ram_7             |

# 3.1.6.1.4 Scratchpad (Ask a Question)

The L2 cache controller has a dedicated scratchpad address region which allows for allocation into the cache using an address range which is not memory backed. This address region is denoted as the L2 Zero Device in 10. MSS Memory Map. Writes to the scratchpad region will allocate into cache ways which are enabled and not masked. Care must be taken with the scratchpad, as there is no memory backing this address space. Cache evictions from addresses in the scratchpad results in data loss.

The main advantage of the L2 scratchpad over the L2-LIM is that it is a cacheable region allowing for data stored to the scratchpad to also be cached in a master's L1 data cache resulting in faster access.

The recommended procedure for using the L2 Scratchpad is as follows:

- 1. Use the WayEnable register to enable the desired cache ways.

- 2. Designate a single master which will be allocated into the scratchpad. For this procedure, designate the master as Master S. All other masters (CPU and non-CPU) will be denoted as Masters X.

- 3. Masters X: write to the WayMaskX register to mask all ways which are to be used for the scratchpad. This will prevent Masters X from evicting cache lines in the designated scratchpad ways.

- 4. Master S: write to the WayMaskX register to mask all ways except the ways which are to be used for the scratchpad. At this point Master S should only be able to allocate into the cache ways meant to be used as a scratchpad.

- 5. Master S: write scratchpad data into the L2 Scratchpad address range (L2 Zero Device).

- 6. Master S: Repeat steps 4 and 5 for each way to be used as scratchpad.

- 7. Master S: Use the WayMaskX register to mask the scratchpad ways for Master S so that it cannot evict cache lines from the designated scratchpad ways.

- 8. At this point, the scratchpad ways should contain the scratchpad data, with all masters able to read, write, and execute from this address space, and no masters able to evict the scratchpad contents.

#### 3.1.6.1.5 L2 ECC (Ask a Question)

The L2 cache controller supports ECC for Single-Error Correction and Double-Error Detection (SECDED). The cache controller also supports ECC for meta-data information (index and tag information) and can perform SECDED. The single-bit error injection is available for the user to control. Dual-bit error injection is handled internally without user control.

Whenever a correctable error is detected, the caches immediately repair the corrupted bit and write it back to SRAM. This corrective procedure is completely invisible to application software. However, to support diagnostics, the cache records the address of the most recently corrected meta-data and data errors. Whenever a new error is corrected, a counter is incremented and an interrupt is raised. There are independent addresses, counters, and interrupts for correctable meta-data and data errors.

DirError, DirFail, DataError, and DataFail signals are used to indicate that an L2 meta-data, data, or un-correctable L2 data error has occurred respectively. These signals are connected to the PLIC as described in 5.5.2. Interrupt Sources and are cleared upon reading their respective count registers.

#### 3.1.6.2 Register Map (Ask a Question)

The L2 cache controller register map is described in the following table.

Table 3-9. L2 Cache Controller Register Map

| Offset         | Width    | Attributes | Register Name      | Notes                                                                  |  |

|----------------|----------|------------|--------------------|------------------------------------------------------------------------|--|

| 0x000          | 4B       | RO         | Config             | Information on the configuration of the L2 cache                       |  |

| 0x008          | 1B       | RW         | WayEnable          | Way enable register                                                    |  |

| 0x040          | 4B       | RW         | ECCInjectError     | ECC error injection register                                           |  |

| 0x100          | 8B       | RO         | ECCDirFixAddr      | Address of most recently corrected metadata error                      |  |

| 0x108          | 4B       | RO         | ECCDirFixCount     | Count of corrected metadata errors                                     |  |

| 0x120          | 8B       | RO         | ECCDirFailAddr     | Address of most recent uncorrectable metadata error                    |  |

| 0x128          | 8B       | RO         | ECCDirFailCount    | Count of uncorrectable metadata errors                                 |  |

| 0x140          | 8B       | RO         | ECCDataFixAddr     | Address of most recently corrected data error                          |  |

| 0x148          | 4B       | RO         | ECCDataFixCount    | Count of corrected data errors                                         |  |

| 0x160          | 8B       | RO         | ECCDataFailAddr    | Address of most recent uncorrectable data error                        |  |

| 0x168          | 4B       | RO         | ECCDataFailCount   | Count of uncorrectable data errors                                     |  |

| 0x200<br>0x240 | 8B<br>4B | WO<br>WO   | Flush64<br>Flush32 | Flush cache block, 64-bit address<br>Flush cache block, 32-bit address |  |

| contin | continued |            |                             |                      |  |  |  |  |  |

|--------|-----------|------------|-----------------------------|----------------------|--|--|--|--|--|

| Offset | Width     | Attributes | Register Name               | Notes                |  |  |  |  |  |

| 0x800  | 8B        | RW         | Master 0 way mask register  | DMA                  |  |  |  |  |  |

| 0x808  | 8B        | RW         | Master 1 way mask register  | AXI4_front_port ID#0 |  |  |  |  |  |

| 0x810  | 8B        | RW         | Master 2 way mask register  | AXI4_front_port ID#1 |  |  |  |  |  |

| 0x818  | 8B        | RW         | Master 3 way mask register  | AXI4_front_port ID#2 |  |  |  |  |  |

| 0x820  | 8B        | RW         | Master 4 way mask register  | AXI4_front_port ID#3 |  |  |  |  |  |

| 0x828  | 8B        | RW         | Master 5 way mask register  | Hart 0 dCache MMIO   |  |  |  |  |  |

| 0x830  | 8B        | RW         | Master 6 way mask register  | Hart 0 iCache        |  |  |  |  |  |

| 0x838  | 8B        | RW         | Master 7 way mask register  | Hart 1 dCache        |  |  |  |  |  |

| 0x840  | 8B        | RW         | Master 8 way mask register  | Hart 1 iCache        |  |  |  |  |  |

| 0x848  | 8B        | RW         | Master 9 way mask register  | Hart 2 dCache        |  |  |  |  |  |

| 0x850  | 8B        | RW         | Master 10 way mask register | Hart 2 iCache        |  |  |  |  |  |

| 0x858  | 8B        | RW         | Master 11 way mask register | Hart 3 dCache        |  |  |  |  |  |

| 0x860  | 8B        | RW         | Master 12 way mask register | Hart 3 iCache        |  |  |  |  |  |

| 0x868  | 8B        | RW         | Master 13 way mask register | Hart 4 dCache        |  |  |  |  |  |

| 0x870  | 8B        | RW         | Master 14 way mask register | Hart 4 ICache        |  |  |  |  |  |

# 3.1.6.3 Register Descriptions (Ask a Question)

This section describes registers of the L2 cache controller. For more information, see PolarFire SoC Device Register Map.

# 3.1.6.3.1 Cache Configuration Register (Config) (Ask a Question)

The Config register can be used to programmatically determine information regarding the cache.

Table 3-10. Cache Configuration Register (Config)

| Register Offset 0x000 |            | 0x000      |       |                                                                      |

|-----------------------|------------|------------|-------|----------------------------------------------------------------------|

| Bits                  | Field Name | Attributes | Reset | Description                                                          |

| [7:0]                 | Banks      | RO         | 4     | Return the number of banks in the cache                              |

| [15:8]                | Ways       | RO         | 16    | Return the total number of enabled ways in the cache                 |

| [23:16]               | Sets       | RO         | 9     | Return the Base-2 logarithm of the number of sets in a cache bank    |

| [31:24]               | Bytes      | RO         | 6     | Return the Base-2 logarithm of the number of bytes in a cache blocks |

# 3.1.6.3.2 Way Enable Register (WayEnable) (Ask a Question)

The WayEnable register determines which ways of the L2 cache controller are enabled as cache. Cache ways which are not enabled, are mapped into the L2-LIM as described in 10. MSS Memory Map.

This register is initialized to 0 on reset and may only be increased. This means that, out of Reset, only a single L2 cache way is enabled as one cache way must always remain enabled. Once a cache way is enabled, the only way to map it back into the L2-LIM address space is by a Reset.

Table 3-11. Way Enable Register(WayEnable)

| Register Offset |            | 0x008            |   |                                                                                |  |

|-----------------|------------|------------------|---|--------------------------------------------------------------------------------|--|

| Bits            | Field Name | Attributes Reset |   | Description                                                                    |  |

| [7:0]           | Way Enable | RW               | 0 | Way indexes less than or equal to this register value may be used by the cache |  |

| [63:8]          | Reserved   | RW               | _ | _                                                                              |  |

# 3.1.6.3.3 ECC Error Injection Register (ECCInjectError) (Ask a Question)

The ECCInjectError register can be used to insert an ECC error into either the backing data or meta-data SRAM. This function can be used to test error correction logic, measurement, and recovery.

The ECC Error injection system works only during writes, which means that the stored data and ECC bits are modified on a write. ECC error is not injected or detected until a write occurs. Hence, a read will complete without ECC errors being detected if a write is not carried out after enabling the ECC error injection register.

Table 3-12. ECC Error Injection Register (ECCInjectError)

| Register Offset |              | 0x040      |       |                                                                                                                                                                                          |  |

|-----------------|--------------|------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bits            | Field Name   | Attributes | Reset | Description                                                                                                                                                                              |  |

| [7:0]           | Bit Position | RW         | 0     | Specifies a bit position to toggle, within an SRAM. The width is SRAM width depends on the micro architecture, but is typically 72 bits for data SRAMs and ≈ 24 bits for Directory SRAM. |  |

| [15:8]          | Reserved     | RW         |       | _                                                                                                                                                                                        |  |

| 16              | Target       | RW         | 0     | Setting this bit means the error injection will target the metadata SRAMs. Otherwise, the error injection targets the data SRAMs.                                                        |  |

| [31:17]         | Reserved     | RW         | _     | _                                                                                                                                                                                        |  |

#### 3.1.6.3.4 ECC Directory Fix Address (ECCDirFixAddr) (Ask a Question)

The ECCDirFixAddr register is a Read-Only register which contains the address of the most recently corrected metadata error. This field only supplies the portions of the address which correspond to the affected set and bank, because all ways are corrected together.

# 3.1.6.3.5 ECC Directory Fix Count (ECCDirFixCount) (Ask a Question)

The ECCDirFixCount register is a Read Only register which contains the number of corrected L2 meta-data errors. Reading this register clears the DirError interrupt signal described in 3.1.6.1.5. L2

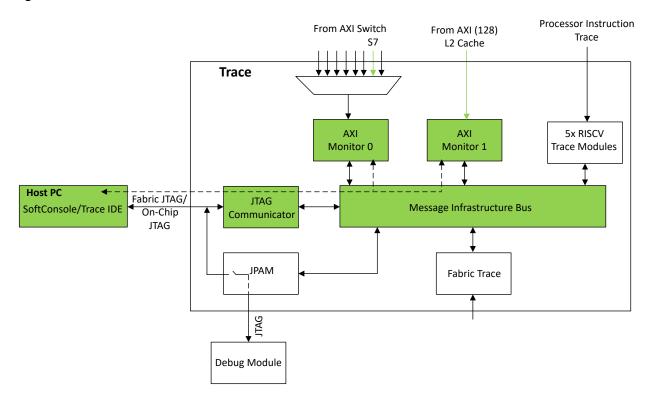

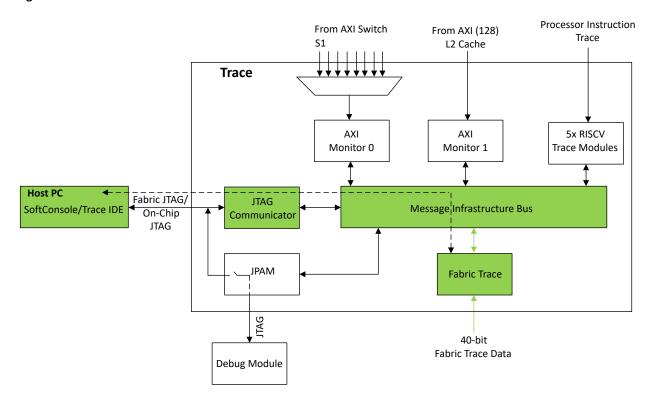

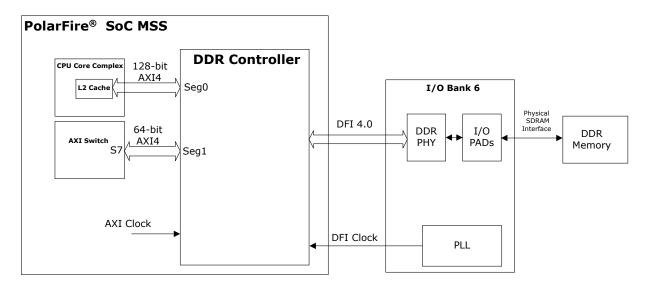

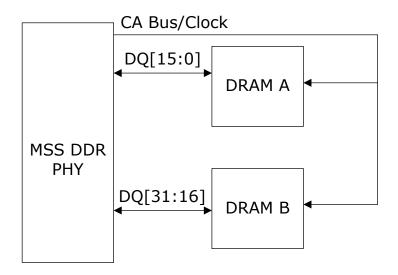

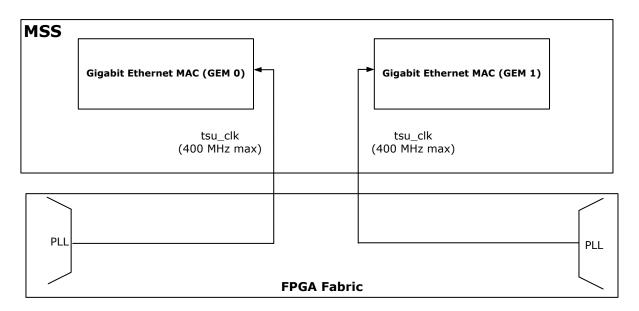

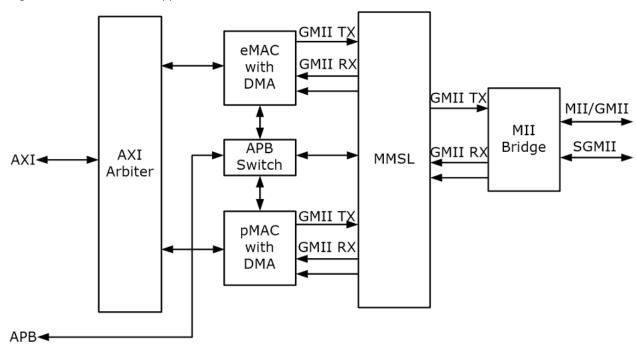

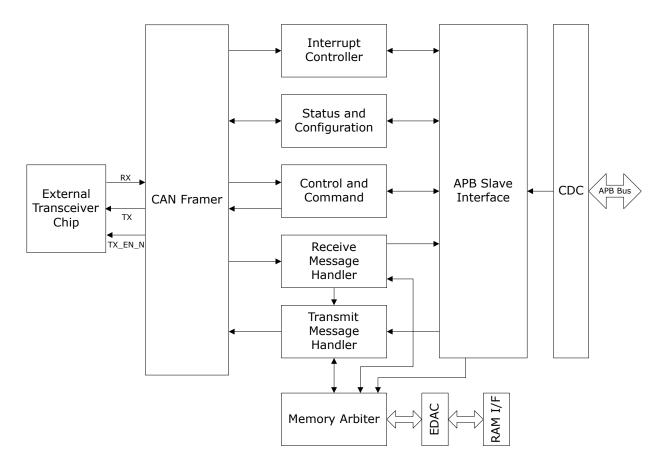

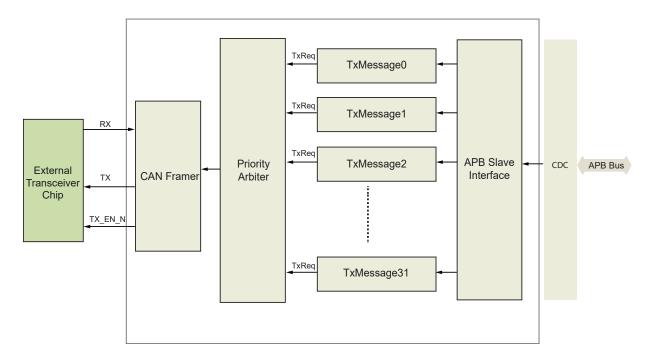

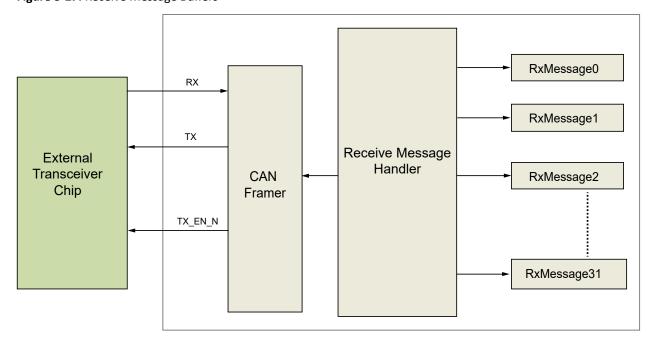

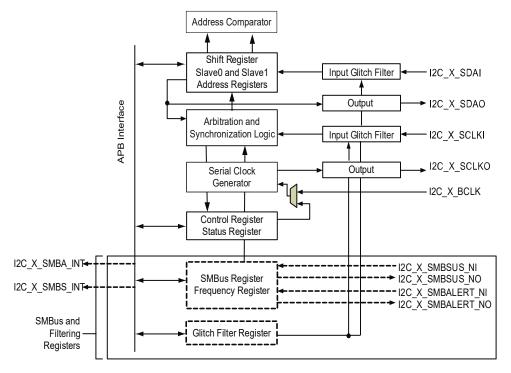

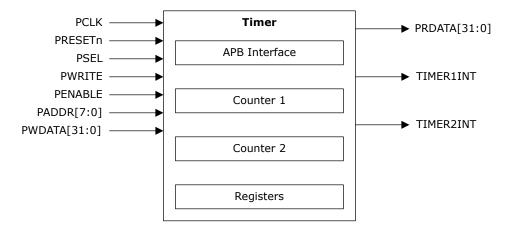

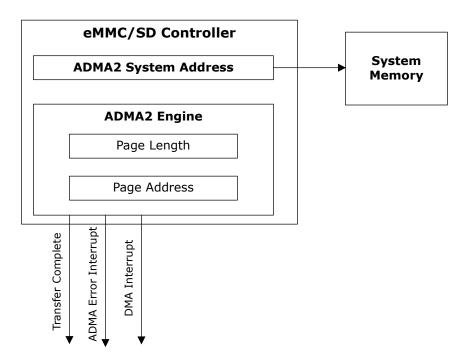

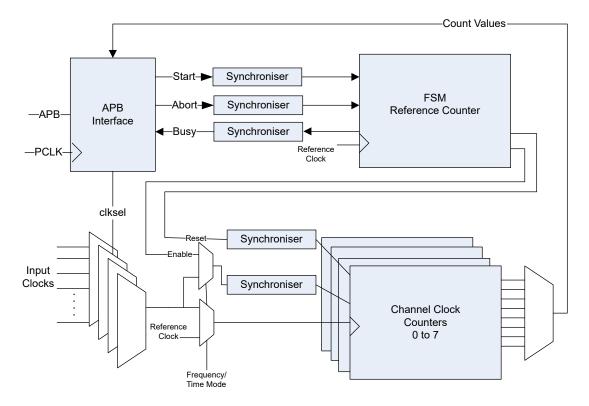

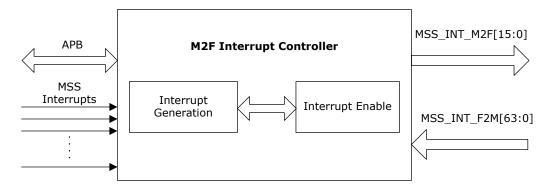

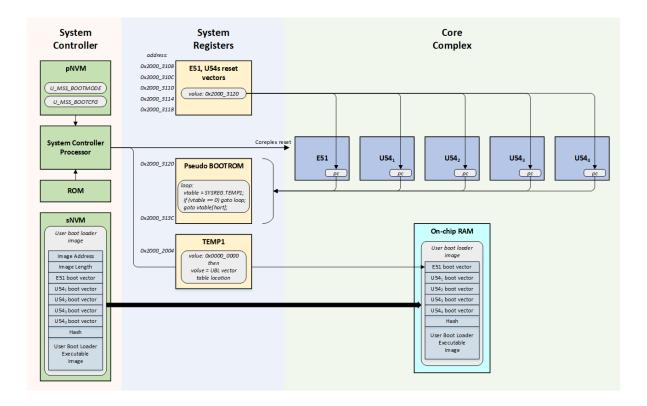

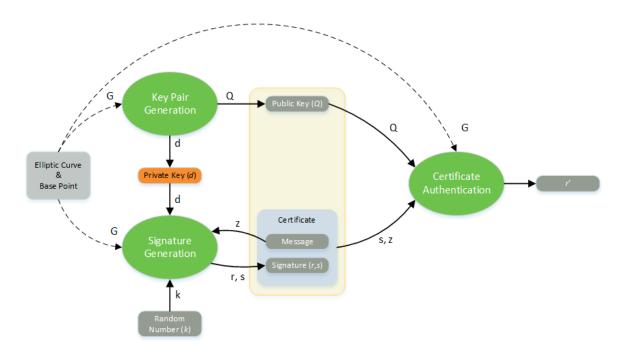

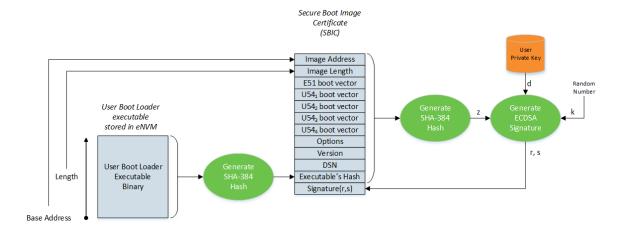

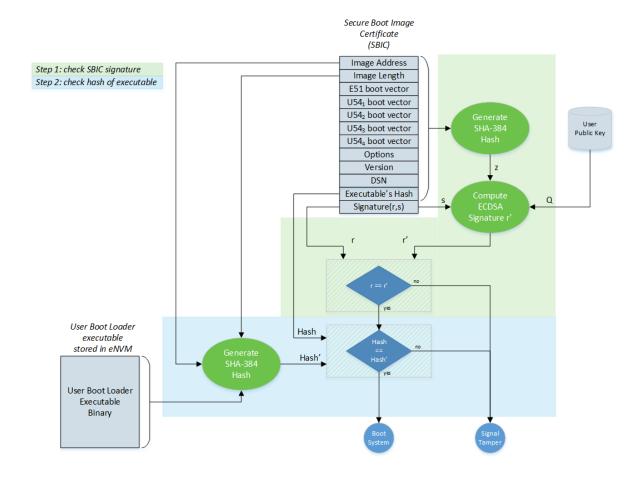

# 3.1.6.3.6 ECC Directory Fail Address (ECCDirFailAddr) (Ask a Question)