Představíme si řešení 100 Gb / s v sítích TCP Offload Engine a implementaci NVMe SSD na vývojové sadě KCU116 od Xilinx. Pomocí jádra TOE100G-IP Core od Design Gateway, které je určeno pro řešení s CPU a přenosem TCP 12 GB/s přes rozhraní 100 GbE, a jádrem NVMeG4-IP Core dokáže dosáhnout neuvěřitelně rychlého přenosu přibližně 4 GB/s na SSD.

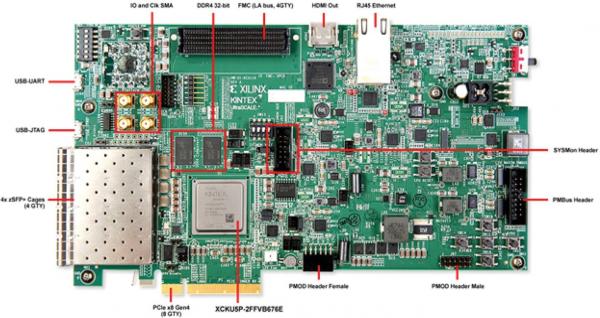

Vývojová sada Kintex UltraScale+ KCU116

KCU116 je ideální pro seznámení se s vlastnostmi Kintex UltraScale+, zejména přenosového výkonu transceiveru 28 Gb / s. Tato sada je vhodná pro rychlé prototypování založené na XCKU5P-2FFVB676E FPGA . Na desce je integrovaný 1 GB 32bitový DDR4-2666, rozšiřující porty FMC pro 1 x M.2 NVMe SSD a PCIe Gen4 x8 až pro 2 x M.2 NVMe SSD rozhraní. Transceivery GTY 16 x 28 Gb / s jsou určeny pro implementaci rozhraní PCIe Gen4 i 100 GbE a nabízejí řadu rozhraní a logiku FPGA pro uživatelsky přizpůsobené designy.

Obrázek 1: Vývojová sada KCU116. (Zdroj obrázku: Xilinx Inc.)

Spolu s IP jádry od Design Gateway poskytuje KCU116 vše, co je nutné k vývoji nejmodernějších 100Gbps síťových řešení, aniž by bylo nutné podporovat MPSoC.

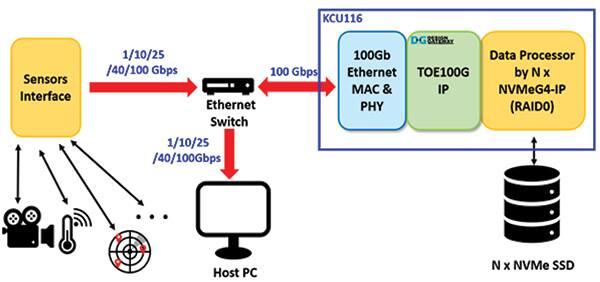

Implementace síťových řešení a úložišť 100 Gb/s

Obrázek 2: Řešení sítě a úložiště 100 Gb/s na KCU116. (Zdroj obrázku: Design Gateway)

I když Kintex UltraScale+ nemají technologii MPSoC, jako je například Zynq UltraScale+, lze síťové zpracování a zpracování protokolu NVMe pro úložiště implementovat bez potřeby procesorů a operačního systému. Využijí se IP jádra od Design Gateway:

- TOE100G-IP : 100 GbE Full TCP protokol stack IP Core bez potřeby CPU

- NVMeG4-IP : Samostatný hostitelský řadič NVMe s integrovanou PCIe Gen4 Soft IP

Jak TOE100G-IP, tak NVMeG4-IP mohou pracovat bez potřeby CPU/OS/ovladače. Uživatelskou logiku pro řízení a datovou cestu s oběma IP lze implementovat čistě hardwarovou logikou nebo bare-metal OS od společnosti Microblaze. To umožňuje rychlejší a snadnější vývoj aplikací a algoritmů na vysoké úrovni. To otevírá nové příležitosti pro pokročilá řešení na úrovni systému, jako je sběr dat ze senzorů, OnBoard Computing či Edge Computing založených na umělé inteligenci.

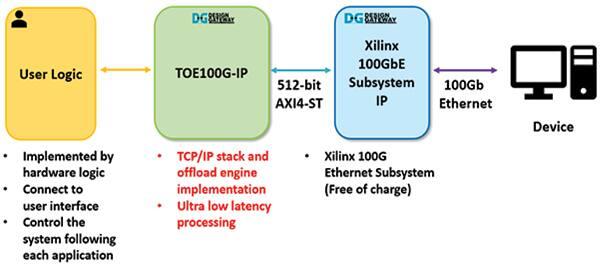

Gateway TOE100G-IP pro UltraScale+

Obrázek 3: Systémy TOE100G-IP. (Zdroj obrázku: Design Gateway)

Jádro TOE100G IP implementuje stack TCP/IP a je spojeno s modulem nižší vrstvy Xilinx 100 Gb Ethernet Subsystem. Uživatelské rozhraní TOE100G IP se skládá z rozhraní Register pro řídicí signály a rozhraní FIFO pro datové signály. TOE100G IP je navrženo pro připojení ke 100 Gb ethernetovému subsystému, který k připojení k uživatelskému rozhraní používá 512bitový AXI4-ST. Subsystém Ethernet poskytovaný společností Xilinx obsahuje funkce EMAC, PCS a PMA. Taktovací frekvence uživatelského rozhraní 100 Gb ethernetového subsystému je 322,265625 MHz.

Funkce TOE100G-IP

- Plná implementace stacku TCP/IP

- Podpora jedné relace jednou TOE100G IP (více relací lze implementovat pomocí více IP adres TOE100G)

- Podpora serverového i klientského režimu (pasivní/aktivní otevírání a zavírání)

- Podporujte Jumbo rámec

- Jednoduché datové rozhraní standardním rozhraním FIFO

- Jednoduché ovládací rozhraní pomocí rozhraní jednoho portu RAM

Využití zdrojů FPGA na zařízení XCKU5P-2FFVB676E FPGA je uvedeno v tabulce 1 níže.

Tabulka 1: Příklad implementace pro Kintex Ultrascale+

Další podrobnosti o TOE100G-IP jsou popsány v jeho datovém listu, který lze stáhnout z webových stránek Design Gateway.

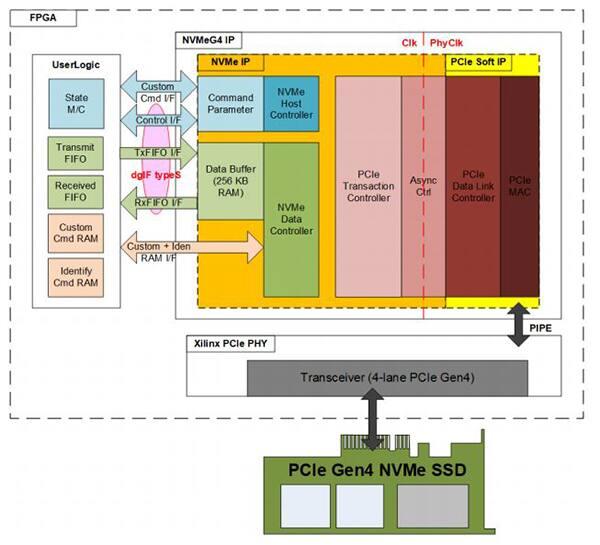

Hostitelský řadič NVMe PCIe Gen4 pro přijímače GTY

Kintex UltraScale+ je vybaven transceiverem GTY, který podporuje rozhraní PCIe Gen4. Integrovaný blokový a ARM procesor PCIe Gen4 není k dispozici. Design Gateway tento problém vyřešil vývojem jádra NVMeG4-IP, které je možné provozovat jako samostatný hostitelský řadič NVMe s integrovanou logikou PCIe soft IP a mostem PCIe v jednom jádru. Povolení přístupu k disku NVMe PCIe Gen4 SSD zjednodušuje uživatelské rozhraní a umožňuje navrhování standardních funkcí pro snadné použití, aniž by bylo nutné znát protokol NVMe.

Obrázek 4: Blokové schéma NVMeG4-IP. (Zdroj obrázku: Design Gateway)

Vlastnosti NVMeG4-IP

- Je schopen implementovat aplikační vrstvu, transakční vrstvu, vrstvu datového propojení a některé části fyzické vrstvy pro přístup k SSD NVMe bez CPU nebo externí paměti DDR

- Funguje s Xilinx PCIe PHY IP konfigurovanou jako 4proudová PCIe Gen4 (256bitové sběrnicové rozhraní)

- Obsahuje 256 kB RAM paměti pro data

- Podporuje šest příkazů, tj. Identify, Shutdown, Write, Read, Smart a Flush (k dispozici je volitelná další podpora příkazů)

- Taktovací frekvence uživatele musí být větší nebo rovna hodinám PCIe (250 MHz pro Gen4)

Využití zdrojů FPGA na zařízení XCKU5P-2FFVB676E FPGA je uvedeno v tabulce 2 níže.

Tabulka 2: Příklad implementace pro Kintex Ultrascale+.

Další podrobnosti o NVMeG4-IP jsou popsány v jeho datovém listu, který lze stáhnout z webových stránek Design Gateway.

Příklad implementace TOE100G-IP na KCU116

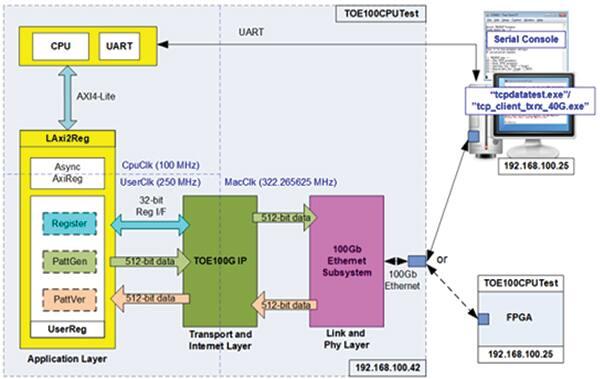

Obrázek 5 zobrazuje referenční návrh založený na KCU116, který demonstruje implementaci TOE100G-IP. Demo systém zahrnuje Bare-metal OS Microblaze systémy, uživatelskou logiku a 100 Gb ethernetové subsystémy Xilinx.

Obrázek 5: Blokové schéma demo systémů TOE100G-IP. (Zdroj obrázku: Design Gateway)

Demo systém je navržen tak, aby vyhodnotil provoz TOE100G-IP v klientském i serverovém režimu. Testování umožňuje odesílání a přijímání dat s testovacím vzorem pro nejvyšší možnou rychlost dat na straně uživatelského rozhraní. Pro rozhraní 100 GbE s KCU116 jsou vyžadovány čtyři transceivery SFP+ (25GBASE-R) a optický kabel, jak ukazuje obrázek 6.

Obrázek 6: Demo prostředí TOE100G-IP nastavené na KCU116. (Zdroj obrázku: Design Gateway)

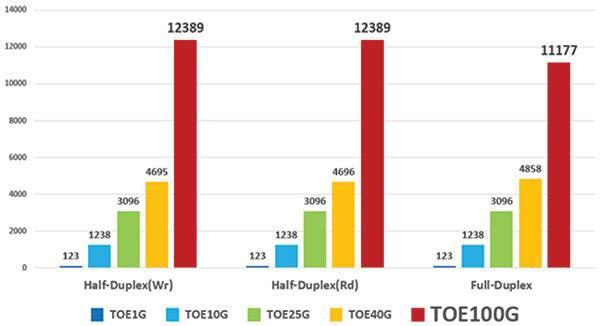

Příklad výsledku testu při porovnání 100G s ostatními (1G/10G/25G/40G) je uveden na obrázku 7.

Obrázek 7: Srovnání výkonu TOE100G-IP s 1G/10G/25G/40G na KCU116. (Zdroj obrázku: Design Gateway)

Výsledek testu ukazuje, že TOE100G-IP je schopen dosáhnout rychlosti přenosu přibližně 12 GB/s TCP.

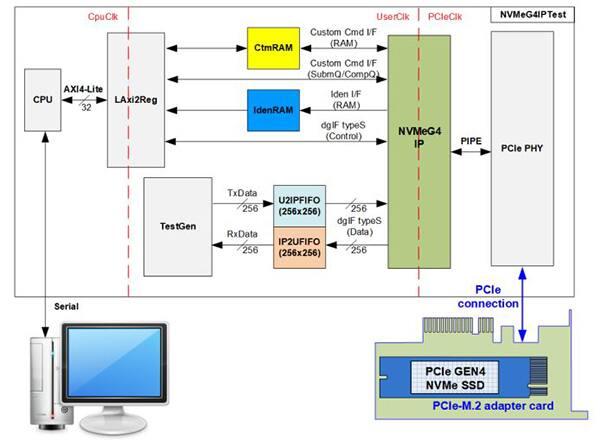

Příklad implementace NVMeG4-IP na KCU116

Obrázek 8 zobrazuje referenční návrh založeného na KCU116, který demonstruje implementaci 1CH NVMeG4-IP. Je možné implementovat více instancí NVMeG4-IP k dosažení vyššího výkonu úložiště, pokud jsou zdroje FPGA k dispozici z uživatelského designu. Další podrobnosti o referenčním návrhu NVMeG4-IP naleznete v referenčním dokumentu NVMeG4-IP na webu Design Gateway.

Obrázek 8: Referenční návrh NVMeG4-IP. (Zdroj obrázku: Design Gateway)

Demo systém je navržen tak, aby zapisoval a ověřoval data pomocí SSD NVMe na KCU116. Uživatel ovládá testovací provoz prostřednictvím sériové konzoly. Aby bylo NVMe SSD propojeno s KCU116, je nutný adaptér AB18-PCIeX16, jak ukazuje obrázek 9.

Obrázek 9: Demo prostředí NVMeG4-IP postavené na KCU116. (Zdroj obrázku: Design Gateway)

Příklad výsledku testu při spuštění demo systému na KCU116 při použití 512 GB Samsung 970 Pro je na obrázku 10.

Obrázek 10: Výkon čtení/zápisu NVMe SSD na KCU116 pomocí Samsung 970 PRO S. (Zdroj obrázku: Design Gateway)

Závěr

Jak jádro TOE100G-IP, tak NVMeG4-IP poskytují stabilní připojení 100 Gb / s na desce KCU116 pro síťové aplikace a úložiště NVMe. Jeden TOE100G-IP je schopen přenosu přibližně 12 GB TCP přes 100 GbE. NVMeG4-IP může poskytovat velmi výkonné úložiště s NVMe PCIe Gen4 s rychlostí přibližně 4 GB/s na SSD. K vytvoření řadiče RAID0 lze použít více instancí NVMeG4-IP zvýšit tak výkon úložiště, aby odpovídal přenosové rychlosti až 100 GbE. Vývojová sada KCU116 a řešení od Design Gateway umožňují dosáhnout nejvyššího možného výkonu s co nejnižším využitím zdrojů FPGA. Podrobnější informace o TOE100G-IP a NVMeG4-IP, datové listy, dostupný referenční design a nastavení demo prostředí jsou k dispozici na webových stránkách Design Gateway:

Článek vyšel v originále na webu DigiKey.com, autorem je Thanaporn Sangpaithoon.