V článku nalezneme popis architektury SoC FPGA a jejich použití v deterministických systémech včetně detailního popisu zabezpečení. Představíme si FPGA SoC od Microchip Technology spolu s jeho vývojovou platformou a v závěru se budeme věnovat rozšiřujícím deskám od MikroElektronika, díky kterým lze systém obohatit o řadu komunikačních rozhraní nebo o lokalizaci pomocí satelitního systému GNSS.

SoC postavené na struktuře FPGA

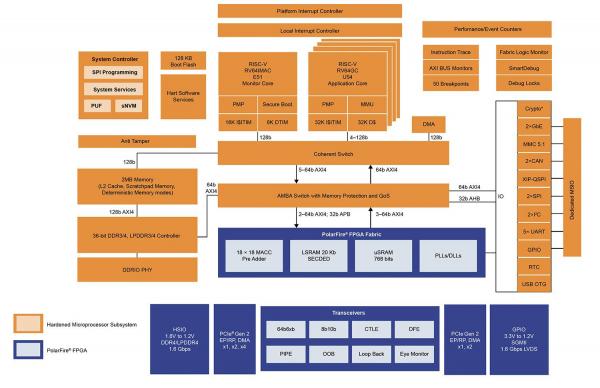

SoC je postaven na struktuře FPGA a to včetně MCU subsystému RISC-V. Subsystém MCU obsahuje čtyřjádrový cluster RISC-V, jádro RISC-V, systémový řadič a deterministický paměťový subsystém úrovně 2 (L2). FPGA v SoC obsahuje 460 K logických prvků, 12,7 Gb/s transceiver, vstupně/výstupní (I/O) bloky, GPIO a také sběrnici PCIe2.0. Architektura zahrnuje opravné funkce „single-error correction a double-error detection“ (SECDED) na všech pamětích. Součástí architektury je také analýza diferenciálního napájení (DPA), ochrana fyzické paměti a 128 kbitů Flash paměť (obrázek 1).

Obrázek 1: Všechny prvky včetně subsystémů RISC-V jsou implementovány na FPGA struktuře. (Zdroj obrázku: Microchip Technology)

Microchip nabízí ekosystém Mi-V (vyslovováno jako „my five“) s nástroji třetích stran na podporu implementace systémů RISC-V. Je navržen tak, aby urychlil přijetí instrukční sady RISC-V (ISA) pro jádra RISC-V. Mezi prvky ekosystému Mi-V patří:

- Licence duševního vlastnictví (IP).

- Hardware

- Operační systémy a middleware

- Debuggery, kompilátory a služby

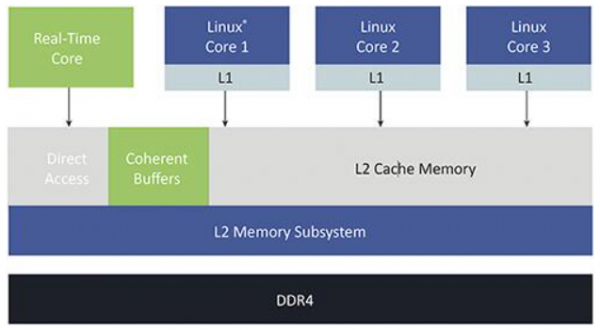

MCU RISC-V v FPGA SoC nabízí několik možností ladění, jako je run-time advanced extended interface (AXI) a sledování instrukcí. AXI umožňuje monitorovat data, která se zapisují nebo čtou z různých pamětí. Subsystém RISC-V MCU není zranitelný vůči exploitům Spectre nebo Meltdown. Exploit je speciální program, data nebo sekvence příkazů, které využívají programátorskou chybu. Tato chyba může způsobit původně nezamýšlenou činnost software a umožňuje tak získat nějaký přístup do systému. Všech pět MCU je koherentních s paměťovým subsystémem a podporují systémy reálného času v režimu deterministického asymetrického multi-processingu (AMP) a Linuxu. Mezi schopnosti subsystému RISC-V patří (obrázek 2):

- Spouštění Linuxu a operace v reálném čase

- Konfigurace L1 a L2 jako deterministickou paměť

- Paměťový subsystém DDR4

- Zakázat/povolit prediktory větví

- Provoz pipeline v určitém pořadí

Obrázek 2: Subsystém RISC-V obsahuje několik procesorových a paměťových prvků. (Zdroj obrázku: Microchip Technology)

Vyšší výkon a zároveň menší spotřeba energie

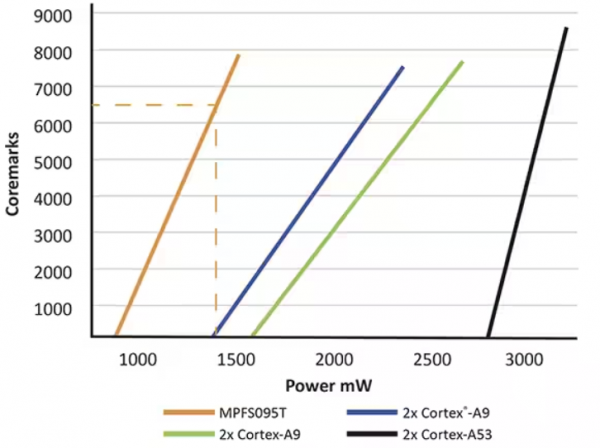

I když SoC mají vysoký výpočetní výkon, který obstojí i v aplikacích reálného času, tak jejich spotřeba je vzhledem k výkonu relativně nízká. Benchmark EEMBC CoreMark-PRO je průmyslový standard pro porovnávání účinnosti a výkonu MCU ve vestavěných systémech. Byl navržen speciálně pro srovnávání výkonu hardware a nahrazuje benchmark Dhrystone.

Pracovní zátěže CoreMark-PRO zahrnují rozmanitost výkonnostních charakteristik, paralelismus na úrovni instrukcí a využití paměti založené na čtyřech pracovních zátěžích s pohyblivou desetinnou čárkou a pěti běžných celočíselných úlohách. Pracovní zátěže s plovoucí desetinnou čárkou zahrnují rutinu lineární algebry odvozenou z LINPACK, rychlou Fourierovu transformaci, algoritmus neuronové sítě pro vyhodnocování vzorů a vylepšenou verzi benchmark smyček Livermore. Komprese JPEG, analyzátor XML, komprese ZIP a 256bitový bezpečný hashový algoritmus (SHA-256) tvoří základ celočíselných pracovních zátěžových testů. Modely MPFSO95T SoC FPGA jako je MPFS095TL-FCSG536E mohou dosáhnout až 6 500 Coremarků při spotřebě 1,3 wattu (obrázek 3).

Obrázek 3: MPFS095T FPGA SoC (oranžová řada) poskytuje 6500 Coremarků při 1,3 wattu. (Zdroj obrázku: Microchip Technology)

Bezpečnostní aspekt

FPGA SoC disponují silnými bezpečnostními prvky, mezi které patří diferenciální analýza výkonu (DPA - differential power analysis), skutečný generátor náhodných čísel (TRNG) a fyzicky neklonovatelná funkce (PUF - physically unclonable function), který slouží jako jedinečný identifikátor. K dispozici je také uživatelem definované bezpečné spouštění, ochrana fyzické paměti, která poskytuje omezení přístupu do paměti, supervizor a imunita proti útokům Meltdown a Spectre.

Zabezpečení začíná bezpečným řízením dodavatelského řetězce, a to použití hardwarových bezpečnostních modulů (HSM) během testování a balení waferů. Použití 768 bajtového digitálně podepsaného x.509 FPGA certifikátu zabudovaného do každého FPGA SoC přispívá k bezpečnosti celého dodavatelského řetězce. SoC FPGA obsahují detektory neoprávněné manipulace přímo na čipu, a je zajištěna bezpečnost a spolehlivý provoz. Pokud je zjištěna neoprávněná manipulace, je vydán příznak neoprávněné manipulace, a systém může reagovat podle potřeby. Detektory manipulace mohou být:

- Monitory napětí

- Teplotní senzory

- Detektory chybových hodin a hodinové frekvence

- Aktivní detektor JTAG

- Síťový aktivní detektor

Zabezpečení je dále zajištěno pomocí 256 bitového pokročilého šifrovacího standardu AES-256 (CPA), integrovaných kryptografických funkcí pro zajištění integrity dat, integrovaného PUF pro ukládání klíčů a možnost nulování FPGA a všech pamětí na čipu.

Příklady SoC FPGA

Microchip nabízí SoC PolarFire FPGA s několika rychlostními stupni, teplotními rozsahy, různými velikostmi pouzder a logickými prvky od 25 K do 460 K. K dispozici jsou čtyři teplotní stupně, rozšířený komerční rozsah 0 °C až +100 °C, průmyslový rozsah -40 °C až +100 °C, automobilový rozsah -40 °C až +125 °C a vojenský rozsah -55 °C až +125°C.

K dispozici jsou dvě kategorie produktů, co se týče rychlosti. Standardní rychlostí a rychlost o 15 % větší, která je pod označením speed grade -1. SoC FPGA napájené napětím 1,0 V jsou určeny pro provoz s nejnižším výkonem a s napájením 1,05 V se dosahuje výkon vyšší. Velikosti pouzder SoC FPGA jsou velikosti 11 x 11 mm, 16 x 16 mm a 19 x 19 mm.

Pro aplikace, které vyžadují rozšířený teplotní rozsah, standardní rychlost a 254 K logických prvků v pouzdře 19 x 19 mm, je ideální volbou MPFS250T-FCVG484EES. Pro jednodušší aplikace, která potřebují jen 23 K logických prvků, lze využít MPFS025T-FCVG484E, který má rovněž rozšířený teplotní rozsah, standardní rychlost a pouzdro o velikosti 19 x 19 mm.

MPFS250T -1FCSG536T2 s 254 K logickými prvky je určen pro vysoce výkonné automobilové systémy a jeho teplotní rozsah je od -40 do 125 °C. Rychlost je o 15% vyšší, a tak je označen jako speed grade -1. Je uložen do pouzdra o velikosti 16 x 16 mm s 536 kuličkami s roztečí 0,5 mm (obrázek 4).

Obrázek 4: MPFS250T-1FCSG536T2 s teplotním rozsahem pro automobilový průmysl se dodává v pouzdře o velikosti 16 x 16 mm s počtem kuliček 536 a roztečí 0,5 mm. (Zdroj obrázku: Microchip Technology)

Vývojová platforma SoC FPGA

Pro urychlení návrhu systémů s SoC PolarFire FPGA nabízí Microchip sadu MPFS-ICICLE-KIT-ES PolarFire SoC Icicle kit, která umožňuje získat zkušenosti s pětijádrovým mikroprocesorovým subsystémem RISC-V. Sada obsahuje bezplatnou licenci Libero Silver, která je potřebná pro hodnocení jednotlivých návrhů. Podporuje funkce programování a ladění v jediném jazyce.

Tyto SoC FPGA jsou podporovány vývojovou sadou VectorBlox Accelerator Software Development Kit (SDK), která umožňuje nízkoenergetické aplikace AI/ML v malém formátu. Důraz je kladen na zjednodušení celého procesu návrhu do té míry, že není potřeba mít předchozí zkušenosti s návrhem FPGA. Sada VectorBlox Accelerator SDK umožňuje programovat energeticky úsporné neuronové sítě pomocí C/C++.

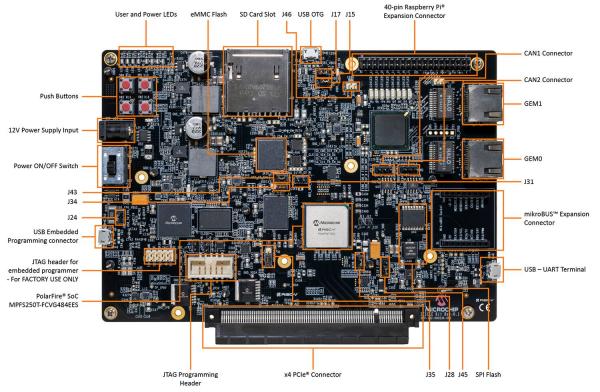

Sada Icicle má řadu funkcí, které poskytují komplexní vývojové prostředí, včetně multi-rail systému snímačů napájení, portu PCIe a vestavěných pamětí LPDDR4, QSPI a eMMC Flash pro provoz Linuxu. Dále jsou k dispozici rozšiřující konektory Raspberry Pi a mikroBUS (obrázek 5).

Obrázek 5: Toto komplexní vývojové prostředí SoC FPGA obsahuje konektory pro rozšiřující desky Raspberry Pi (vpravo nahoře) a mikroBUS (pravá dolní strana). (Zdroj obrázku: Microchip Technology)

Rozšiřující desky

Několik příkladů rozšiřujících desek mikroBUS:

- MIKROE-986 - CAN

- MIKROE-1582 - RS-232.

- MIKROE-989 - RS422/485.

- MIKROE-3144 - technologie LTE Cat M1 a NB1 umožňující spolehlivou a jednoduchou konektivitu se zařízeními 3GPP IoT.

- MIKROE-2670 - GNSS se současným příjmem GPS a Galileo plus buď BeiDou nebo GLONASS. To má za následek vysokou přesnost polohy v situacích se slabým signálem nebo rušením v městských zástavbách.

Závěr

SoC FPGA poskytují širokou škálu systémových prvků, včetně FPGA struktury, RISC-V MCU subsystému s vysoce výkonnými pamětmi, vysokorychlostními komunikačními rozhraními a několika bezpečnostními funkcemi. K dispozici jsou vývojové desky a prostředí, které obsahují všechny potřebné prvky, včetně rozšiřujících desek, které lze použít k implementaci široké škály komunikačních a lokalizačních funkcí.

Další informace:

- How to Implement Time Sensitive Networking to Ensure Deterministic Communication

- Real-Time Operating Systems (RTOS) and Their Applications

Článek vyšel v originále na webu DigiKey.com