Pomocí vývojové desky GateMate lze ověřit všechny možnosti FPGA čipu CCGM1A1 a zároveň ji lze použít jako referenční návrh při vývoji výpočetně výkonných aplikací. Pomocí konektorů Pmod lze připojit další hardware, a lze tak jednoduše získat prototyp finálního produktu ve velmi krátkém čase. Pmod rozhraní je běžnou součástí řady periferních desek, které obsahují drivery motorů, senzory, displeje a mnoho dalších podpůrných zařízení.

Vývojová deska GateMate nabízí:

- Hostitelské rozhraní USB

- Rozhraní JTAG a SPI

- Flash paměť přímo na desce

- Rozhraní Serializer/Deserializer (SerDes).

- Pmod rozhraní

- Integrovaný modul HyperRAM

- 108 univerzálních vstupů a výstupů (GPIO)

- Napětí VCore (0,9 až 1,1 V) a Vio (1,2 až 2,5 V)

- 7 stavových LED

Vývojová deska GateMate obsahuje všechny potřebné komponenty, aby zajistila co nejvyšší výkon a flexibilitu a zároveň nabízí plnou kontrolu nad jádrem a vstupy/výstupy. Díky tomu lze přesně a efektivně řídit rychlost a spotřebu systému. Čipy řady GateMate obsahují 40 000 až 1 milion tzv. LUT jednotek (lookup table). LUT je digitální obvod, který lze použít k implementaci libovolné booleovské funkce v návrhu FPGA. Toto množství LUT jednotek splňuje vlastnosti malých až středně velkých FPGA.

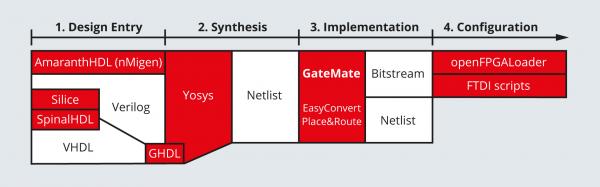

Vývojový systém GateMate lze zdarma stáhnout z Githubu a obsahuje nástroj pro syntézu Verilog nebo VHDL. Pomocí nástroje Place&Route lze vytvořit výstupní soubory pro simulátory a generovat soubor bitového toku pro programování FPGA. Příklad takového souboru je zobrazen na obrázku níže.

Syntéza RTL z VHDL nebo Verilog se provádí pomocí open source softwarové sady Yosys. Yosys zahrnuje rozsáhlou podporu jazyku Verilog. Pro vývoj v abstraktním jazyce VHDL je k dispozici zásuvný modul GHDL do Yosys. Lze použít i jiné jazyky HDL nebo nástroje s Verilog backendem.

Syntéza generuje Verilog netlist a ten je pak předán do nástroje Place&Tool. Tam se vytvoří bitstream pro programování a v případě potřeby i netlist s informacemi o časování. Simulaci časování lze provést například pomocí simulátoru Icarus Verilog Simulator třetí strany a prohlížečem GTKWave Waveform Viewer. Konfigurační soubor se pak nahraje do FPGA nebo externího flash disku pomocí OpenFPGALoader.

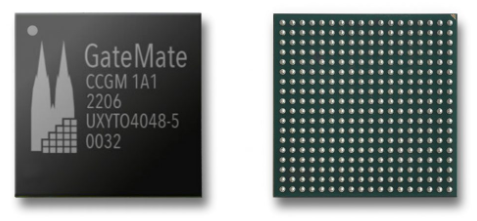

GateMate CCGM1A1 je vyráběn technologií 28SLP v GF Factory 1 v Drážďanech. Tím je sníženo obchodní riziko na minimum. Díky použité technologii se dosáhlo velmi vysoké hustoty a čip má velmi malou spotřebu energie. Tím se odstranil hlavní nedostatek FPGA čipů s integrovanou SRAM pamětí. Čip A1 je prvním členem rodiny, který je již dostupný ve vzorcích a čip A2 je plánován ve formě vzorků ve 2. čtvrtletí 2023.

Vlastnosti CCGM1A1:

- Logická kapacita: 20,000 až 500 000 logických buněk

- Duální SRAM 1280kBit

- Tři provozní režimy: Low Power, Economy, Speed

- FPGA v BGA pouzdře - malé rozměry a vysoký počet pinů (324 balls, pouzdro FPGA 15x15 mm)

- Na desce plošných spojů jsou vyžadovány pouze dvě signálové vrstvy

- General Purpose IO (GPIO) konfigurovatelné jako single-ended nebo LVDS

- Nízký počet konfiguračních bitů

- Konfigurace pomocí 4Bit SPI rozhraní až do 100MHz

- Minimální proudové rázy při spouštění

- Vícenásobná schémata taktování

- Dvouportové bloky paměti RAM s datovou šířkou 1 až 80 bitů, také konfigurovatelné jako FIFO

- Lze implementovat multiplikátory s libovolnou bitovou šířkou

- Podpora SERDES 2,5 Gbit/s

- Konfigurovatelné pull-up/pull-down rezistory

- Podpora pro ADC a DAC s dalšími jádry IP

- GateMate Place & Route s automatickou optimalizací hodinového signálu

- Statická časová analýza pro hodnocení výkonu

Podrobnosti o čipu naleznete na: https://www.colognechip.com/programmable-logic/gatemate/

Podrobnosti o vývojové desce naleznete na: https://www.colognechip.com/programmable-logic/gatemate-evaluation-board/

Pro více informací kontaktujte distributora Codico (www.codico.com): Petr.Rocek@codico.com. Zde také můžete směřovat veškeré své dotazy.