Sběrnice PCI-Express (je známá také jako 3GIO = 3rd Generation I/O) je logickým pokračováním implementace dnes hojně využívané PCI sběrnice. Používá existující komunikační standardy - je však založena na mnohem rychlejší sériové komunikaci. Na standardu PCI-Express začala jako první pracovat společnost Intel.

PCI-Express (PCI-E) je určena pro použití jako lokální sběrnice. Protože je založena na původním PCI systému, rozšiřující karty a systémy mohou být převedeny na PCI-E pouze změnou fyzické vrstvy. Rychlost PCI-E sběrnice předčí současné interní sběrnice jako např. AGP (viz ?Propustnost PCI-E sběrnice ? níže). Existují i návrhy, kdy by jediný řadič PCI-E komunikující s externími zařízeními nahradil v současnosti na základních deskách využívané řešení s northbridge a southbridge.

Rozdíl mezi PCI a PCI-E

-

Sběrnice PCI (Peripherial Component Interconnect ) využívaly k přenosu jeden vodič s dvoustavovou modulací (logická úroveň 1 nebo 0) - naproti tomu sběrnice PCI-E využívá dva vodiče v diferenciálním zapojení. Modulace vodičů je obvykle vícestavová - používají se obvody preemfáze sloužící k úpravě signálů na vedení. Tento typ modulace slouří především k potlačení ztrát vznikajících na vedení například vlivem skinefektu nebo vyzařování.

PCI-E Link představuje komunikační kanál mezi dvěma zařízeními sběrnice PCI-E. Základní PCI-E Link je sestaven ze dvou nízkonapěťových diferenciálních párů a to přijímacího a vysílacího komunikačního páru označovaného jako Lane. Činnost vysílače i přijímače je na sobě nezávislá a Link tvoří plně duplexní komunikační kanál.

PCI-E link

-

Vrstvy sběrnice PCI-E

PCI-E je jako protokol založený na vrstvách, jejichž uspořádání a názvy jsou v jisté souvislosti se síťovým ISO-OSI (IEEE802 model of networking protocol) modelem známým z prostředí LAN sítí. PCI-E používá následující vrstvy:

- Transaction Layer (transakční vrstva)

- Data Link Layer (linková vrtva)

- Physical Layer (fyzická vrstva)

Vrstvy sběrnice PCI-E

Vrstvy sběrnice PCI-ETransakční vrstva

Nejvyšší vrstvou architektury je transakční vrstva. Tato vrstva je zodpovědná za zpracování (kompozici a dekompozici) paketů transakční vrstvy (Transaction Layer Packet - TLP). Tyto pakety nesou informaci o typu prováděné operace, jako je čtení, zápis, zpráva nebo operace s IO prostorem. Všechny pakety, které výžadují potvrzení jsou implementovány jako dvě transakce (request/completion) a jsou přijímány nebo posílaný do vrstvy core logic. Každý vysílaný paket má svoje identifikační číslo, aby cílové zařízení mohlo poslat completion transakci zdroji. Dále vrstva zajišťuje nastavování atributů, posílaní zpráv, které v podstatě realizují virtruální vodiče přerušení, řízení napájení, jak jsme je znali z jiných typů sběrnic.

Paket transakční vrstvy

Paket transakční vrstvy obsahuje hlavičku (TLP Header), přenášená data - pokud jsou požadována a nepovinný kontrolní součet ECRC. Hlavička se skládá především z řídících informací o typu přenosu.

Linková vrstva

Linková vrstva je vložená mezi transakční a fyzickou vrstvu. Jejím úkolem je zajišťování integrity dat - detekce a oprava chyb. Data přijatá z transakční vrstvy jsou opatřena kontrolním kódem, identifikačním číslem a poslána do fyzické vrstvy. Naopak data přijatá z fyzické vrstvy jsou otestována, zda neobsahují nějakou chybu a jsou poslána do transakční vrstvy. V případě výskytu chyby, vrstva zajišťuje opakovaný požadavek na data, dokud nejsou požadovaná data přitomná, nebo dokud není linka prohlášena za nefunkční. Paket linkové vrstvy

Paket linkové vrstvy

Fyzická vrstva

Fyzická vrstva se ještě dále dělí na logickou a elektrickou podvrstvu. Logická vrstva zabezpečuje PCS (Physical Coding Sublayer) a MAC (Media AccessCotrol).Model fyzické vrstvy sběrnice PCI Express vychází spíše ze sítí typu peer-to-peer než z architektury PCI nebo PCI-X. Jistá podobnost architektury PCI Express je i v dělení vrstev se síťovým modelem ISO-OSI. Architektura typu peer-to-peer umožňuje nezávislou komunikaci mezi jednotlivými zařízeními, kdy jedno zařízení nemusí čekat na uvolnění sběrnice při vzniku požadavku na komunikaci s jiným zařízením, jak tomu bylo u architektury PCI. Pochopitelně komunikace neprobíhá pouze jedním směrem, ale oběma - rozhraní je plně duplexní.

Fyzická vrstva zajišťuje veškeré obvody nutné pro připojení k linku. Jsou to fázové závěsy, buffery, sério-paralelní a paralelně sériové převodníky, impedanční přizpůsobení a v neposlední řadě i logiku pro inicializaci a udržování spojení na linku (vyjednání přenosové rychlosti, formátu přenosu dat). Tato vrstva je zodpovědná za komunikaci mezi linkem a linkovou vrstvou. Paket přijatý z linkové vrstvy LLTP je doplněn o kódy začátku konce paketu podobně, jako je tomu u síťových paketů (Ethernet). Dále je paket zakódován kódem 8 na 10. Tím jsou do paketu doplněny další informace zajišťující synchronizaci. Potom je paket převeden na sériový kód a odvysílán do příslušného Lanu. Přijímací část fyzické vrstvy postupuje opačným způsobem. Dekóduje přijatý paket na řídící kódy, data a rekonstruuje hodiny. Pokud je rámec paketu v pořádku a odpovídá kontrolní součet, je odeslán do linkové vrstvy, dále je také odesláno potvrzení o přijetí dat zdroji transakce, který vyprázdní retry buffer. Pokud přijdou data s chybou, odesílá se do zdrojového portu požadavek na opakování transakce.

Je nutno podotknout, že pokud dojde v budoucnu ke změně formátu kódování (64bitů na 66bitů) nebo rychlosti, je třeba změnit pouze fyzickou vrstvu a není nutné měnit žádnou jinou vrstvu modelu PCI Express.

Signály sběrnice PCI-E

Základem je Line sestavený ze dvou diferenciálních párů a to příjímacího a vysílacího. Sběrnice je poté pochopitelně doplněna o další pomocné a napájecí signály. Popis signálu konektoru PCI x 1 je v následující tabulce. Konektor pro verze x2, x4, x8 a x16 je rozšířen o další nože konektoru - obvykle o čtyři pozice, které obsahují GND a přijímací a vysílací pár. Implementace některých signálů není bezpodmínečně nutná a je pouze doporučena. Detailnější popis nalezne čtenář v literatuře uvedené na konci článku .

Číslo pinu

Strana A

Strana B

Název

Popis

Název

Popis

1

+12V

Napájení +12V

PRSNT1#

Detekce přítomnosti karty Hot-Plug

2

+12V

Napájení +12V

+12V

Napájení +12V

3

RSVD

Vyhrazeno pro budoucí použití

+12V

Napájení +12V

4

GND

Zem

GND

Zem

5

SMCLK

System Managenet Bus Clock

JTAG2

TCK, hodinový signál pro JTAG

6

SMDAT

System Management Bus Data

JTAG3

TDI, vstupní data pro JTAG

7

GND

Zem

JTAG4

TDO, výstupní data od JTAGu

8

+3,3V

Napájení +3,3V

JTAG5

TMS, výběr modu pro JTAG

9

JTAG1

TRST, reset JTAGu

+3,3V

Napájení +3,3V

10

3,3Vaux

Pomocné napájení 3,3V - pro wake-up

+3,3V

Napájení +3,3V

11

WAKE#

Signál pro reaktivaci zařízení z PWD

PERST#

Reset

12

RSVD

Vyhrazeno pro budoucí použití

GND

Zem

13

GND

Zem

REFCLK-

Referenční hodinový signál, negativní

14

PETp0

Vysílač - Lane 0 pozitivní

REFCLK+

Referenční hodinový signál, pozitivní

15

PETn0

Vysílač - Lane 0 negativní

GND

Zem

16

GND

Zem

PERp0

Přijímač - Lane 0 pozitivní

17

PRSNT2#

Detekce přítomnosti karty Hot-Plug

PERn0

Přijímač - Lane 0 negativní

18

GND

Zem

GND

ZemMechanické uspořádání PCI-E na základních deskách

V současné době dochází u základních desek k přechodu od standardu PCI ke standardu PCI-E, obdobně jako tomu bylo u rozhranní ISA a PCI. Doporučené mechanické uspořádání je na následujícím obrázku.

Mechanické uspořádání PCI-E

Mechanické uspořádání PCI-E

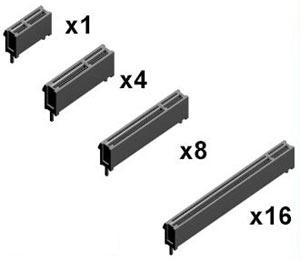

Fyzické provedení PCI-E slotů (od shora: 1x ? 2,5Gbps, 4x ? 10Gbps, 8x - 2GBps, 16x ? 3,2GBps)

Fyzické provedení PCI-E slotů (od shora: 1x ? 2,5Gbps, 4x ? 10Gbps, 8x - 2GBps, 16x ? 3,2GBps)

Rozměry přídavných karet by měly splňovat některá omezení. Maximální povolené rozměry jsou uvedeny následující tabulce.

Šířka linku

Typ karty

Výška karty

Šířka karty

x1

Standardní karty poloviční délky

111.15 mm (max)

167,65 mm (max)

x1,x4,x8,x16

Standardní karty plné délky

111.15 mm (max)

312 mm (max)

x1,x4,x8,x16

Karty s nízkým profilem

68,9 mm (max)

167,65 mm (max)Závěr

Článek měl v krátkosti představit sběrnici PCI-E, která je v současné době používána především u grafických karet - na trhu jsou ovšem pochopitelně i zvukové, síťové a další karty pro PCI-E. V některém z dalších článku budou představeny speciální karty pro bezpečnostní video aplikace určené pro sběrnici PCI-E.

Použitá literatura

- Některé obrázky,část textu a především tabulky byly se svolením převzaty ze serveru www.svethardware.cz .

- http://www.svethardware.cz/art_doc-66405A60712A7A6CC12570000046F535.html

- http://www.pcisig.com

- PCI Special Interest Group. PCI Local Bus Specification, rev 2.3, March 29, 2002. Dostupné na www.pcisig.com

- PCI Special Interest Group. PCI-X Protocol Addendum to the PCI Local Bus Specification Revision 2.0a. July 22, 2003. Dostupné na www.pcisig.com

- PCI Special Interest Group. PCI Express Base Specification Revision 1.0a. April 15, 2003. Dostupné na www.pcisig.com

- Edward Solari, Brad Congdom: The Complete PCI Express Reference Design Insights for Hardware and Software Developers. Intel Press 2003, ISBN 0-9717861-9-4

Komentáře

Chyba?

Dobry vecer. V textu je malicka chybka. Konkretne na radku s "16x - 3.2 GBps (obousměrně 6.4 Gbps) ". Je tam preklep s malym "b".

Děkuji za upozornění

Děkuji za upozornění, už je to opraveno.