Úvod:

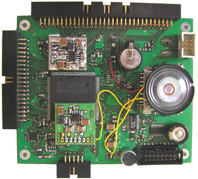

Cílem mé práce není navrhnout desku, která by se výpočetním výkonem vyrovnala PC nebo podobným zařízením, ale desku která by především byla schopna samostatně řídit různé typy displejů, byla vhodná k zástavbě do zařízení, byla by schopna komunikovat s jinými deskami a byla by vhodná pro připojení na sběrnici různých procesorů. Deska by měla umět zpracovat analogové či digitální signály, poslat je do PC, zapsat na SD kartu nebo zobrazit srozumitelným způsobem. Hlavní částí práce byl výběr vhodných součástek, návrh samotné desky v návrhovém prostředí pro plošné spoje (Eagle) a samotné osazení a oživení desky. Neméně důležitou částí bylo vytvoření ukázkového programu pro AVR a FPGA. Mým cílem v budoucnu je připojit k desce digitální obrazový snímač a s pomocí desky uložit jeho obraz do SD karty, nejlépe jako video sekvenci se zvukem, nebo jej rozhraním RS485 poslat do jiné desky.

Seznam použitých zkratek a symbolů:

- !- vstup (výstup) aktivní v logické nule

- BRAM - Block RAM, dvoubránová paměť v hradlovém poli, konfigurovatelná pro různou šířku datové sběrnice a různou hloubku

- LUT - look-up table, základní funkční element v hradlovém poli, vytvářející logickou funkci, v řadě XC3SxxxE je to rychlá čtyřvstupová SRAM

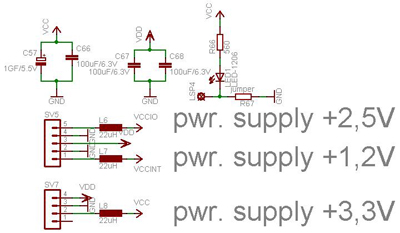

- VCC - napájecí napětí +3,3V

- VCCINT - napájecí napětí +1,2V

- VCCIO - napájecí napětí +2,5V

- VDD - napájecí napětí +5V

Požadavky na použité obvody a jejich volba:

Mojí snahou bylo použít co nejlépe dostupné součástky a to takové, které se dají koupit přímo v některé z prodejen v Praze a nebo na objednávku, ale ne s dodací lhůtou řádově měsíců nebo s minimálním objednacím množstvím stovek kusů. I přes tento požadavek jsem na desce použil některé exotičtější součástky z důvodu jejich speciálních parametrů. Konstrukce desky je modulární, deska na sobě nemá stabilizátory napětí, ale má pro ně otvory pro připájení. Je to proto, že deska má hustotu páté konstrukční třídy, ale zdroj lze navrhnout v nižší třídě, která je levnější. Dále je to také proto, že se mi nezdálo nejvhodnější navrhnout desku závislou na konkrétním stabilizátoru a zvláště proto, že výrobci inovují a časem nabídnou novější stabilizátory s lepšími parametry a vyšší účinností, než jsou k dispozici dnes.

Vzhledem k tomu, že různí výrobci požívají na svých displejích různé konektory, vybral jsem univerzální konektor pro propojení s displejem s rozumnou roztečí, který se dá bez problémů zapájet a pro který se dá v domácích podmínkách vyrobit konektorová redukce pro příslušný displej. Na tento konektor lze také připojit i jiná zařízení, např. digitální obrazový senzor apod.Pokud by bylo potřeba k desce připojit standardní LCD monitor, lze vytvořit desku, která na sobě bude mít DA převodníky a oddělovací obvody.

Výběr výrobce hradlového pole byl jednoduchý, protože v zaměstnání programuji hradlová pole firmy Xilinx a mám je v oblibě a také protože navrhový systém je pro vybrané obvody zdarma ke stažení na internetu, zvolil jsem právě výrobce Xilinx. Dalším krokem bylo vybrat vhodný typ hradlového pole. Kritériem pro výběr byla jeho velikost (počet LUT, BRAM apod.), počet I/O vývodů, typ konfigurační paměti, typ pouzdra a cena. Snahou bylo použít obvod, který má konfigurační data uložena v paměti, kterou lze jednoduše programovat z připojeného procesoru. Protože použití paměti programované prostřednictvím rozhraní JTAG se mi zdálo poněkud těžkopádné, zvolil jsem obvod, který má konfigurační data uložena v SPI paměti. Dalším krokem bylo vybrat vhodný řídicí procesor, kritériem pro jeho výběr byl počet I/O vývodů, velikost jeho pamětí, dostupnost vývojových prostředků a jeho rozšířenost mezi konstruktéry elektronických zařízení. Zpočátku jsem uvažoval o rychlejším procesoru typu ARM, ale ten není tolik rozšířený a seznamování se s vývojovým prostředím pro tento procesor by zabralo příliš mnoho času. Proto jsem zvolil známější mikrokontrolér rodiny AVR.

Dalším krokem bylo vybrat vhodný řídicí procesor, kritériem pro jeho výběr byl počet I/O vývodů, velikost jeho pamětí, dostupnost vývojových prostředků a jeho rozšířenost mezi konstruktéry elektronických zařízení. Zpočátku jsem uvažoval o rychlejším procesoru typu ARM, ale ten není tolik rozšířený a seznamování se s vývojovým prostředím pro tento procesor by zabralo příliš mnoho času. Proto jsem zvolil známější mikrokontrolér rodiny AVR.

U zvukového kodeku jsem chtěl, aby to nebyl pouze AD a DA převodník, ale aby měl také mikrofonní zesilovač. Vzhledem k tomu že v mém okolí se již jeden typ kodeku objevil, použil jsem stejný typ, ale s napájecím napětím 3V. Tento typ zvukového kodeku se ukázal výhodným také proto, že má zabudovány vnitřní filtry a nastavitelné vstupní a výstupní zesilovače. Výstupní zesilovače pro reproduktory jsem chtěl co nejúčinnější a proto jsem vybral nejdostupnější obvody ve třídě D.

Dále jsem chtěl, aby deska obsahovala nějakou paměť RAM, ve které by mohla být uložena data nejen pro zobrazení. Statickou RAM jsem zavrhl z důvodu velkého počtu adresových vývodů i při její relativně malé kapacitě a také kvůli její velké proudové spotřebě. Lepší paměť se jevila buď paměť SDRAM nebo DDR SDRAM, ale vzhledem k tomu, že paměť DDR SDRAM má jiné napájecí napětí než ostatní obvody na desce, zvolil jsem paměť SDRAM.

Protože při oživování a používání desky jsou potřeba ovládací prvky jako tlačítka nebo klávesnice, umístil jsem na desku expander portů. Dále jsem chtěl, aby deska měla obvod reálného času a proto jsem vybral nejdostupnější a nejpřesnější, který byl v době návrhu na trhu. Dalším požadavkem bylo, aby deska měla analogový vstup pro připojení analogového signálu, např. ČB kamery. Vybral jsem obvod s nejmenším počtem vývodů a s malou spotřebou.

Popis funkčních částí desky:

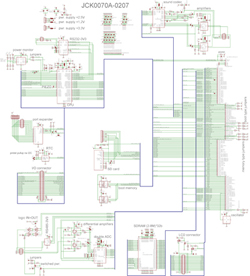

V této kapitole jsou popsány jednotlivé funkční části desky. Značení konektorů je převzato z katalogu firmy GM electronics. V textu, kde jsou uvedeny hodnoty součástek, jsou vybrány typické hodnoty z katalogového listu. Ve schématu je FPGA (IC4) typ XC3S250E místo XC3S500E, protože v knihovně Eagle mám pouze XC3S250E. Tato skutečnost nevadí, protože oba typy mají stejné rozložení vývodů. Pro lepší orientaci jsou v částech schématu umístěny obrázky konektorů při pohledu shora, dále jsou zde některé pomocné texty napsány anglicky, protože české označení je oproti anglickému poněkud těžkopádné a anglické označení bývá známější nebo výstižnější.

FPGA (IC4)

Použité FPGA je typ XC3S500E-5PQG208C v pouzdru PQFP208, výrobce Xilinx. Tento obvod je srdcem celé desky a je připojen na I/O a LCD konektor, AVR, SPI a SDRAM paměť, AD převodník, logický vstup a výstup, ADM3485 a zvukový kodek. Jeho (vybrané) parametry jsou:

- ekvivalentní počet hradel - 500 000

- počet LUT – 9312

- počet BRAM - 20 (kapacita jedné BRAM je 18Kbit)

- počet I/O vývodů – 126

- počet vstupních vývodů - 32

Propojky R37-R39 určují způsob konfigurace FPGA. Propojky R34-R36 vybírají typ konfigurační SPI paměti pro FPGA. Propojky R70/R71 zapínájí/vypínají pullup rezistory na vývodech FPGA během konfigurace. Rezistory R2 - R4, R16 - R18 a R69 oddělují vývody FPGA od propojek a umožňují tak FPGA, po nakonfigurování, měnit stav na těchto vývodech, nezávisle na propojkách.

Pull Up rezistory:

- R27 je pullup rezistor detekce přítomnosti SD-karty v konektoru

- R30 je pullup rezistor pro deaktivaci ADM3485 při konfigurování FPGA

- R55 je pullup rezistor pro detekci WP (zákaz zápisu - spínač na SD-kartě) SD-karty

- R72 je pullup rezistor pro deaktivaci SPI paměti při konfigurování FPGA

Rezistor R68 převádí 3,3V signál z AVR na 2,5V signál pro FPGA. Kondenzátor C79 slouží k odfiltrování případného rušení. Dva I/O vývody FPGA jsou vyvedeny na prokovy LSP2 a LSP3 a jsou použity při oživování desky nebo pro jiný účel. Jako zdroj hodinového taktu pro FPGA je použit oscilátor SG8002, firmy EPSON, pro napájecí napětí 3,3V a naprogramovaný na výstupní frekvenci 50 MHz. Schéma zapojení FPGA ke konektorům je popsáno v originální bakalářské práci, která je umístěna v odkazech.

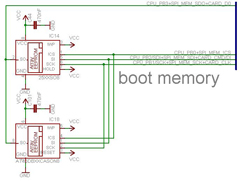

Konfigurační paměť (IC14 nebo IC18) pro FPGA

Použitá SPI paměť je řady 25XX nebo řady AT45DBXX výrobce Atmel (pouze jedna nebo druhá, nikdy ne zároveň obě !!!) o kapacitě 4Mbity (pro XC3S250 je dostatečná kapacita 2Mbity), obě v pouzdru SO8 nebo se stejnou roztečí vývodů. Je připojena k AVR tak, aby do/z ní mohlo AVR zapisovat/číst data prostřednictvím SPI rozhraní a je také připojena na I/O konektor, jehož prostřednictvím ji lze programovat/číst. Zapojení viz. níže.

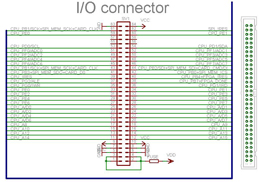

I/O konektor (SV1)

Tímto konektorem je napájena celá deska a je na něj přivedena datová / adresová sběrnice AVR, některé další porty AVR, některé vývody FPGA, SPI rozhraní pro programování AVR a konfigurační paměti FPGA, I2C rozhraní. Jeho čtyři piny nejsou zapojeny, a lze na ně v případě potřeby připojit potřebné signály. Konektor je typ MLW64G (přímý) nebo typ MLW64A (zahnutý o 90°).

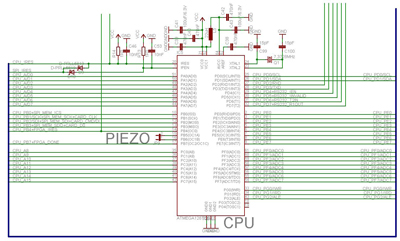

Mikrokontrolér (IC5)

Použitý mikrokontrolér je typ ATMEGA128L rodiny AVR v pouzdru TQFP64, výrobce Atmel. Suffix L znamená, že mikrokontrolér je určen pro napájecí napětí 2,7V - 5,5V a frekvenci hodinového taktu max. 8 MHz. Jeho (vybrané) parametry jsou:

- frekvence vnitřního taktu - 1/2/4/8 MHz /

- frekvence externího taktu - 0-8 MHz (pro komunikaci rozhraním RS232 je nejvhodnější použít externí krystal s frekvencí rovnou násobku baudové rychlosti, např. 7,3728 MHz)

- vnitřní programová a datová FLASH - 128 kB

- vnitřní datová EEPROM - 4 kB

- vnitřní datová SRAM - 4 kB

- externí paměťový prostor - až 64 kB

I/O porty AVR jsou použity následovně:

PORTA - LSB část adresové / datové sběrnice, připojen na FPGA a na I/O konektor

- PA0-PA7 = AD0-AD7

- PB0 = !CS pro konfigurační SPI paměť, připojen na I/O konektor

- PB1 = SCK pro SPI rozhraní a SD-kartu, připojen na I/O konektor

- PB2 = SDI pro SPI rozhraní a DI/CMD SD-karty, připojen na I/O konektor

- PB3 = SDO pro SPI rozhraní a DO SD-karty, připojen na I/O konektor

- PB4 = !PROGRAM pro FPGA - vymazání aktuálního obsahu FPGA a jeho rekonfigurace, připojen na I/O konektor

- PB5 = PWM výstup OC1A pro piezoměnič

- PB6 = PWM výstup OC1B pro piezoměnič

- PB7 = signál DONE z FPGA - informace, že FPGA načetlo konfigurační data z SPI paměti, připojen na I/O konektor

PORTC - MSB část adresové sběrnice, připojen na FPGA a na I/O konektor

- PC0-PC7 = A8-A15

- PD0 = SCL rozhraní I2C

- PD1 = SDA rozhraní I2C

- PD2 = RxD rozhraní RS232

- PD3 = TxD rozhraní RS232

- PD4 = !EN obvodu MAX3223E

- PD5 = !INVALID z obvodu MAX3223E

- PD6 = výstup rozhraní RS232, pro libovolné použití, např. řízení toku dat

- PD7 = vstup rozhraní RS232, pro libovolné použití, např. řízení toku dat

PORTE - připojen na FPGA a na I/O konektor, s aktuálním programem je použit jako MSBčást datové sběrnice (D8-D15)

PORTF - libovolné použití, také zastává funkci analogových vstupů, připojen na I/O konektor

PORTG - řídicí signály, část připojena na I/O konektor

- PG0 = !WR, připojen na I/O konektor

- PG1 = !RD, připojen na I/O konektor

- PG2 = ALE, připojen na I/O konektor

- PG1 = nezapojen

- PG2 = nezapojen

Piezoměnič je připojen mezi dva PWM výstupy, které s aktuálním programem běží v protifázi, a má proto dvakrát vyšší hlasitost, než při běžném připojení mezi výstup a GND (VCC). Signál SPI_!RES z I/O konektoru slouží k resetování a uvedení AVR do programovacího módu. Pokud je tento signál držen na log. nule při připojení desky na napájecí napětí, pak se AVR pomocí signálu !PEN uvede do programovacího módu a zůstává v něm trvale až do odpojení napájecího napětí. Když není osazena dioda D10, stejnou funkci zastává signál !RES, ale po deaktivaci SPI_!RES se ihned spustí běh programu AVR. Dioda D9 od sebe odděluje AVR vstupy !RES od !PEN a také vytváří z push-pull signálu SPI_!RES signál s vlastnostmi otevřeného kolektoru, aby se dalo AVR resetovat signálem z MAX6714. Kondenzátory C46 a C53 slouží k odfiltrování případného rušení.

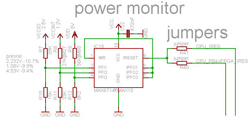

Resetovací obvod (sledovač napájecích napětí - IC15)

Použitý obvod je typ MAX6714 v pouzdru mMAX10, výrobce Maxim. Tento obvod sleduje velikost napájecích napětí VCC, VDD, VCCINT, VCCIO a při jejich poklesu resetuje AVR nebo FPGA výstupem !RESET. Jaký obvod bude resetován se určuje propojkami R40/R41. Odporové děliče R7/R10, R8/R11, R9/R12 určují velikost napěťového prahu. Poklesem napětí pod rozhodovací úroveň (podle kat. listu 0,62V) na vstupu PFI1 (PFI2 nebo PFI3) se aktivuje !PFO1 (!PFO2 nebo !PFO3. Výstupy !PFOx mají otevřený kolektor a jsou připojeny na !MR (převzato z kat. listu).

Použitý obvod je typ MAX6714 v pouzdru mMAX10, výrobce Maxim. Tento obvod sleduje velikost napájecích napětí VCC, VDD, VCCINT, VCCIO a při jejich poklesu resetuje AVR nebo FPGA výstupem !RESET. Jaký obvod bude resetován se určuje propojkami R40/R41. Odporové děliče R7/R10, R8/R11, R9/R12 určují velikost napěťového prahu. Poklesem napětí pod rozhodovací úroveň (podle kat. listu 0,62V) na vstupu PFI1 (PFI2 nebo PFI3) se aktivuje !PFO1 (!PFO2 nebo !PFO3. Výstupy !PFOx mají otevřený kolektor a jsou připojeny na !MR (převzato z kat. listu).

Jeho log. nulou se aktivuje výstup !RESET na min. 140ms. Výstup !RESET se také aktivuje poklesem VCC pod úroveň danou použitým obvodem (MAX6714CUB 3.3V-10%, MAX6714DUB 3.3V-5%). Napájecí napětí VCC se sleduje vždy (je to hlavní napájecí napětí), sledování ostatních se dá vyřadit vhodnou volbou odporových děličů, nebo přeškrábnutím příslušného spoje !PFOx do !MR na desce.

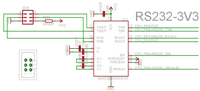

Rozhraní RS232 (IC1 + SV9)

Použitý obvod je typ MAX3223E v pouzdru SSOP20, výrobce Maxim. Je určen pro napájecí napětí 3 - 5,5V (na této desce má napájení 3,3V) a převádí signály TTL (LVTTL) na signály o napěťových úrovních RS232. Tento obvod automaticky vypíná RS232 výstupy, když na jeho RS232 vstupy není připojena platná logická úroveň, tuto skutečnost signalizuje výstupem !INVALID. Také má vestavěnou vnitřní ochranu proti elektrostatickému výboji až do 15kV (Human Body Model). Konektor je typ MLW06G (přímý) nebo typ MLW06A (zahnutý o 90°).

Použitý obvod je typ MAX3223E v pouzdru SSOP20, výrobce Maxim. Je určen pro napájecí napětí 3 - 5,5V (na této desce má napájení 3,3V) a převádí signály TTL (LVTTL) na signály o napěťových úrovních RS232. Tento obvod automaticky vypíná RS232 výstupy, když na jeho RS232 vstupy není připojena platná logická úroveň, tuto skutečnost signalizuje výstupem !INVALID. Také má vestavěnou vnitřní ochranu proti elektrostatickému výboji až do 15kV (Human Body Model). Konektor je typ MLW06G (přímý) nebo typ MLW06A (zahnutý o 90°).

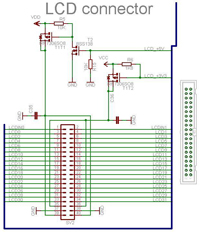

LCD konektor (SV2)

Tento konektor je připojen na 2 vstupní a 32 I/O vývodů FPGA, je jím napájen a řízen připojený displej, lze ho ale použít i pro jiné účely. Napájení displeje se zapíná pomocí tranzistorů T1T1, T1T2 a T2, které jsou řízeny pomocí FPGA. T1T1 a T1T2 jsou dva tranzistory PMOS v jednom pouzdru SO8, mohou být i jiný typ než je ve schématu, ale s co nejmenším odporem v sepnutém stavu (RDSON) a spínající při malém napětí (5 V). T2 je libovolný, pinově kompatibilní, NMOS tranzistor spínající při malém napětí (3,3 V). Rezistory R5, R6 a R15 drží tranzistory zavřené během načítání konfiguračních dat obvodem FPGA. Konektor je typ MLW40G (přímý) nebo typ MLW40A (zahnutý o 90°).

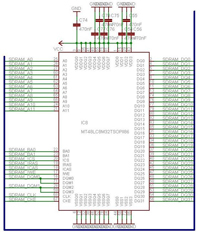

Paměť SDRAM (IC8)

Deska je navržena pro paměť MT48LC8M32 v pouzdru TSOP 86, výrobce Micron. Je to paměť typu SDRAM o kapacitě 8M * 32b, pro frekvenci až do 166 MHz. Lze použít i paměti s menší kapacitou, jiných výrobců i jiných rychlostí, měly by být pinově kompatibilní, ale vždy je to třeba před osazením zkontrolovat. Šířka datové sběrnice byla zvolena 32 bitů z důvodu rychlejšího přístupu do paměti např. při použití displeje s vyšším počtem barev než 16 bitů. Čtyři vstupy DQM0-3 pro povolení jednotlivých bytů jsou, kvůli nedostatku I/O vývodů FPGA, po dvojicích spolu propojeny. Všechny ostatní řídicí, adresové a datové vývody paměti jsou připojeny na FPGA.

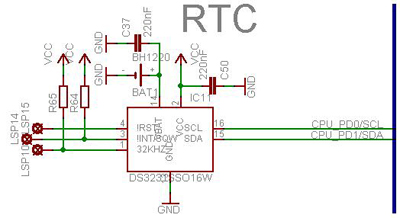

RTC (obvod reálného času - IC11)

Použitý obvod je typ DS3231 v pouzdru SO16W, výrobce Maxim. Tento obvod se sám přepíná na záložní baterii při poklesu napájecího napětí, má vnitřní teplotně kompenzovaný krystal a pravidelně provádí kalibraci jeho frekvence. Je připojen na rozhraní I2C a některé jeho vývody jsou vyvedeny na prokovy LSP10, LSP14 a LSP15.

Paměťová SD-karta (SV10 nebo SV11)

SD-karta je připojena na SPI rozhraní (z důvodu úspory vývodů FPGA) a na FPGA. Napájení pro kartu se zapíná tranzistorem T5 spínajícím při malém napětí (3,3V), ten je při konfiguraci FPGA možno držet rozepnutý/sepnutý rezistorem R59/R54. Pro případ nedostupnosti konektoru SV10 (konektor pro SD-kartu), je na desce umístěn konektor SV11 pro připojení dostupnějšího konektoru. Proto jsou konektory SV10 a SV11 umístěny na desce přes sebe. Paměťová SD-karta je sice připojena na SPI rozhraní, ale na této desce se s ní dá komunikovat pouze pomocí FPGA. Může se to jevit jako nevýhoda, ale je třeba si uvědomit, že paměťová karta zvládá komunikaci na mnohem vyšší frekvenci (až 25 MHz) než běží AVR a než je vůbec schopno programově „mávat“ piny. Proto by byla škoda zpomalovat si s ní komunikaci připojením na samotné SPI rozhraní, a také proto, že karta zvládá komunikaci po čtyřech bitech, na rozdíl od jednobitového SPI rozhraní.

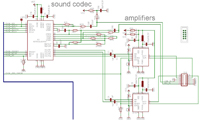

Zvuková část (IC3 + IC12 + IC13 + SV8)

Použitý kodek je typ AD73322L v pouzdru QSOP20, výrobce Analog Devices. Obsahuje vstupní a výstupní nastavitelné zesilovače, filtry a dva 16bitové AD a DA převodníky se vzorkovací frekvencí až 64kHz. Rezistory a kondenzátory, na které je přiveden linkový vstup, jsou propojeny univerzálně tak aby se dala použít různá zapojení podle kat. listu. Ve schématu, kde je u rezistoru napsáno např. 47K||100pF, je na rezistoru o hodnotě 47KΩ umístěn kondenzátor s kapacitou 100pF. Výstupní zesilovače jsou typ MAX9700 v pouzdru μMAX10, výrobce Maxim. Jsou to zesilovače třídy D s diferenciálními vstupy a výstupy. Napájení pro oba dva se vybírá propojkou R24 nebo R25 (5V nebo 3,3V , nikdy nezapojovat současně!!!). Propojkou JP3/JP4 nebo JP7/JP8 se vybírá modulační frekvence zesilovače. Konektor je typ MLW10G (přímý) nebo typ MLW10A (zahnutý o 90°).

Použitý kodek je typ AD73322L v pouzdru QSOP20, výrobce Analog Devices. Obsahuje vstupní a výstupní nastavitelné zesilovače, filtry a dva 16bitové AD a DA převodníky se vzorkovací frekvencí až 64kHz. Rezistory a kondenzátory, na které je přiveden linkový vstup, jsou propojeny univerzálně tak aby se dala použít různá zapojení podle kat. listu. Ve schématu, kde je u rezistoru napsáno např. 47K||100pF, je na rezistoru o hodnotě 47KΩ umístěn kondenzátor s kapacitou 100pF. Výstupní zesilovače jsou typ MAX9700 v pouzdru μMAX10, výrobce Maxim. Jsou to zesilovače třídy D s diferenciálními vstupy a výstupy. Napájení pro oba dva se vybírá propojkou R24 nebo R25 (5V nebo 3,3V , nikdy nezapojovat současně!!!). Propojkou JP3/JP4 nebo JP7/JP8 se vybírá modulační frekvence zesilovače. Konektor je typ MLW10G (přímý) nebo typ MLW10A (zahnutý o 90°).

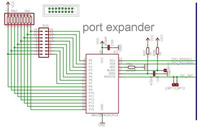

Expander pro klávesnici (IC2 + SV3)

Použitý obvod je typ MAX7314 v pouzdru QSOP24, výrobce Maxim. Je připojen na konektor SV3, FPGA a na rozhraní I2C. Tento obvod je na desce použit pro připojení ovládacích tlačítek nebo klávesnice. Lze s ním ovládat LED, měnit intenzitu jejich svitu lze, když je na jeho vstup BLINK připojen zdroj hodinového signálu. Vývody připojené na konektor lze nakonfigurovat jako vstupní, výstupní nebo s otevřeným kolektorem. U vstupních vývodů signalizuje změnu stavu výstupem !INT, pokud je tak nakonfigurován. Protože nezbyl vývod na AVR pro vyvolání přerušení, je vývod !INT připojen na FPGA. Konektor je typ MLW16G (přímý) nebo typ MLW16A (zahnutý o 90°).

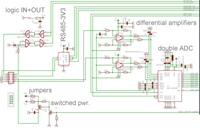

Diferenciální zesilovače (IC7 + IC10), AD převodník (IC6), logický vstup a výstup (IC17), rozhraní RS485 (IC16) a SV6

AD8137 jsou diferenciální zesilovače v pouzdru SO8, výrobce Analog Devices. Na této desce převádějí single-ended signál na diferenciální signál, který je následovně připojen na AD převodník MAX1193. MAX1193 je dvojitý AD převodník v pouzdru QFN28, výrobce Maxim. Tento převodník je připojen na FPGA. Jeho (vybrané) parametry jsou:

- dvojitý osmibitový AD převodník 45 MSPS

- diferenciální vstupy s napěťovým rozsahem ±0,512V

- multiplexovaný datový výstup

- nízká spotřeba 27 mA (standby 10 μA)

74AC132 slouží k bezpečnému oddělení FPGA od logických signálů na konektoru SV6. Zenerova dioda D1 omezuje napětí na vstupu 74AC132, rezistor R53 omezuje proud diodou D1. ADM3485 je převodník LVTTL signálu na diferenciální signál RS485 v pouzdru SO8, výrobce Analog Devices. Požít lze i rychlejší typ ADM3485E se zabudovanou ochranou proti elektrostatickému výboji. T4 je libovolný tranzistor NMOS, který spíná při 3,3V. T5 je tranzistor PMOS s malým odporem (RDSON), který spíná při 3,3V (5V - podle propojky). Propojka R32/R33 vybírá napětí, které bude připínáno na konektor SV6. Konektor je typ MLW10G (přímý) nebo typ MLW10A (zahnutý o 90°).

Ostatní:

Dioda LED je použita při oživování desky a lze ji připojit na FPGA. Do konektorů SV5 a SV7 se připojují napájecí moduly se stabilizátory napětí. Napájení desky je filtrováno tlumivkami L6 - L8 a kondenzátory v příslušné napájecí větvi.

Chyby na desce:

- Rozhraní I2C nemá pull-up rezistory

- Při oživování se ukázalo, že pro konfiguraci s FPGA resetovaným AVRkem je vhodnější FPGA držet resetované, protože jinak se po zapnutí snaží načíst konfigurační data a pokud je vymazáno AVR, tak to ruší jakoukoliv komunikaci programátoru s AVR nebo s SPI pamětí a oboje tak nelze nahrát.

- Pro konfiguraci, kdy je FPGA resetované samotným MAX6714, tato úprava neplatí.

Více informací o chybách a jejich řešení naleznete v originálu bakalářské práce jež je umístěna v odkazech.

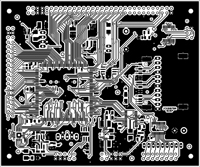

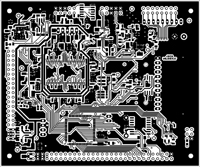

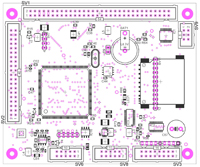

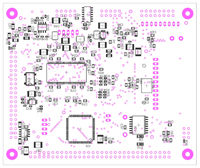

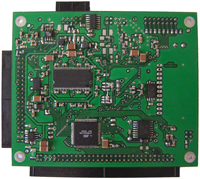

Spoje desky a rozmístění součástek na desce:

V této kapitole nejsou přiloženy obrázky vnitřních vrstev, protože nesdělují nějakou zásadní informaci. Pro doplňující informace se neváhejte obrátit na autora bakalářské práce, Pavla Košíka.

Software:

Popis programu pro FPGA:

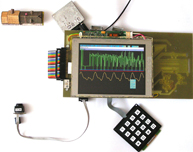

Program pro FPGA je vytvořen a přeložen v návrhovém systému ISE WebPACK, verze 8.2.03i, firmy Xilinx. Program pro FPGA je tvořen moduly, které jsou mezi sebou propojeny. Hlavní částí programu pro FPGA je řadič displeje, jeho součástí je znakový generátor s výběrem barvy pro písmo a pozadí, a generátor svislých čar (pro funkci osciloskopu). Jeho součástí je také funkce blikání znaku a „průhledná“ barva, která odkrývá data z SDRAM a generátoru čar.

Další modul je řadič paměti, který zapisuje data do SDRAM ze své FIFO a na požádání načítá obrazový řádek pro řadič displeje, v budoucnu i pro AVR. Zvukový modul posílá data ze své FIFO do zvukového kodeku a také je z něj příjímá do své druhé FIFO, do obou pamětí FIFO má přístup AVR. AD modul slouží k oddělení jednotlivých kanálů z AD převodníku. Video modul dekóduje obrazový signál z AD modulu a žádá řadič paměti o jeho zápis do SDRAM. Jednotlivé moduly jsou o rozsahu 50 - 500 řádek zdrojového kódu.

Popis programu pro AVR:

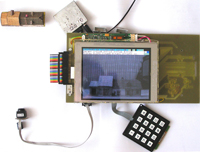

Program pro AVR je vytvořen a přeložen v návrhovém systému AVR studio, verze 4.13.528, firmy Atmel, s nainstalovaným překladačem WinAVR pro jazyk C. Program pro AVR je napsán v programovacím jazyce C. Hlavní částí programu je menu, ze kterého se spouštějí různé podprogramy. Program se ovládá klávesnicí připojenou na konektor SV3. Podprogramy vykonávají různé funkce, např. nastavují čas obvodu RTC, přehrávají ukázkový zvuk, zobrazují menu na displeji a nebo kreslí některé grafické symboly na displeji. Jednotlivé části programu AVR jsou v rozsahu 35 - 580 řádek zdrojového kódu.

Ukázky programu jak pro FPGA tak pro AVR je k nahlédnutí v originálu bakalářské práce.

Závěr:

Nejvíce času jsem strávil samotným vytvářením spojů desky v editoru plošných spojů (Eagle). Velkou část času jsem také strávil při tvorbě programu pro AVR a hlavně pro FPGA, asi nejsložitější bylo naprogramovat řadič paměti SDRAM. Možností pro vylepšení desky je několik, obvod ADM3485 má zbytečně připojeny tři vývody na FPGA, přestože stačí připojit pouze dva. Také paměť SDRAM má některé vývody zbytečně připojeny na FPGA a zbytečně mu tak vývody zabírá.

Samostatnou kapitolou pro vylepšování jsou programy, např. rychlost zápisu do SDRAM řadičem lze zvýšit. I v programu pro AVR lze udělat změny k lepšímu, ale tvorbu programového vybavení jsem si nekladl za hlavní cíl této práce, protože programové vybavení je vždy napsáno pro konkrétní zařízení, kde je umístěno. Části jako jsou RS485, RS232, SD-karta a logický vstup/výstup jsem nemohl z časových důvodů vyzkoušet, ale domnívám se, že jsou plně funkční. Funkci ostatních částí desky

jsem s úspěchem otestoval.

Na vzorové desky jsem připájel moduly se stabilizátory napětí, které jinde v textu neuvádím, protože je nepovažuji za přímou součást návrhu desky a předpokládám, že jejich popis později umístím na internet. Lze je nahradit lineárními stabilizátory, pokud odběr desky není příliš velký. Na fotografiích s displejem je vidět jednostranná deska, tu jsem vyrobil pro řízení dvou displejů, ale z časových důvodů jsem na ni umístil pouze jeden. Nepředpokládám, že bych ji s tímto umístěním řídicího konektoru ještě někdy vyráběl, raději bych ji někdy v budoucnu přepracoval.

Přílohy:

Odkazy & Download:

- http://www.analog.com/en/

- http://www.atmel.com/

- http://www.fairchildsemi.com/

- http://www.gme.cz/

- http://www.maxim-ic.com/

- http://www.micron.com/

- http://www.onsemi.com/

- http://www.sandisk.com/

- http://www.xilinx.com/

- Originál bakalářské práce , autor: Pavel Košík (*.pdf, 8,11MB)

Internetové stránky s návrhovými systémy

- http://winavr.sourceforge.net/

- http://www.atmel.com/

- http://www.xilinx.com/