FPGA hrají klíčovou roli v mnoha aplikacích, ale my se zaměříme na zpracování obrazu, kde lze využít strojové učení (ML) a umělou inteligenci (AI). FPGA je možné nakonfigurovat tak, aby poskytly několik vysokorychlostních rozhraní pro připojení kamery. FPGA používá vyhrazené logické cesty (pipeline), čímž se odstraní problematika sdílených zdrojů v klasickém řešení s CPU nebo GPU. Prakticky se podíváme na referenční aplikaci pro zpracování obrazu pomocí vývojové desky Ti180 M484 řady Titanium. Cílem je porozumět základním částem návrhu a identifikovat, kde technologie FPGA umožňuje odstranit problematické části návrhu nebo přináší značné výhody.

Referenční design na bázi Ti180 M484

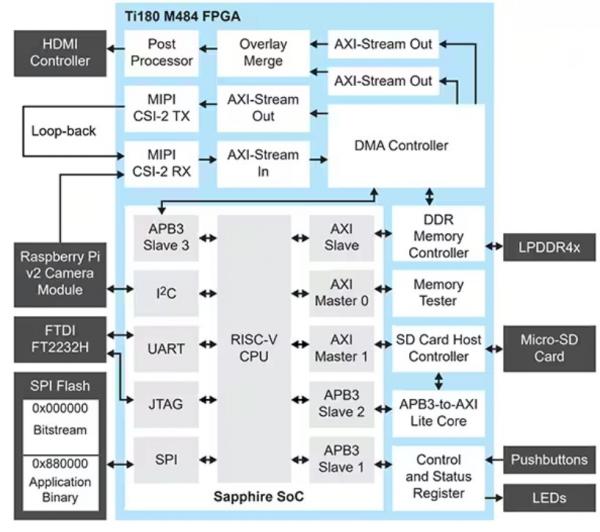

Referenční návrh (obrázek 1) přijímá snímky z několika kamer s rozhraním Mobile Industry Processor Interface (MIPI) a ukládá je do vyrovnávací paměti LPDDR4x. Poté je odesílá na displej skrz rozhraní High Definition Multimedia Interface (HDMI). Karta FPGA Mezzanine Card (FMC) a čtyři rozhraní Samtec QSE na desce slouží jako kamerové rozhraní HDMI.

Obrázek 1: Referenční design Ti180 M484 přijímá snímky z několika kamer MIPI, ukládá je do vyrovnávací paměti v LPDDR4x a poté je odesílá na displej přes HDMI. (Zdroj obrázku: Efinix)

Rozšiřující karta FMC to QSE se používá ve spojení s kartou HDMI k zajištění výstupní video cesty, zatímco tři konektory QSE se používají k propojení s kamerami DFRobot SEN0494 MIPI. Příjem více streamů MIPI s vysokým rozlišením (HD) a s vysokou frekvencí je však náročný. Zde je výhodná technologie FPGA, protože umožňuje paralelně využívat více MIPI streamů. Referenční návrh FPGA využívá jak paralelní, tak sekvenční struktury zpracování. Paralelní struktury se používají k implementaci pipeline pro zpracování obrazu, zatímco procesor RISC-V zajišťuje sekvenční zpracování používané pro vyhledávací tabulky LUT.

Pipeline pro zpracování obrazu lze rozdělit na dvě části, a to na vstupní a výstupní streamy. Vstupní stream je připojen k rozhraní kamery a výstupní stream je připojen k HDMI výstupu k displeji. Na vstupní pipeline jsou funkce pro vylepšení obrazu jako je například Bayerova konverze nebo automatická vyvážení bílé. Ve výstupním streamu dochází ke změně barev například z RGB na YUV a následném zpracování pro požadovaný výstupní formát jako je například HDMI.

Řetězec zpracování vstupního obrazu často pracuje s taktovací frekvencí snímače (kamery). Tato frekvence je ale odlišná od zobrazovací frekvence na výstupu. Vyrovnávací paměť LPDDR4x se používá jako mezičlánek vstupní a výstupní pipeline. Referenční design Ti180 používá podobné řešení. Pipeline pro zpracování vstupního obrazu implementuje jádro intellectual property (IP) MIPI Camera Serial Interface 2 (CSI-2), které je postaveno na I/O s podporou fyzické vrstvy MIPI (MIPI D-PHY). MIPI je výkonnostně náročné rozhraní, protože kromě nízkorychlostní a vysokorychlostní komunikace používá jak jednosměrnou, tak diferenciální komunikaci. Integrace fyzické vrstvy MIPI D-PHY do FPGA I/O významně snižuje složitost.

Referenční design převede obrazový stream z MIPI CSI-2 RX na stream AXI (Advanced eXtensible Interface). AXI Stream je jednosměrné vysokorychlostní rozhraní, které poskytuje tok dat z masteru na slave. Signály handshaking pro přenos mezi master a slave jsou přenášena spolu se signály postranního pásma. Tyto signály postranního pásma lze použít k přenosu informací o časování obrazu jako je začátek snímku a konec řádku. AXI Stream je ideální pro aplikace se zpracováním obrazu a umožňuje Efinix poskytovat řadu s funkcemi intellectual property IP, které pak lze snadno integrovat dle požadavků aplikace. Po přijetí jsou obrazová data MIPI CSI-2 a časovací signály převedeny na AXI Stream a vstupují do DMA modulu, který je zapisuje do LPDDR4x a funguje jako vyrovnávací paměť snímků.

Modul DMA pracuje pod kontrolou jádra RISC-V v systému Sapphire na SoC čipu. SoC řídí veškerý tok skrz DMA. Navíc poskytuje potřebné informace (adresa v paměti a informace o šířce a výšce obrázku definované v bajtech) pro správný zápis obrazových dat do LPDDR4x. Výstupní část čte obrazovou informaci z vyrovnávací paměti LPDDR4x pod přísnou kontrolou RISC-V SoC. Data jsou výstupem z DMA IP jako AXI Stream, který je poté převeden z formátu RAW do formátu RGB (obrázek 2) a připraven pro výstup přes integrovaný HDMI vysílač ADV7511 od Analog Devices.

Obrázek 2: Obrázky výstupu z referenčního návrhu. (Zdroj obrázku: Adam Taylor)

Díky DMA má Sapphire SoC RISC-V přístup k obrázkům uloženým ve vyrovnávací paměti a k to včetně abstraktním statistikám a informacím o snímcích. Sapphire SoC je také schopen zapisovat překryvy zpět do LPDDR4x, takže je lze sloučit s výstupním video streamem. Moderní obrazové snímače CMOS (CIS) mají několik provozních režimů a lze je nakonfigurovat přes I²C tak, aby poskytovaly několik různých výstupních formátů a snímkovací frekvence. V referenčním designu Efinix tuto komunikaci I²C s kamerami MIPI zajišťuje procesor Sapphire SoC RISC-V.

Integrace procesoru RISC-V do Titanium FPGA snižuje celkovou velikost finálního řešení, protože odstraňuje potřebu implementovat složité stavové stroje FPGA, které zvyšují riziko návrhu, tak externí procesory, které přidávají na ceně a složitosti. Procesor RISC-V lze využít pro komunikaci jádra intellectual property IP s kartou MicroSD. Díky tomu lze okamžitě vyhodnocovat, které snímky budou uloženy pro pozdější analýzu.

Celkově je architektura referenčního designu Ti180 optimalizována tak, aby umožnila kompaktní, levné, a přesto vysoce výkonné řešení. Referenční design slouží pro vytvoření vlastního hadrware, převzít kritické prvky a modifikovat je k potřebě dané aplikace.

Implementace

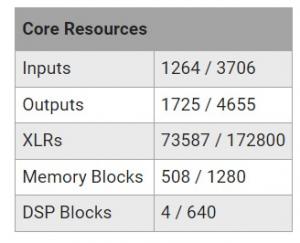

Jak bylo popsáno v Efinix FPGA pro AI/ML Imaging — Část 1: Začínáme, architektura Efinix je jedinečná v tom, že používá buňky eXchangeable Logic and Routing (XLR) k poskytování funkcí směrování i logiky. Video systém, jako je referenční design, je smíšený systém, který je náročný jak na logiku tak i na směrování. K implementaci funkcí zpracování obrazu je zapotřebí rozsáhlá logika a pro připojení IP buněk na požadovaných frekvencích je zapotřebí rozsáhlé směrování. Referenční návrh využívá přibližně 42 % XLR buněk v FPGA, a to ponechává dostatek prostoru pro další funkce a vlastní aplikace jako je například edge ML. Využití RAM bloků je jen ze 40 % a využití bloků DSP je jen pouze 4 ze 640 (obrázek 3).

Obrázek 3: Alokace zdrojů na architektuře Efinix ukazuje, že je využito pouze 42 % XLR buněk, a to ponechává dostatek prostoru pro další procesy. (Zdroj obrázku: Adam Taylor)

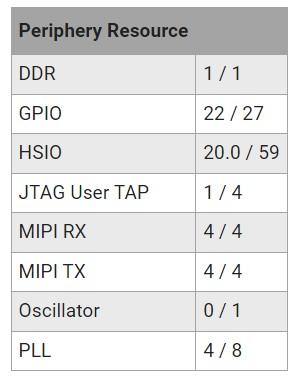

I/O FPGA používá rozhraní DDR k zajištění aplikační paměti pro SoC Sapphire a vyrovnávací paměti. Využívají se všechny kanály MIPI a 50 % smyček fázového závěsu PLL (obrázek 4).

Obrázek 4: Formát snímku využití I/O zdrojů. (Zdroj obrázku: Adam Taylor)

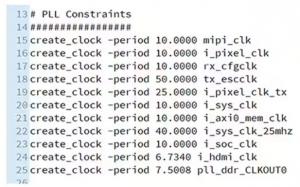

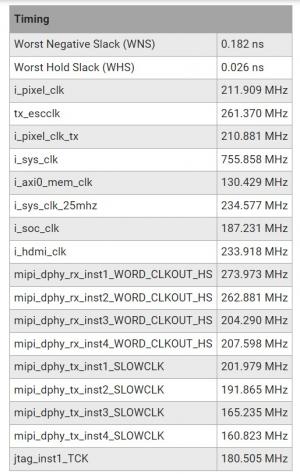

GPIO se používá k zajištění komunikace I²C spolu s několika rozhraními připojenými k Sapphire SoC jako je NOR FLASH, USB UART a SD karty. HSIO rozhraní se používá jako vysokorychlostní video výstup do vysílače HDMI ADC7511. V referenčním designu Ti180 se využívá několik hodin s různými vysokými frekvencemi. Finální tabulka časování ukazuje maximální frekvence dosažené pro hodiny v systému. V tabulce jsou uvedeny požadované hodiny pro konkrétní blok (obrázek 5). Například hodiny s frekvencí 148,5 MHz pro výstupní hodiny HDMI (Konstanta 6,734 i_hdmi_clock ).

Obrázek 5: Hodiny pro referenční návrh. (Zdroj obrázku: Adam Taylor)

Potenciál struktury Titanium FPGA XLR snižuje možné zpoždění směrování, a tím se zvyšuje celkový výkon (obrázek 6).

Obrázek 6: Potenciál struktury Titanium FPGA XLR snižuje zpoždění směrování, a tím zvyšuje celkový systému. (Zdroj obrázku: Adam Taylor)

Závěr

Referenční design Ti180 M484 ukazuje schopnosti Efinix FPGA. Návrh využívá několik jedinečných I/O struktur vhodné pro zpracování obrazu. Systém zpracování obrazu funguje pod kontrolou soft-core Sapphire SoC, který implementuje nezbytné prvky sekvenčního zpracování aplikace.

Článek vyšel v originále na webu DigiKey.com