FPGA hrají klíčovou roli v průmyslovém řízení, bezpečnosti, robotice, leteckém i automobilovém průmyslu. Poslední dobou se nejvíce FPGA používá v aplikacích strojového učení, kde se využívají náročné algoritmy pro zpracování obrazu. FPGA jsou totiž schopny zpracovávat data z několika vysokorychlostních kamerových rozhraní najednou. Klasická architektura FPGA s CBL (combinatorial logic blocks) nemusí mít dostačující výkon pro aplikace vyžadují strojové učení (ML) či umělou inteligenci (AI). Architektura Quantum od Efinix používá blok XLR (eXchangeable Logic and Routing), která je přímo určená pro aplikace s ML/AI. První díl pojednává o klíčových vlastnostech architektury Efinix FPGA, o použití v AI/ML a uvede její reálnou implementaci v praxi. Představíme si vývojovou desku a související nástroje, které usnadní začátky se zpracováním obrazu pomocí AI/ML.

Efinix FPGA

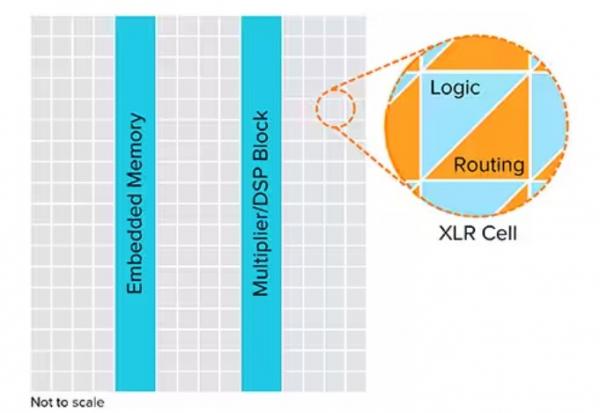

Efinix aktuálně nabízí dvě rodiny FPGA. První rodina Trion nabízí logickou hustotu od 4000 do 120 000 logických prvků (LE) a je vyrobena pomocí technologie SMIC 40LL. Nejnovější rodina Titanium nabízí logickou hustoty od 35 000 do 1 milionu logických prvků a je vyrobena na technologii TSMC 16 nm. Obě rodiny jsou založeny na architektuře Quantum, která je ve světě FPGA jedinečná. Standardní architektura FPGA je založena na logických blocích CLB (combinatorial logic blocks), které na se skládají z vyhledávací tabulky (LUT) a klopných obvodů. CLB implementují logické rovnice, které jsou následně propojeny pomocí směrování. Kvantová architektura Efinix je postavena na blocích XLR (eXchangeable Logic and Routing).

To, co dělá blok XLR jedinečným, že může být nakonfigurován tak, aby fungoval jako logická buňka s tabulkou LUT, registrem se sčítací jednotkou nebo směrovací maticí (routing matrix). Tento přístup nabízí jemnější architekturu, která poskytuje vyšší flexibilitu směrování a umožňuje implementace, které jsou náročné na logiku a výkon.

Obrázek 1: Blok XLR je jedinečný v tom, že může být nakonfigurován tak, aby fungoval jako logická buňka s tabulkou LUT, registrem se sčítací jednotkou, nebo jako směrovací matice. (Zdroj obrázku: Efinix)

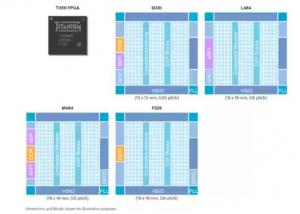

Nejnovější rodina FPGA Titanium nabízí nejpokročilejší funkce (obrázek 2) jako je jádro XLR, které je schopno poskytnout multigigabitové sériové linky, které pracují buď rychlostí 16 Gbps nebo 25,8 Gbps v závislosti na zvoleném typu. Tato multigigabitová spojení jsou klíčovým faktorem pro možnost vysokorychlostního přenosu dat na čipu i mimo něj.

Obrázek 2: Titanium FPGA Ti180 se dodává v různých variantách v závislosti na šířce sběrnice, I/O a požadavcích na paměť. (Zdroj obrázku: Efinix)

FPGA Titanium také poskytují širokou škálu vstupně-výstupních (I/O) rozhraní, které lze seskupit jako GPIO a které mohou podporovat jednostranné I/O standardy jako je nízkonapěťový CMOS ( LVCMOS) s úrovní napětí 3,3 V, 2,5 V a 1,8 V. Pro vysokorychlostní a diferenciální rozhraní Titanium nabízí HSIO, které podporuje standardy single-end I/O jako je LVCMOS s úrovní napětí 1,2 V, 1,5 V a SSTL a HSTL. Diferenciální I/O standardy podporované HSIO zahrnují také standard LVDS a diferenciální SSTL a HSTL.

Moderní FPGA vyžaduje úzce propojenou paměť s velkou šířkou pásma, která se používá k ukládání obrazových snímků pro aplikace se zpracováním obrazu, rychlé zpracování signálu a spuštění operačních systémů. Rodina Titanium poskytuje rozhraní DDR4 a nízkoenergetickou LPDDR4. V závislosti na přesně vybraném typu je podpora šířky sběrnice x32 (J) nebo x16 (M), některé typy ale nepodporují LPDDR4 (L).

FPGA Titanium jsou založeny na SRAM a vyžadují konfigurační paměť, přičemž konfigurace se provádí buď pomocí SPI nebo JTAG. Aby bylo zajištěno, že tato konfigurační metoda je bezpečná, používá Titanium FPGA šifrování AES GCM spolu s AES GCM a RSA-4096 k zajištění autentizace bitového toku. Silné zabezpečení je nutností, protože FPGA jsou nasazena tam, kde mohou mít přístup a manipulovat s jejich chováním neoprávněné osoby.

Vývojová deska

Vývojovou desku lze použít k prozkoumání schopností FPGA a k sestavení prototypových aplikací. První dostupná vývojová deska k zahájení stavby prototypu je Ti180 M484 (obrázek 3). Deska obsahuje konektor FPGA Mezzanine Card (FMC) a čtyři konektory Samtec QSE .

Obrázek 3: Ti80 M484 obsahuje Titanium FPGA, konektor FMC a čtyři konektory Samtec QSE. (Zdroj obrázku: Adam Taylor)

FPGA Ti180 osazené na této vývojové desce poskytuje 172 000 XLR buněk, 32 globálních hodin, 640 prvků digitálního zpracování signálu (DSP) a 13 Mb vestavěné paměti RAM. DSP poskytují násobení 18 x 19 s pevným bodem a 48 bitové násobení. DSP může být optimalizován pro operace s jednou instrukcí a více daty (SIMD - single instruction, multiple data) běžící v duální nebo čtyřnásobné konfiguraci. DSP lze také nakonfigurovat pro provádění operací s pohyblivou řádovou čárkou.

Jako většina vývojových desek, tak i vývojová deska Ti180 poskytuje jednoduché LED diody a tlačítka pro komunikaci s uživatelem. Jeho skutečná síla však spočívá v jeho rozmanitosti rozhraní. Vývojová deska Ti180 poskytuje konektor FMC s nízkým počtem pinů, který umožňuje připojení široké škály periferií. Protože se jedná o široce používaný standard, existuje mnoho karet FMC, které umožňují propojení vysokorychlostního analogově-digitálního převodníku (ADC), digitálně-analogového převodníku (DAC), síťových řešení nebo připojení paměti či úložišť. Kromě připojení FMC poskytuje deska čtyři konektory Samtec QSE, které umožňují přidat další rozšiřující karty. Konektory QSE se používají k poskytování vstupů a výstupů MIPI, přičemž každý konektor QSE poskytuje buď vstup nebo výstup MIPI.

Obrázek 4: Vývojová sada Ti180 M484 je zobrazena s možností rozšíření založených na konektorech QSE a FMC. (Zdroj obrázku: Adam Taylor)

Deska Ti180 poskytuje 256 Mbitů LPDDR4 paměti požadované v aplikacích pro zpracování obrazu či signálu. Vývojová deska navíc poskytuje řadu možností taktování, a to na 25, 33,33, 50 a 74,25 MHz, které lze použít se smyčkou fázového závěsu (PLL) pro generování různých vnitřních frekvencí. Schopnost přeprogramování se a možnost ladění tzv. online přímo na desce je důležitou funkcí pro vývoj. Toto ladění je možno provádět prostřednictvím rozhraní USB-C. K dispozici je také energeticky nezávislá paměť ve formě dvou 256 Mbit NOR flash, kterou lze použít k uložení konfigurace. Deska je napájena z 12 V univerzálního napájecího adaptéru, který je součástí balení. Součástí je také přerušení FMC-to-QSE s rozšiřujícími kartami QSE pro HDMI, Ethernet, MIPI a LVDS. Pro proniknutí do zpracování obrazu je k dispozici duální karta RPI a dvě karty fotoaparátu IMX477.

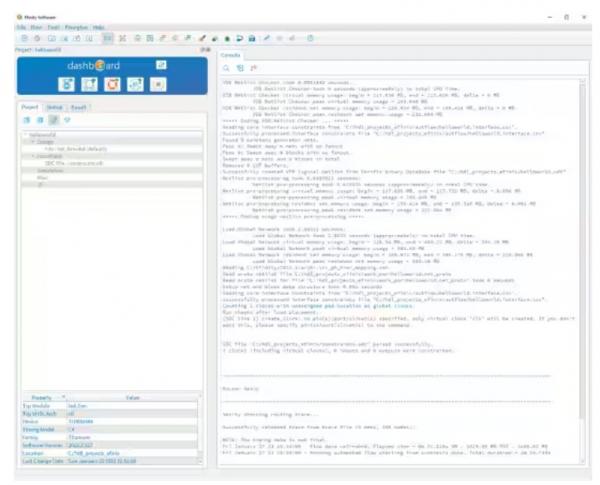

Softwarové prostředí

Implementační návrhy zaměřené na vývojovou desku Ti180 využívají Efinix software Efinity. Software umožňuje generování bitového toku prostřednictvím syntézy a funkce place and route. Poskytuje také vývojářům bloky intellectual property (IP), analýzu časování a ladění přímo na čipu. Pro získání přístupu k software Efinity je vyžadována vývojová deska. Na rozdíl od jiných dodavatelů však tento nástroj nemá různé verze, které vyžadují další licencování. V rámci Efinity vznikají nové projekty zaměřené na vybrané typy. Soubory RTL lze poté přidat do projektu a vytvořit omezení pro časování i návrh vstupů / výstupů, a to i s využitím HSIO, GPIO a specializovaných I/O.

Obrázek 5: V rámci Efinity se vytvářejí nové projekty zaměřené na vybrané typy FPGA. (Zdroj obrázku: Adam Taylor)

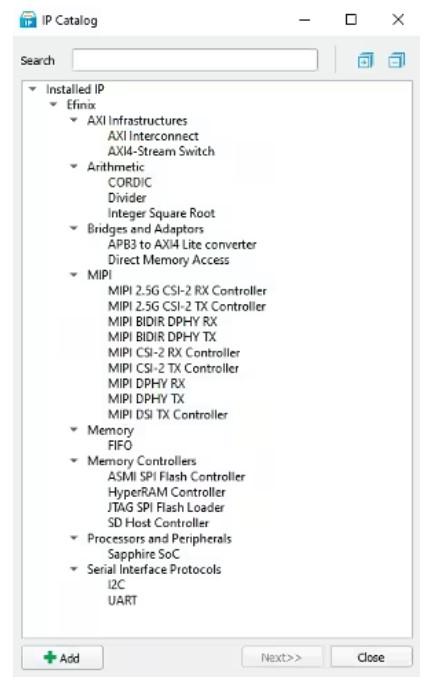

Důležitým prvkem návrhu FPGA je využití bloků intellectual property (IP), zejména pro komplexní IP jako je propojení AXI, řadiče paměti a softcore procesorů. Efinity poskytuje řadu bloků IP, které lze použít k urychlení celého návrhu.

Obrázek 6: Efinity poskytuje katalog IP, který lze využít k urychlení procesu návrhu. (Zdroj obrázku: Adam Taylor)

FPGA se většinou navrhují pro paralelní zpracování dat, ale někdy je důležité zhotovit strukturu FPGA jako procesor s tzv. měkkým jádrem (softcore). Tyto procesory se využívají pro sekvenční zpracování jako je síťová komunikace. Efinity poskytuje konfigurační nástroj Sapphire system-on-chip (SoC), aby bylo možné nasadit softcore procesory v FPGA Efinix. Sapphire umožňuje definovat víceprocesorový systém, který se skládá z mezipaměti i koherenci mezipaměti napříč více procesory s možností provozovat vestavěný operační systém Linux. V rámci Sapphire si lze vybrat mezi jedním a čtyřmi softcore procesory.

Implementovaným softcore procesorem je soft CPU VexRiscV, který je založen na architektuře instrukční sady RISC-V. Procesor VexRiscV je 32 bitová implementace, která má rozšíření pro zřetězení a nabízí sadu konfigurovatelných funkcí jako je multiplikátor, atomické instrukce, rozšíření s pohyblivou řádovou čárkou a instrukce pro komprimaci. V závislosti na konfiguraci systému SoC se výkon bude pohybovat mezi 0,86 a 1,05 DMIPS/MHz.

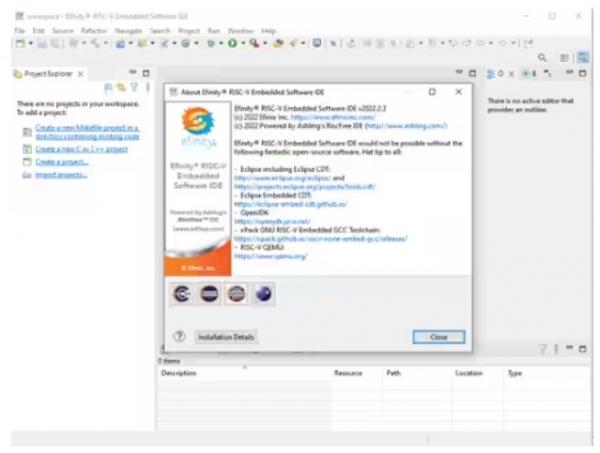

Jakmile je hardwarové prostředí navrženo a implementováno v FPGA Efinix, aplikační software může být vyvinut pomocí IDE Ashling RiscFree. Ashling RiscFree je založené na Eclipse, které umožňuje vytváření a kompilaci aplikačního softwaru s možností jemného doladění aplikace.

Obrázek 7: Ashling RiscFree je IDE založené na Eclipse, které umožňuje vytváření a kompilaci aplikačního softwaru s možností jemného doladění. (Zdroj obrázku: Adam Taylor)

Pokud se vyvíjí vestavěné linuxové řešení, jsou k dispozici všechny nezbytné artefakty spouštění, včetně zavaděče First Stage Boot Loader, OpenSBI, U-Boot a Linux pomocí Buildroot. Alternativně lze použít FreeRTOS, pokud je vyžadováno řešení v reálném čase.

Implementace AI

Implementace umělé inteligence je založena na softcore RISC-V. Využívá se schopnosti vlastních instrukcí procesoru RISC-V k integraci knihovny TensorFlow Lite. TensorFlow je bezplatná softwarová knihovna s otevřeným zdrojovým kódem pro strojové učení a umělou inteligenci. Použití procesoru RISC-V umožňuje uživatelům vytvářet vlastní instrukce, které lze použít před i po zpracování umělou inteligencí. Díky tomu lze vytvořit citlivější a propracovanější řešení.

Chcete-li začít s implementací AI, prvním krokem je prozkoumat Efinix model zoo. To je knihovna modelů AI/ML optimalizovaná pro koncová zařízení. Do modelu zoo lze přistupovat a trénovat pomocí Jupyter Notebooks nebo Google Colab. Jakmile je síť natrénována, lze ji převést z modelu s pohyblivou řádovou čárkou na kvantovaný pomocí převodníku TensorFlow Lite. Jakmile je ve formátu TensorFlow Lite, lze akcelerátor tinyML od Efinix použít k vytvoření hotového řešení pro architekturu RISC-V. Generátor tinyML umožňuje přizpůsobit implementaci a generovat klíčové soubory projektu. Při nasazení tímto způsobem se docílí akcelerace 4x až 200x v závislosti na zvolené architektuře.

Závěr

FPGA Efinix poskytují flexibilitu díky své jedinečné architektuře XLR. Toolchain poskytuje schopnost nejen implementovat RTL design, ale také implementovat komplexní SoC řešení, která nasazují softcore RISC-V procesory. Díky vysokému výkonu a dostupným knihovnám lze jednoduše implementovat umělou inteligenci a strojové učení například pro aplikace se zpracovaním obrazu.

Článek vyšel v originále na webu DigiKey.com