Toto eliminuje potřebu drahých obvodů jako VCXO/VCSO (Voltage Controlled Crystal Oscillator, Volatge Controlled SAW Oscillator), diskrétní součástky potřebné na filtr smyčky, multiplexory, hodinové buffery a převodníky úrovní. Cílovými aplikacemi by se měla stát zařízení, jako jsou:

- telefonní automaty,

- ethernetové aplikace,

- video a audio aplikace,

- vrátový a bezdrátový přenos dat.

Normálně by se použilo více PLL, jejich problém je, že jsou drahé a pracné na výrobu, pokud neobsahují žádné děličky, zvládají generovat pouze jeden přesný kmitočet, celkově prodlužují dobu vývoje zařízení a jsou s nimi spojeny i další nevýhody. Naproti tomu obvody řady Si53xx obsahují všechno potřebné a díky technologii DSP můžeme čerpat preciznosti PLL digitální cestou.

Konkurence

Konkurence

Pouze diskrétní a modulové analogové PLL založené na vysokofrekvenčních obvodech VCXO/VCSO mají porovnatelný jitter s obvody Si53xx. Silicon Labs tyto „neohrabané“ PLL nahradil jediným integrovaným obvodem, který podstatně zjednodušuje návrh obvodů, desek plošných spojů a s tím jde ruku v ruce i snížení šumu a náchylnosti na něj. Na obrázku vpravo je vidět zřejmý rozdíl mezi obvody Si53xx a standardním modulovým PLL.

Technologie DSPLL

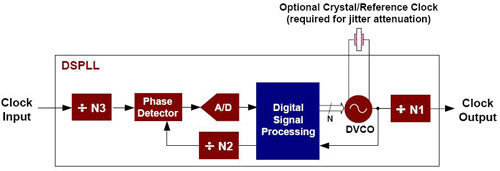

Jak je patrné na následujícím obrázku, architektura DSPLL využívá výhody digitálního zpracování signálu k vytvoření vysoce integrované PLL. V této PLL architektuře založené na DSP je výstup z detektoru fáze převeden na digitální formát pomocí vysoko rychlostního AD převodníku. Tato digitální data jsou poté zpracovávána pomocí rychlých DSP algoritmů.

Filtr smyčky je implementovaný digitálně, což znamená, že je frekvenční pásmo plně nastavitelné (programovatelné). Srdce technologie DSPLL tvoří nízko šumový, digitálně řízený vysokofrekvenční oscilátor DVCO, který zahrnuje jak perfektní parametry signálu (nízký jitter, stabilita, rozsah aj.), tak jednoduchost v nastavení potřebného kmitočtu.Přímým důsledkem je, že obvody řady Si53xx podporují široký rozsah vstupních a výstupních frekvencí, které by normálně vyžadovaly několik obvodů PLL (s VCXO nebo VCSO). Volitelný krystal nebo zdroj referenčního signálu je potřebný pro dosažení co nejnižšího jitteru (ustálení kvality signálu) a platí to pro obvody Si5316/23/26/66/68. Tato reference není potřeba pro jednodušší hodinové násobiče Si5322/25/65/67, které i tak mají velmi nízký a pro mnohé aplikace dostačující jitter.

Hlavní funkce a výhody:

Hlavní výhody jsou velice zjevné. Díky programovatelných frekvencím je možné použít referenčního designu pro více aplikací. Není již potřeba navrhovat složité PLL založené na VCXO/VCSO nebo pro tyto moduly mít na skladě ohromné množství součástek pro jednotlivé aplikace. Zkrátka a dobře pokud potřebujete zdroj hodinového signálu s volitelným kmitočtem a chcete návrh udržet co nejjednodušší, jsou pro vás obvody Si53xx tím pravým řešením.

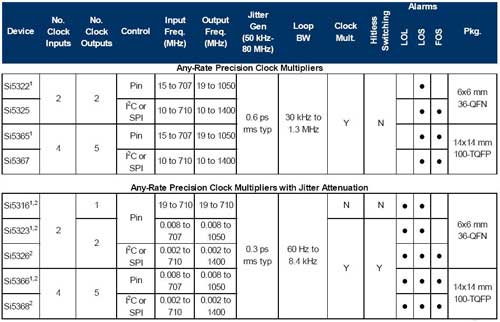

Obvody Si53xx disponují až 4 vstupy a 5 výstupy, každý může pracovat nezávisle na různých frekvencích. Tato úroveň integrace eliminuje potřebu po externích multiplexorech, bufferech a jiných součástek, které jsou jinak potřeba pro diskrétní PLL, modulové PLL a hodinové integrované obvody. V následující tabulce jsou uvedeny jednotlivé typy a jejich vlastnosti.

Díky interním výstupním bufferům, které si může uživatel nastavit na úrovně LVPECL, LVDS, CML nebo CMOS, odpadá potřeba externích převodníků úrovní. Toto ušetří cca 2-4 dolary na jedné aplikaci.

Frekvenční syntéza

Obvody Si53xx mohou generovat signál s rozsahem 2 kHz až 945 MHz (max. 1.4 GHz), a to z jakéhokoliv vstupního signálu z rozsahu 2 kHz až 710 MHz. Tato flexibilita jak v rozsahu vstupních, tak výstupních frekvencí umožňuje zjednodušit celkový návrh a pokryje rozmanité spektrum cílových aplikací.

Výhody integrovaného filtru smyčky:

- Zjednodušuje návrh PLL.

- Kmitočet smyčky může být změněn bez výměny komponent.

- Minimalizuje celkové rušení a citlivost na něj díky absenci diskrétních součástek.

Alarmové stavy

Obvody Si53xx podporují tři alarmové stavy – ztráta závěsu (LOL – loss of lock), ztráta vstupního signálu (LOS – clock loss of signal) a frekvenční kompenzace (FOS - frequency offset). Alarmové stavy LOL a LOS jsou užitečné pro precizní časové operace, zatímco alarm FOS je klíčovou vlastností v aplikacích SONET/SDH (optické sítě), kde se sleduje přesnost a kvalita frekvence. Tyto stavy jsou dostupné na výstupech obvodu pro použití v nadřazených systémech.

Zachování výstupní frekvence

Obvody Si5323/26/66/68 poskytují unikátní vlastnost umí totiž poskytovat přesný výstupní signál, i když je vstupní signál ztracen. Během této funkce DSPLL generuje výstupní frekvenci založenou na známé vstupní frekvenci, pro kterou má vyhrazený buffer, předtím než nastala tato situace.

Nízký jitter a hladina šumu

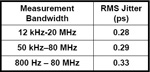

Násobiče frekvencí od Silicon Labs (obvody Si5316/23/26/66/68) poskytují jitter, který soutěží s těmi nejlepšími diskrétními PLL založenými na obvodech VCXO/VCSO. K dosažení těchto výsledků bylo zapotřebí integrovat všechny důležité součásti diskrétních PLL do jediného čipu, počínaje nízkošumovým VCO přes filtry smyčky, fázové detektory, děličky, konče výstupními buffery. V následující tabulce jsou uvedeny naměřené hodnoty.

Závěr:

![]() Obvody Si53xx od Silicon Labs disponují perfektními parametry a spojením technologií PLL a DSP vznikla řada absolutně unikátních obvodů, které najdou uplatnění v nejširším spektru aplikací. Obvody jsou dostupné buď v pouzře QFN (6x6 mm, 36 vývodů), nebo v pouzdře TQFP (14x14 mm, 100 vývodů). Pro přesnější informace navštivte domovské stránky společnosti Silicon Labs nebo oficiální stránky společnosti MES Praha s.r.o., která je také oficiálním distributorem součástek Silicon Labs v české republice.

Obvody Si53xx od Silicon Labs disponují perfektními parametry a spojením technologií PLL a DSP vznikla řada absolutně unikátních obvodů, které najdou uplatnění v nejširším spektru aplikací. Obvody jsou dostupné buď v pouzře QFN (6x6 mm, 36 vývodů), nebo v pouzdře TQFP (14x14 mm, 100 vývodů). Pro přesnější informace navštivte domovské stránky společnosti Silicon Labs nebo oficiální stránky společnosti MES Praha s.r.o., která je také oficiálním distributorem součástek Silicon Labs v české republice.

Odkazy & Download:

- Oficiální stránka výrobce - www.silabs.com

- Oficiální stránka společnosti MES Praha - www.mespraha.cz

- Přehled obvodů Si53xx (*.pdf, 1,2MB)