Článek volně navazuje na předchozí příspěvek o nových hradlových polích FPGA pro 3.2 Gbps, které vhodným způsobem podporuje a doplňuje součástkovou základnu. Bez precizního taktování to zkrátka nejde ani na nepoměrně nižších přenosových rychlostech.

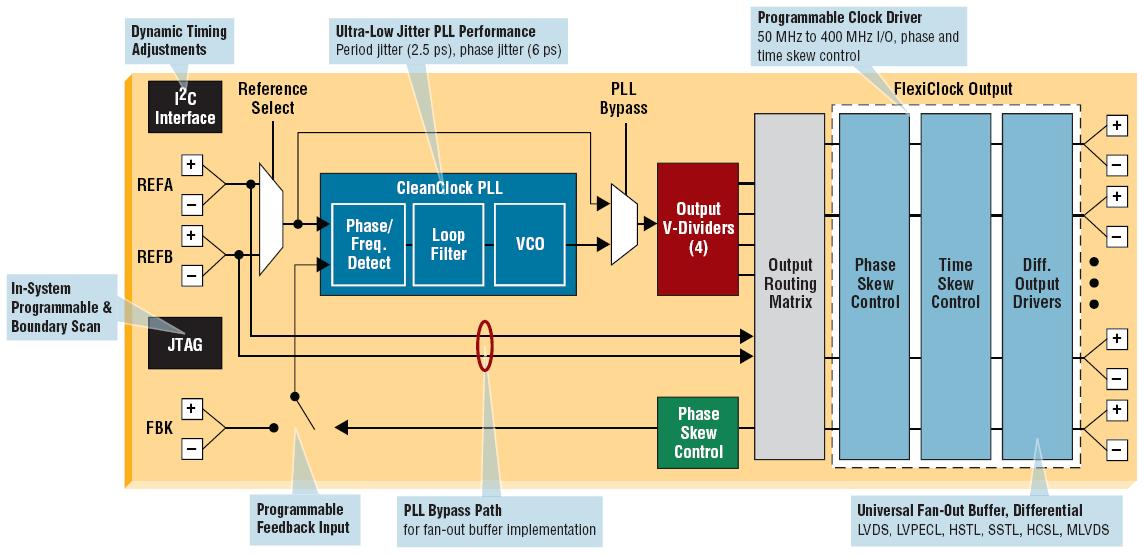

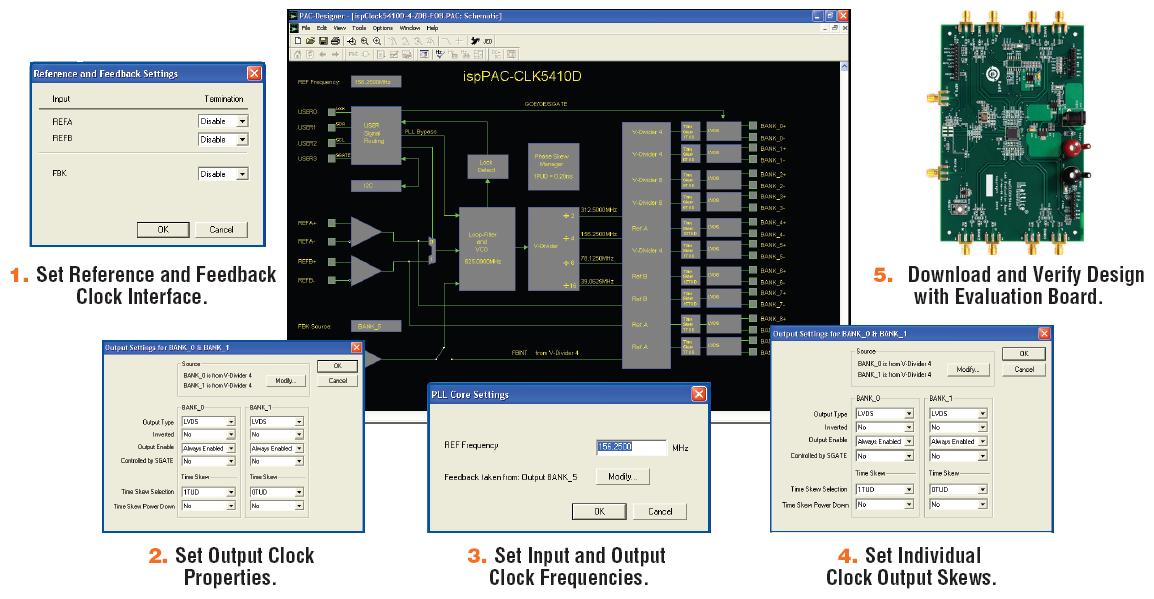

Blokový diagram rodiny obvodů ispClock5400D od Lattice

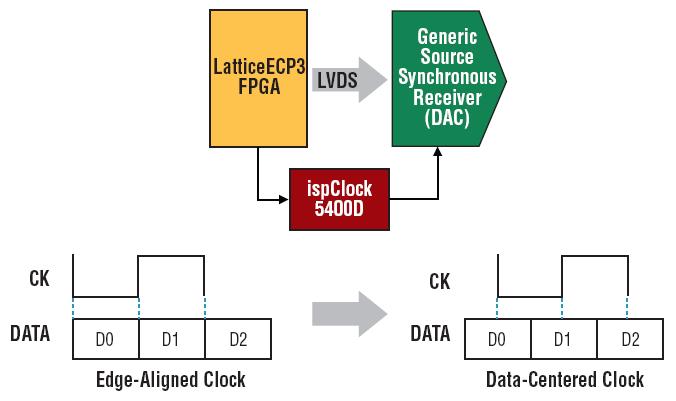

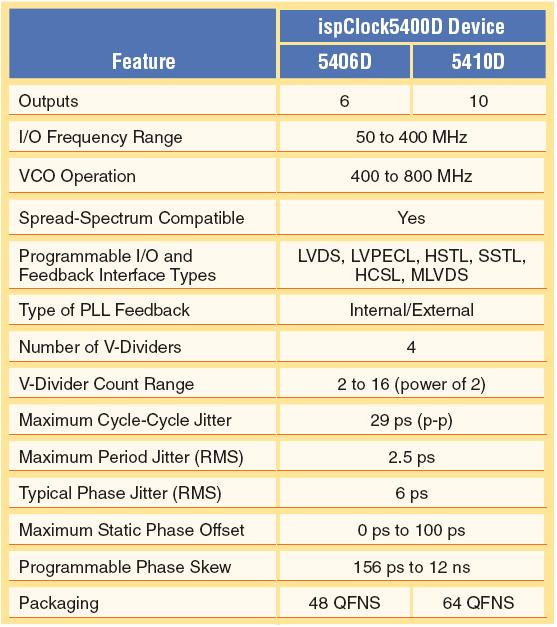

Rodina ispClock5400D In-System Programmable, Ultra-Low Jitter Zero Delay and Fan-Out Buffer, Differential, zastoupená dvěma členy ispClock5406D a ispClock5410D, tvoří integrované nástroje pro výrobu a precizní distribuci rozdílového hodinového signálu v obvodech vyžadujících nulové zpoždění hodinových bufferů (zero delay), v případě rychlých hradlových polí s bloky SERDES nebo u zařízení podporujících ATCA, MicroTCA, AMC, PCI Express apod.

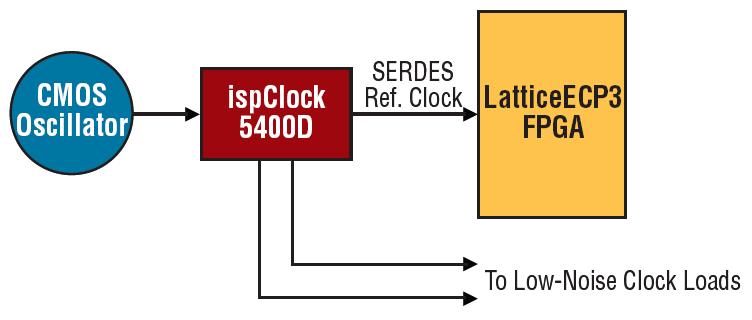

Referenční hodiny pro SERDES

IspClock5400D zahrnuje in – system programování, ultra nízký fázový šum (CleanClockTM) a třetí generaci PLL. Výstupní obvody označené jako FlexiClockTM podporují rozmanité logické standardy, přičemž zajišťují dvojnásobnou, časovou i fázovou kontrolu nad nesymetrií. Konfigurace každého čipu se odehrává ve vestavěné non – volatilní paměti, kterou lze reprogramovat prostřednictvím rozhraní JTAG, přičemž některé záležitosti lze ovlivnit i „za letu“ pomocí I2C.

Příklad hodinového managementu pro vysokorychlostní aplikace

Základní vlastnosti:

- Ultra nízký jitter

- Třetí generace PLL

- Vstupy pro externí zpětnou vazbu

- FlexiClock I/O

- Až 10 programovatelných Fan – Out bufferů

- In – system programování (JTAG, I2C)

Software