Nejmenší mikrokontrolér pro zabezpečené aplikace

MAXQ1850

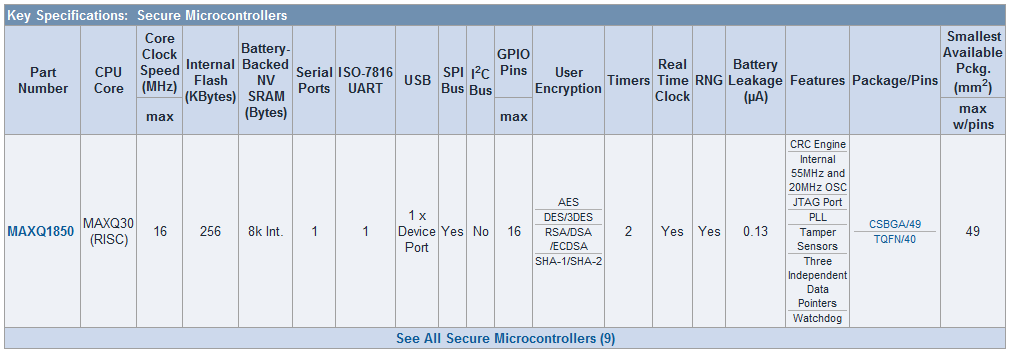

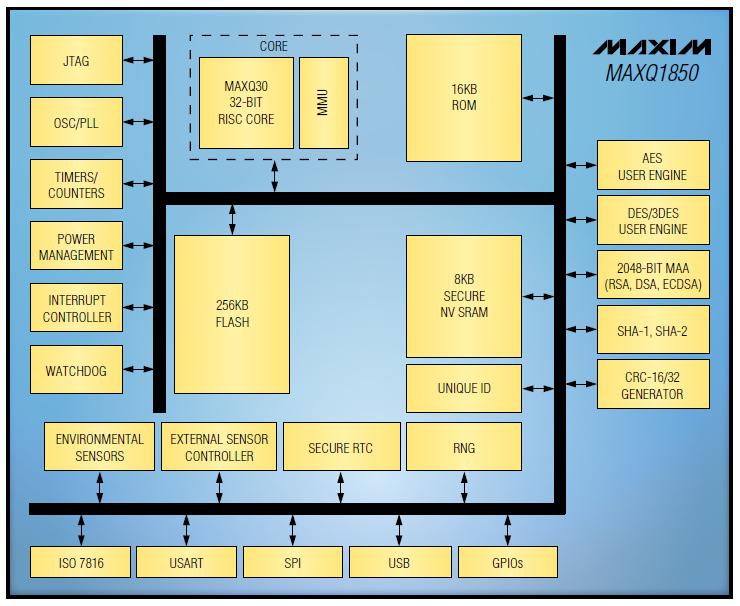

![]() Obvod MAXQ1850 patří ve své třídě k nejmenším mikrokontrolérům, vyvinutým s ohledem na vysokou míru zabezpečení koncové aplikace. Bezkonkurenční účinnosti při zpracování dat spolu s optimalizací C kódu bylo v případě tohoto 1cyklového procesoru s architekturou RISC dosaženo vykonáváním 16bitových instrukcí za přispění 32bitového toku dat. Díky hardwarovému urychlení symetrických i nesymetrických kódovacích postupů může v závislosti na požadavcích dané, zabezpečené aplikace nabídnout potřebnou flexibilitu, vyžadovanou pro nezávislé kontroléry či koprocesory. Rovněž musíme zmínit integrované snímače pro vyhodnocení případné sabotáže (Tamper). V reakci senzorů na detekovaný útok pak dochází k vymazání vestavěné, zajištěné, bateriově podepřené, non – volatilní paměti typu SRAM o velikosti 8 KB. Během zálohování zajištěné SRAM a provozu snímačů pro tampery mikrokontrolérem protéká pouhých 130 nA.

Obvod MAXQ1850 patří ve své třídě k nejmenším mikrokontrolérům, vyvinutým s ohledem na vysokou míru zabezpečení koncové aplikace. Bezkonkurenční účinnosti při zpracování dat spolu s optimalizací C kódu bylo v případě tohoto 1cyklového procesoru s architekturou RISC dosaženo vykonáváním 16bitových instrukcí za přispění 32bitového toku dat. Díky hardwarovému urychlení symetrických i nesymetrických kódovacích postupů může v závislosti na požadavcích dané, zabezpečené aplikace nabídnout potřebnou flexibilitu, vyžadovanou pro nezávislé kontroléry či koprocesory. Rovněž musíme zmínit integrované snímače pro vyhodnocení případné sabotáže (Tamper). V reakci senzorů na detekovaný útok pak dochází k vymazání vestavěné, zajištěné, bateriově podepřené, non – volatilní paměti typu SRAM o velikosti 8 KB. Během zálohování zajištěné SRAM a provozu snímačů pro tampery mikrokontrolérem protéká pouhých 130 nA.

Blokový diagram obvodu MAXQ1850

Základní vlastnosti a výhody obvodu MAXQ1850:

- Posílení bezpečnosti celého systému

- Kryptografické, hardwarové akcelerátory pro RSA, DSA, ECDSA, SHA-1, SHA-2, AES, DES a 3DES

- Bezpečnostní dohled (Tamper – detekce a reakce)

- Kryptografická jednotka, pracující na 65 MHz

- Minimální požadavky na velikost zastavěné plochy

- 6 mm x 6 mm, 40pinové pouzdro TQFN

- 7 mm x 7 mm, 49vývodové pouzdro CSBGA

Bezpečnostní správa systému, střežící kódovací klíče před narušiteli

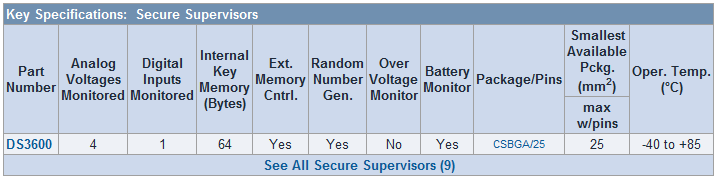

DS3600

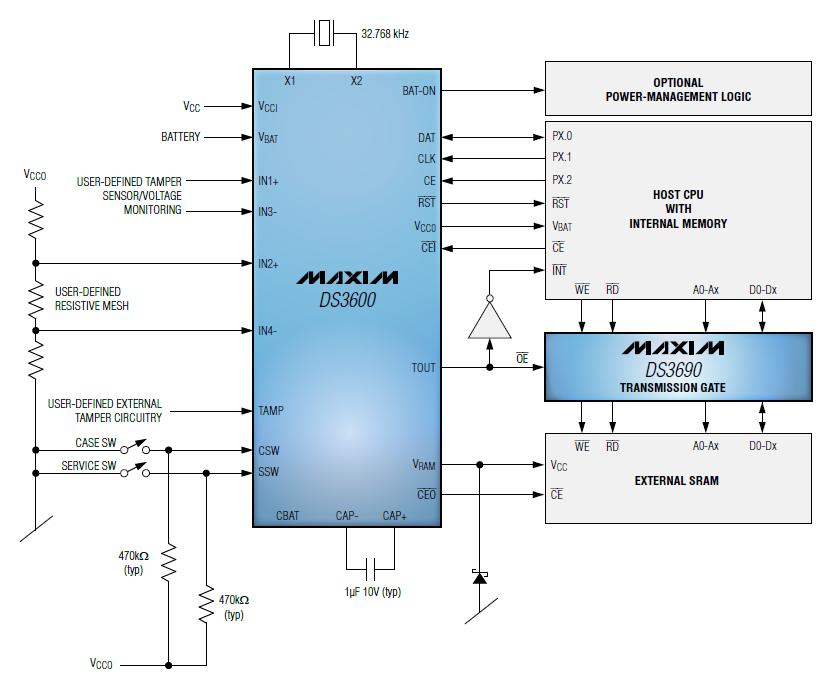

Bezpečnostní správa systému zajišťuje úplnou ochranu dat. Jednočipové řešení DS3600 nabídne bezpečnostní prvky, detekci sabotáže, uložení kódovacího klíče a také jeho zničení v případě potvrzené sabotáže. Pro zvýšenou úroveň zabezpečení bylo zvoleno pouzdro typu CSBGA.

Supervizor DS3600 v typické, bezpečnostní akci

Základní vlastnosti a výhody obvodu DS3600:

- Zvýšená míra zabezpečení

- Podpora nejvyšších požadavků v souvislosti se zajištěním (FIPS 140.2, Common Criteria, PCI PED a EMV 4.1)

- Víceúrovňová detekce sabotáže

- Klíče a / nebo další kritická data jsou v reakci na vzniklé narušení okamžitě a beze zbytku odstraněna

- Patentem chráněná, vestavěná a nezkopírovatelná paměť

1drátová ověřovací struktura, vycházející z SHA-1, bezpečně ochrání řídicí moduly před neoprávněným klonováním či změnou vlastností

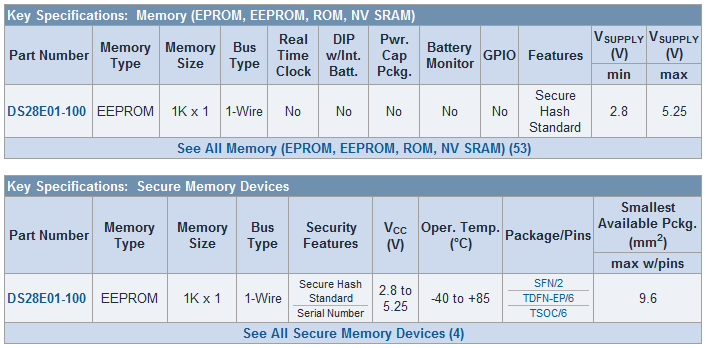

DS28E01-100, DS28E02, DS28E10

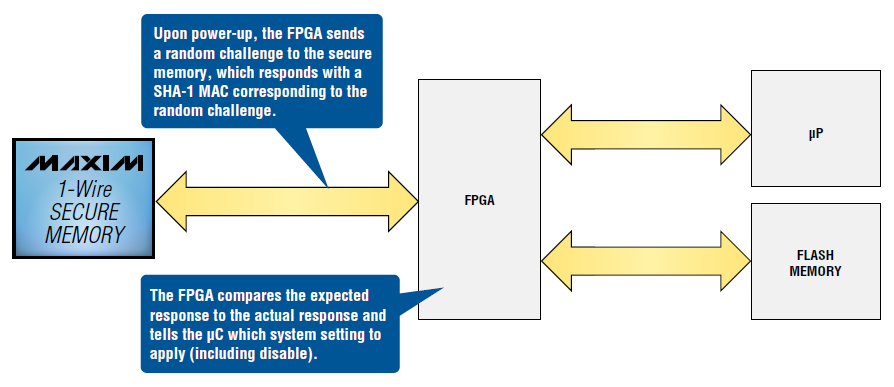

1drátové zabezpečené paměti využívají ověřovací posloupnost, založenou na dostatečně odolném vysílání požadavku, přijímání odezvy a samozřejmě také na algoritmu SHA-1. Díky takovému ověřování pravosti mohou FPGA či CPU rozlišovat mezi autorizovaným přístupem a klony. Konečné rozhodnutí pak buď umožní běžnou činnost systému nebo zakáže příslušný modul a zabrání případnému zneužití. Před neoprávněným pozměňováním lze navíc prostřednictvím algoritmu SHA-1 chránit i provozní nastavení modulu, uložená v paměti typu EPROM.

Blokový diagram systému FPGA, využívajícího ověřování s 1drátovým přístupem do chráněné paměti

Základní výhody daného řešení:

- Podpora zabezpečení celého systému

- Ověřování, založené na SHA-1 (FIPS 180-3)

- Propracované fyzické zabezpečení chrání před útoky na čipové úrovni

- Chráněná NV EPROM nebo OTP (One-Time Programmable) paměť pro ukládání citlivých dat

- Volitelné, spolehlivé před – programování zákazníkem definovaných dat

- Více informací získáte prostřednictvím těchto odkazů:

- Zanedbatelný vliv na vyhrazené I/O piny a související prostředky FPGA nebo CPU

- Vyžaduje pouze jediný I/O pin

- Jedno vyhrazené místo pro komunikaci a napájení

- Malé nároky na velikost kódu a využívanou paměť

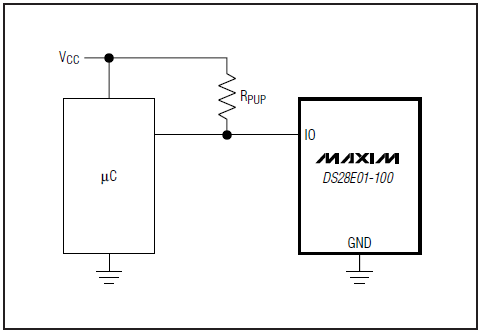

Typické zapojení obvodu DS28E01-100

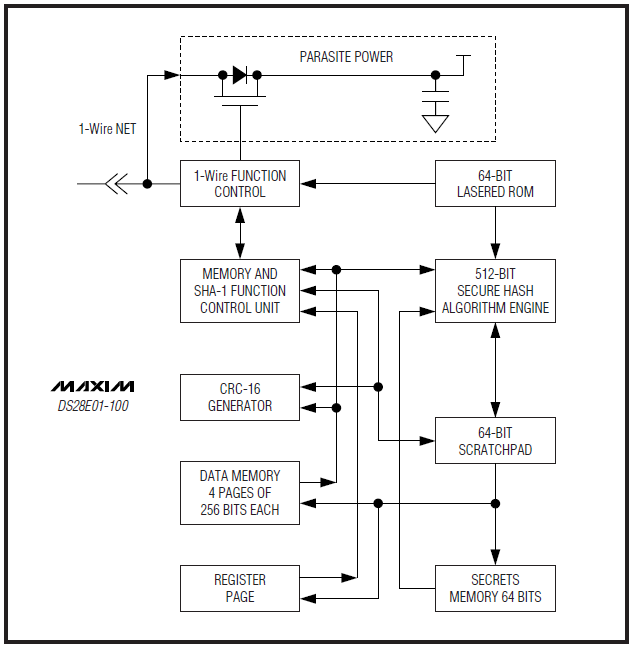

Vnitřní struktura obvodu DS28E01-100

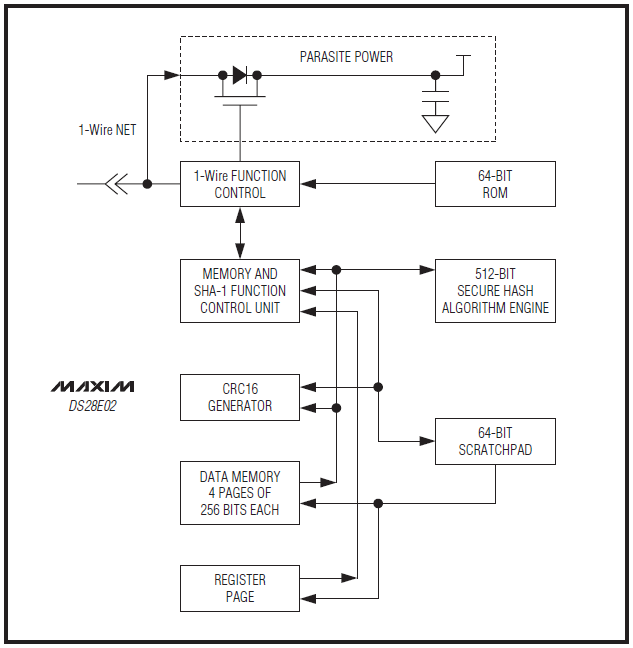

Vnitřní struktura obvodu DS28E02

Popis integrovaného obvodu DS28E02 na stránkách výrobce

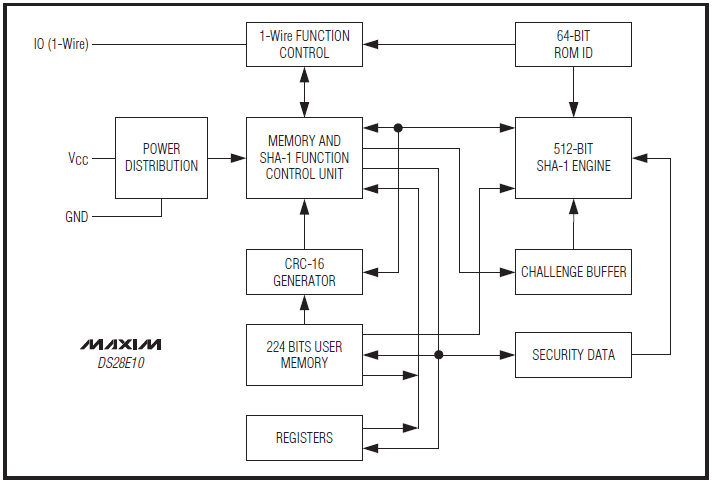

Vnitřní struktura obvodu DS28E10

Příště se budeme věnovat napájecím zdrojům.

Použitá literatura:

Download a odkazy:

Download a odkazy:

- Návrh PLC očima vývojáře – 1. část

- Návrh PLC očima vývojáře – 2. část (Analogové vstupy)

- Návrh PLC očima vývojáře – 3. část (Analogové vstupy – příklady)

- Návrh PLC očima vývojáře – 4. část (Analogové výstupy)

- Návrh PLC očima vývojáře – 5. část (Analogové výstupy – příklady)

- Návrh PLC očima vývojáře – 6. část (Průmyslová sběrnice)

- Návrh PLC očima vývojáře – 7. část (Průmyslová sběrnice – příklady)

- Návrh PLC očima vývojáře – 8. část (Digitální vstupy / výstupy)

- Návrh PLC očima vývojáře – 9. část (Digitální vstupy / výstupy – příklady)

- Návrh PLC očima vývojáře – 10. část (CPU)

- Domovská stránka Maxim: http://www.maxim-ic.com/

- Distributor pro ČR: http://www.mespraha.cz/