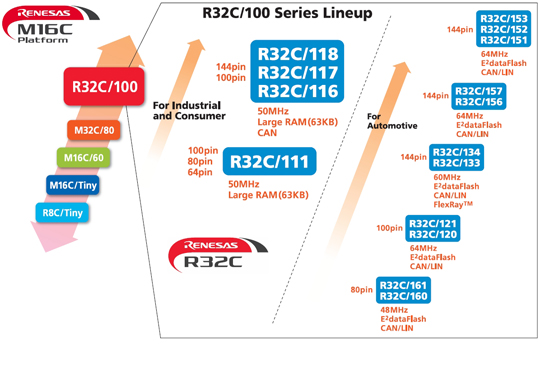

Ve všech těchto oblastech lidské činnosti se úspěšně prosadily 16bitové mikrořadiče. Náš podnik nyní přichází s novou řadou mikrořadičů R32C, kterou zahajuje proces dalšího zlepšování výkonnostní charakteristiky platformy MCU prostřednictvím stoprocentního 32bitového jádra.

Ve všech těchto oblastech lidské činnosti se úspěšně prosadily 16bitové mikrořadiče. Náš podnik nyní přichází s novou řadou mikrořadičů R32C, kterou zahajuje proces dalšího zlepšování výkonnostní charakteristiky platformy MCU prostřednictvím stoprocentního 32bitového jádra.

Výrobci průmyslových a spotřebních aplikací jsou v současné době pod velkým cenovým tlakem, což je motivuje k intenzivnějšímu využívání koncepcí založených na připravených platformách. Již nyní se množí aplikace postavené na rozvoji a rozšiřování platforem, přičemž prioritou je zatím v prvé řadě snižování nákladů opakovaným použitím již vyvinutých prvků.

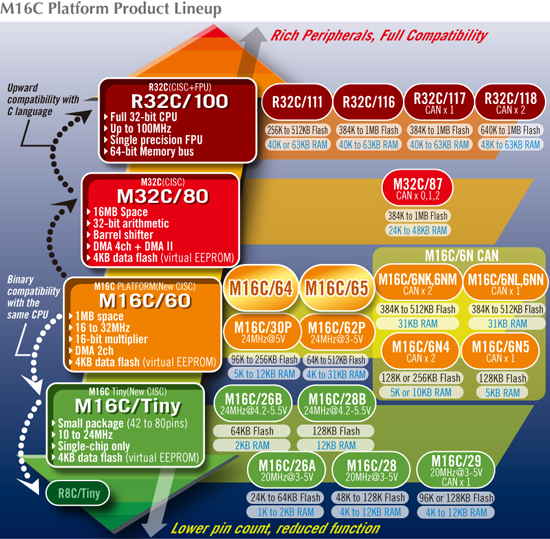

Společnost Renesas vychází svým produktovým spektrem tomuto trendu maximálně vstříc. Zmiňovaná platforma M16C v něm zaujímá výjimečné postavení, neboť je kompatibilní nejen s jádry a kódy MCU, nýbrž i s perifériemi a vývojovými prostředími. Kompatibilita je zajištěna dokonce i na úrovni kolíkových vývodů (pinů), což usnadňuje výběr součástek stejného formátu.

Společnost Renesas vychází svým produktovým spektrem tomuto trendu maximálně vstříc. Zmiňovaná platforma M16C v něm zaujímá výjimečné postavení, neboť je kompatibilní nejen s jádry a kódy MCU, nýbrž i s perifériemi a vývojovými prostředími. Kompatibilita je zajištěna dokonce i na úrovni kolíkových vývodů (pinů), což usnadňuje výběr součástek stejného formátu.

Trh však netíhne jen ke koncepcím flexibilních platforem umožňujícím opakované využití existujících kódů. Současně jsme také svědky příklonu ke stále výkonnějším modulům. V tomto duchu nabízí společnost Renesas svým zákazníků řešení spočívající v kombinaci nového, výkonnějšího modulu a stávající platformy v nezměněné podobě, které nemá žádný negativní dopad na technická a nákupní oddělení odběratelských firem.

Klíčem k úspěchu každé platformy je míra přizpůsobení potřebám finální aplikace. Tedy vhodně zvolené jádro s dostatečnou kapacitou paměti a vhodně vybavenou periférií. To vše samozřejmě za přijatelnou cenu v mezích uvažovaného rozpočtu. Všechny tyto požadavky splňuje nová řada R32C na bázi nového 32bitového jádra CISC.

R32C – výkonnější doplněk palety platforem M16C

Mikrořadiče nové řady R32C z produkce společnosti Renesas představují obohacení existující platformy M16C o výkonnější moduly s větší kapacitou pamětí FLASH a RAM. Po rostoucí kapacitě RAM je velká poptávka, a to proto, že zásobníky, které jsou v rámci implementace komunikačních protokolů potřeba, se v praxi běžně ukládají do interní paměti RAM.

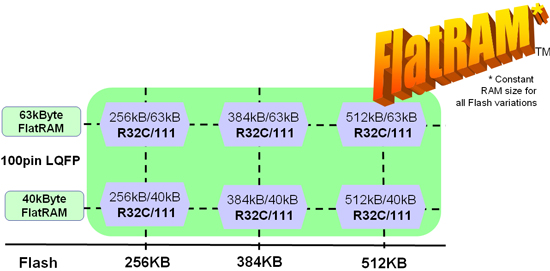

Všechny tyto vpravdě různorodé požadavky splňuje mikrořadič R32C/111 postavený na koncepci FlatRAM™. Základem filosofie FlatRAM je jednotná velikost paměťové oblasti RAM bez ohledu na kapacitu flashové paměti. Tato myšlenka vychází z úvahy, že menší nároky na kapacitu paměti FLASH nevedou automaticky ke zmenšení komunikačních zásobníků využívajících interní paměť RAM. Výhoda koncepce FlatRAM spočívá v tom, že ve fázi vývoje mohou inženýři pracovat s modulem o největší kapacitě paměti FLASH a pro účely sériové výroby přejít na variantu s FLASHEM přesné a vhodné velikosti, aniž by se měnila kapacita RAM. V nabídce společnosti Renesas jsou mikrořadiče R32C/111 s FlatRAM ve 40kB a 63kB verzi a interní pamětí FLASH o kapacitě 256 kB, 384 kB a 512 kB. Na trhu se tak objevují dosud poměrně neobvyklé kombinace paměťových jednotek – například 256kB FLASH spolu s 63kB interní RAM.

Koncepce FlatRAM mikrořadiče R32C/111

Moduly s větší kapacitou pamětí typu FLASH a RAM musí zvládat analogicky také větší množství výpočetních operací, než běžný 16bitový mikrořadič, a proto jsou vybaveny výkonným 32bitovým procesorovým jádrem typu R32C. Design tohoto jádra čerpá mimo jiné i z letitých zkušeností s velmi dobře známým jádrem M16C.

Jádro mikrořadiče R32C

R32C s 32bitovým jádrem CISC-MCU je založen na tzv. von Neumannově architektuře a obsahuje dva registrové bloky (banky) čítající celkem šestnáct 32bitových univerzálních/adresovacích registrů a čtyři 32bitové registry s ukazateli základu rámce či statického základu. Způsob využívání těchto datových registrů je možno pružně přizpůsobit individuálním požadavkům programového kódu.

R32C s 32bitovým jádrem CISC-MCU je založen na tzv. von Neumannově architektuře a obsahuje dva registrové bloky (banky) čítající celkem šestnáct 32bitových univerzálních/adresovacích registrů a čtyři 32bitové registry s ukazateli základu rámce či statického základu. Způsob využívání těchto datových registrů je možno pružně přizpůsobit individuálním požadavkům programového kódu.

CPU zahrnuje dále také celou řadu funkčních jednotek, které přispívají ke zvýšení všeobecné výkonnosti. Pro příklad jmenujme:

- hardwarovou násobičku: 32 bitů × 32 bitů = 64 bitů

- jednotku pro opakování instrukcí násobením a sčítáním (RMPA): 32 bitů × 32 bitů + 64 bitů = 64 bitů

- jednotku pro práci s pohyblivou řádovou čárkou FPU (s jednoduchou přesností) podle normy IEEE-754

- 32bitový posuvný registr

- 64bajtovou instrukční řadu

Skupina R32C/111 nyní dokáže vyvinout maximální taktovací frekvenci 50 MHz, z čehož plyne minimální doba trvání instrukčního cyklu 20 ns. S koncepcí R32C lze při zpracovávání kódů z integrované flashové paměti dosáhnout finálního výkonu 42 Dhrystone MIPS, a to bez vsunutých čekacích stavů – což je pro jednotku CPU typu CISC vynikající výsledek, který jsou jiná jádra CISC schopna překonat jen teoreticky.

Do CPU je kromě toho integrována také jednotka umožňující práci s čísly s pohyblivou řádovou čárkou (floating point unit; FPU) splňující požadavky normy IEEE-754. Které funkce FPU budou ke kompilaci kódu použity, lze zvolit ve vývojovém prostředí. FPU je přitom možno využívat pro logické instrukce různých typů, jako například sčítání, násobení, dělení, odčítání, převádění, porovnávání a zaokrouhlování proměnných s pohyblivou čárkou. S aktivní variantou podpory funkcionality FPU je kompilátor schopen generovat programy 50krát rychlejší, než je programový kód opírající se o volitelnou softwarovou knihovnu jednotky pro operace s pohyblivou řádovou čárkou.

Ke značnému zvýšení operačního výkonu přispívají svými aritmetickými funkcemi také integrovaný 32bitový multiplikátor spolu s rovněž vestavěným 32bitovým posuvným registrem.

Již tak vysokou výkonnostní hladinu zvedají ještě také další prvky a funkce jako 32bitová hardwarová násobička. R32C podporuje kromě toho i elementární funkce DSP jako například realizaci instrukcí typu RMAC (opakování násobením/sčítáním) vyskytujících se obvykle ve výpočtech s filtrem.

V zájmu dosažení maximální výkonnosti je popisované 32bitové jádro napojeno na interní paměťovou sběrnici o šířce 64 bitů. Struktura této interní sběrnice je rozčleněna na dva úseky, na rychlou sběrnici, jež je vyhrazena pro CPU a pro přístupy do paměti, a na pomalejší sběrnici, která slouží jako rozhraní k periferním funkcím. Vedle zmíněné interní sběrnice a periferní sběrnice nabízí R32C také externí sběrnici o šířce 8 bitů nebo 16 bitů a taktovací frekvenci až 32 MHz. Adresovací oblast o velikosti 64 MB je možno rozdělit až na čtyři části se vstupy v podobě „výběru čipu“ individuálně volitelné šířky datového pásma a vsuvek čekacích stavů. Při realizaci individuálních systémových koncepcí je takto zajištěna maximální možná flexibilita.

Odkazy

Odkazy

- Autor: Bernd Westhoff Renesas; Marc-Oliver Reinschmidt, GLYN Germany

- Domovská stránka GLYN - http://www.glyn.cz

- Hlavní stránka společnosti Renesas Technology Europe - http://eu.renesas.com/