Beze změny zůstává vlastnost ?instant-on?, tedy funkčnost ihned po zapnutí napájení, a přidává se navíc zabezpečený bitstream, zálohování EBR do flash a možnost přeprogramování pole za běhu. Čipy se vyrábějí v ?křemíkové slévárně? firmy Fujitsu nejnovější technologií, která dovoluje vytvořit flash paměť a logiku na jednom čipu při 90nm výrobním procesu.

Hradlová pole LatticeXP2 se budou vyrábět v pěti velikostech od 5k do 40k čtyřvstupových LUT. Paměť EBR, tvořená dvouportovými bloky po 18 kilobitech, dosahuje velikosti 162 kbit u nejmenšího a 864 kbit u největšího provedení. Pro menší buffery nebo FIFO lze také vytvořit paměť RAM z logických elementů (distribuovaná paměť RAM) až do velikosti 83 kbit. Pro podporu návrhů, stále častěji vyžadujících složité matematické operace, je k dispozici až 8 sysDSP bloků, které postupně (pipeline) dělají násobení a součet 36x36 bitů při taktu až 365 MHz. Jeden sysDSP blok lze nakonfigurovat pro jako jednu 36x36, čtyři 18x18, nebo osm 9x9 násobiček. O generování a zarovnávání hodin se starají 2 nebo 4 fázové závěsy (PLL) se vstupní frekvencí 10 až 420 MHz.

Počet I/O pinů se pohybuje od 86 do 540 v závislosti na pouzdru a velikosti pole. I/O buffery podporují nejpopulárnější standardy, jako PCI, LVTTL, LVCMOS, SSTL, HSTL a LVDS včetně hardwarových bloků pro jednoduché připojení DDR pamětí, které umožňují připojit DDR či DDR2 paměti až do rychlosti 400 Mbit/s na pin, rychlé AD nebo DA převodníky až do 750Mbit/s nebo 7:1 LVDS display interface při více jak 600 Mbit/s. LatticeXP2 budou dostupné jednak v klasických vývodových pouzdrech TQFP a PQFP, tak v rozměrově úsporných BGA.

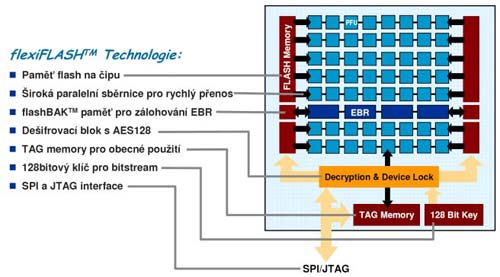

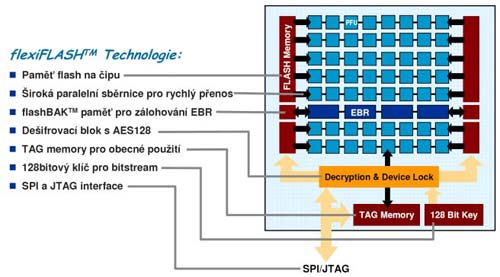

Architektura ?flexiFLASH?

Flash paměť, která u LatticeXP2 drží konfigurační bitstream, se nachází přímo na čipu. Jedná se tedy skutečné o jednočipové řešení, kterému Lattice říká flexiFlash. Po zapnutí napájení, nebo na uživatelský povel, se přenese celý obsah paměti flash do SRAM, která řídí vlastní propojení FPGA. Přenos probíhá vysokou rychlostí po masivní paralelní sběrnici, takže je celé pole připraveno přibližně do 2 ms, což je výrazně kratší doba, než za jakou je schopno naběhnout klasické FPGA, které potřebuje boot PROM, ať už externí, nebo zalitou v pouzdře spolu s FPGA. Za takto krátkou dobu dokonce nestačí naběhnout ani krystalový oscilátor, nebo napájecí zdroj. Takže ve chvíli, kdy je k dispozici stabilní napájecí napětí a hodinový signál z oscilátoru, je již FPGA dlouhou dobu nakonfigurované a funkční. Toto je nezbytná vlastnost pro realizaci systémových funkcí, jako je správa napájení, dekódování adres na sběrnici, nebo resetovací logika.

Umístěním paměti s konfigurací přímo na čip FPGA je také zaručena podstatně lepší ochrana dat, která je navíc posílena možností zakázat zpětné vyčtení. Do FPGA lze také volitelně uložit 128bitový AES klíč, který poté slouží k dešifrování (zašifrovaných) konfiguračních dat během programování obvodu. Proti neoprávněnému nebo nechtěnému smazání či přeprogramování chrání obvod další 64bitový klíč. Během programování je také možno zvolit tzv. OTP mód, který zakáže jakékoli další smazání nebo přeprogramování.

Součástí flash na čipu je také paměť ?FlashBAK?, která zrcadlí všechny bloky EBR a po zapnutí napájení tyto bloky inicializuje na definovaný obsah. Kromě toho je navíc u LatticeXP2 možnost kdykoli během provozu zapsat zpět data z EBR do flash. Lze toho využít např. pro ukládání kalibračních konstant, či zálohování stavových proměnných, nebo jiných důležitých dat, která se nesmí ztratit po vypnutí napájecího napětí. Celý přepis včetně smazání trvá asi jednu sekundu, takže je potřeba počítat s tímto časem při návrhu napájecího zdroje. Navíc je k dispozici 0,6 až 3,4 kbitů sériové TAG flash paměti pro obecné použití. Tato paměť je přístupná z logiky v FPGA i z programovacího rozhraní, i když je obvod uzamčený. Lze sem např. uložit sériové číslo, uživatelská nastavení, atd.

Možnosti přeprogramování ?za běhu?

V podstatě každý výrobce složitějších systémů dnes nabízí možnost aktualizace firmware. Aktualizace přitom musí být spolehlivá, bezpečná a ve spoustě případů nesmí dojít k výpadku funkce přístroje. Nyní si povíme, co všechno musí, nebo spíše nemusí vývojář řešit, pokud se rozhodne pro použití LatticeXP2.

Spolehlivost přeprogramování je zajištěna funkcí dual-boot. K obvodu lze totiž připojit externí SPI flash paměť podobně, jako ke klasickému SRAM FPGA. Pokud dojde k selhání během přepisu vnitřní flash paměti, ať už kvůli chybě v datech, nebo výpadku napájení, a hradlovému poli se tedy po resetu nepodaří načíst konfiguraci z vnitřní paměti, pokusí se automaticky načíst ?záložní? konfiguraci z externí paměti. Není proto třeba používat záložní bateriový zdroj, nebo navrhovat speciální dohlížecí obvod.

Výrobce zařízení může také s klidným svědomím umístit aktualizovaný zašifrovaný firmware na Internet, aniž by musel mít strach, že mu někdo design ukradne. O zabezpečení se totiž stará již zmíněné AES128 dešifrovací jádro. Není tedy nutné používat přídavný komunikační procesor, který by data dekódoval nebo vymýšlet vlastní šifrovací algoritmus.

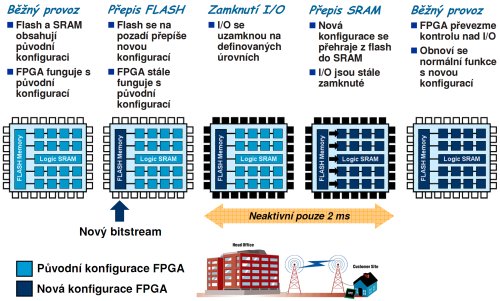

LatticeXP2 také podporují tzv. ?Transparent Field Reconfiguration? neboli TransFR. V podstatě jde o techniku, jak přepsat konfiguraci uvnitř FPGA ?na pozadí?, přičemž FPGA se stane neaktivní pouze na 2 ms. Nejlépe to vystihuje následující obrázek, kde je naznačen průběh přeprogramování konfigurace.

Dostupnost a ceny

Vzorky prvního dostupného typu LFXP2-17 se 17k LUT v pouzdru 208PQFP, 256ftBGA a 484fpBGA jsou již k dispozici. Lattice plánuje uvést celou rodinu XP2 na trh do konce roku 2007. Orientační cena LFXP2-17 by měla být kolem 12 USD na 100 000 kusů. Máte-li zájem o vzorky, nebo vývojový kit, napište si o ně firmě MSC-Vertriebs-CZ na praha@ msc-ge.com, autorizovanému distributorovi Lattice Semiconductor Corporation.

Download & Odkazy

Download & Odkazy

- Domovská stránka Lattice Semiconductor - http://www.latticesemi.com/

- Domovská stránka distributora - http://www.msc-ge.com/

- Online pozvánka na seminář

- Online registrace na seminář