Úvod:

Série těchto obvodů Atmel označuje AT94K a AT94S (S značí Secure, neboli zabezpečený). Tyto součástky kombinují všechny základní stavební bloky (logiku, paměť a systém) v monolitickém programovatelném obvodu založeném na technologii SRAM.

Série těchto obvodů Atmel označuje AT94K a AT94S (S značí Secure, neboli zabezpečený). Tyto součástky kombinují všechny základní stavební bloky (logiku, paměť a systém) v monolitickém programovatelném obvodu založeném na technologii SRAM.

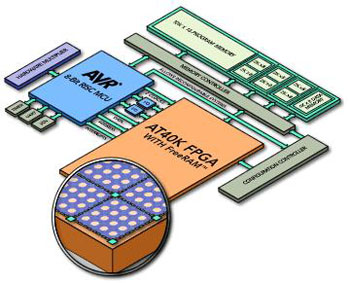

V zásadě se jedná o 8bitové MCU řady AVR doplněné o hradlové pole FPGA. Obvody FPSLIC kombinují 5 až 40 tisíc hradel Atmelem patentované FPGA architektury (AT40K), 8bitové jádro AVR (20 - 30 MIPS, RISC), velký počet periférií a až 36KB paměti programu a dat typu SRAM.

Co se týče sériových konfiguračních pamětí pro FPGA část obvodů, jsou zde dostupná dvě řešení, buď použití externích pamětí ATFSxx nebo obvodové řady Secure AT94S. Ta nabízí mnohem větší bezpečnost, větší stupeň integrace a právě již zmíněnou konfigurační paměť ve společném pouzdře, to umožňuje programování přímo v aplikaci (ISP) a vzdálené updaty. Zvýšená bezpečnost se týká zejména ochraně proti vyčtení programového kódu z FPGA a AVR.

Obvody ATFS05, ATFS10 a ATFS40 jsou paměti typu EEPROM které poskytují jednoduchost a cenovou výhodnost pro konfiguraci bloku FPGA obvodů FPSLIC. Použitý jednoduchý sériový protokol umožňuje konfigurovat jeden či více obvodů na jednou a jejich malá velikost šetří místem na desce plošných spojů.

Vlastnosti:

Monolithic Field Programmable System Level Integrated Circuit (FPSLIC?)

Monolithic Field Programmable System Level Integrated Circuit (FPSLIC?)

FPGA architektura AT40K (založena na technologii SRAM) s integrovaným RISC AVR? jádrem- 5,000 až 40,000 Hradel patentováné SRAM AT40K FPGA a FreeRAM? dostupnou uživateli

? 2 - 18.4 Kbits Single/Dual Port FPGA User SRAM

? Vysoce výkonné optimalizové FPGA Core Cell

? Možnost dynamického rekonfigurování FPGA - Velmi nízká statická a dynamická spotřeba proudu ? vhodné pro přenosná zařízení napájená z baterií

- Patentovaná vylepšená AVR architektura RISC

? více jak 120 výkonných instrukcí, přičemž většina je provedena v jednom hodinovém cyklu

? Vysoce výkonná hardwarová násobička pro systémy založené na DSP

? Výkon přibližující se k 1 MIPS při 1 MHz

? Architektura je optimalizována pro C kód s 32 x 8 interními registry pro všeobecné použití

? Low-power Idle, Power-save a Power-down módy

? 100 ?A Standby a typicky 2-3 mA na 1 MHz v aktivním módu - Až 36 KB Dynamicky alokované paměti SRAM pro program a data

- Až 16 KB x 16 vnitřní 15 ns paměti SRAM pro instrukce

- Až 16 KB x 8 Internal 15 ns paměti SRAM pro data

- JTAG (IEEE std. 1149.1 kompatibilní) Interface

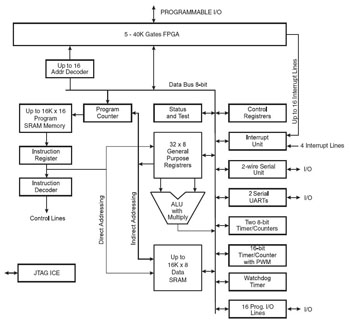

- Periférie jádra AVR

? 2-wire Serial Interface (vyhovující průmyslovému standardu)

? Dvě programovatelné sériové linky UART

? Dva 8bitové Čítače/Časovače každý se svojí předděličkou a jednotkou PWM

? Jeden 16bitový Čítač/Časovač s předděličkou, Compare/Capture módem a dvojitým 8, 9 nebo 10bitovým PWM - Podpora pro zákaznické FPGA periférie

? FPGA Macro knihovna zákaznických periférií - 16 FPGA interních přerušení do jádra AVR

- Až čtyři zdroje externího přerušení pro AVR

- 8 různých zdrojů hodin pro FPGA

? Dva zdroje hodin jsou odvozeny z vnitřní logiky jádra AVR - Programovatelný Watchdog Timer s interním oscilátorem

- Softwarově nastavitelný takt hodin

- Samostatný oscilátor pro Čítač/Časovač a pro obvod reálného času

- Napájecí napětí: 3,0V - 3,6V

- 3.3V 33 MHz PCI-kompatibilní FPGA I/O

? 20 mA Sink/Source High-performance I/O Structures - Všechny I/O FPGA idividuálně programovatelné

- Vstupy tolerují úrovně TTL 5V

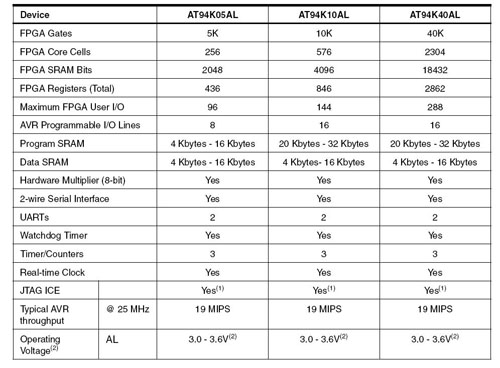

V následující tabulce jsou patrné parametry série AT94K obvodů FPSLIC, které jsou kombinací populárního FPGA AT40K a výkonného 8bitového MCU řady AVR se standardními perifériemi. Tyto obvody jsou vyráběny 0.35?m 5vrstvou CMOS technologií.

Software:

Software:

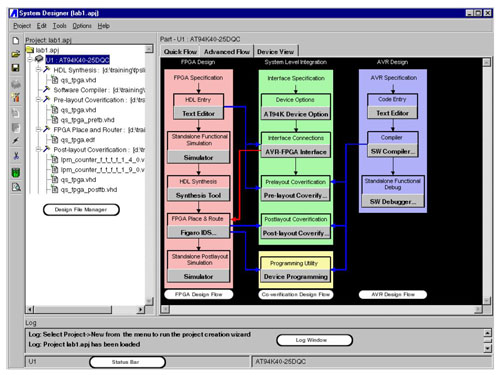

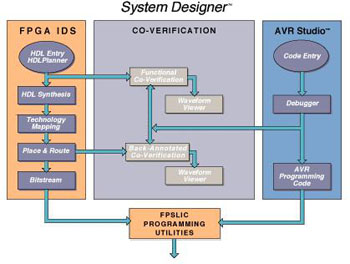

K návrhu elektronických systémů s platformou SLI (s obvody FPSLIC) se používá jednotné IDE, tzv. System Designer. Což je vlastně kompletní balíček softwaru pro zadání návrhu, návrh, syntézu, simulaci až po konečné ladění a programování. Balíček obsahuje následující software:

- Atmel AVR Studio?

- Atmel Configurator Programming System (CPS)

- Co-verification, Powered by Mentor Graphics

- LeonardoSpectrum?

- ModelSim? od fy. Model Technology? (simulátor)

- Několik C kompilerů (vývojové verze)

- Atmel Integrated Development System (IDS) ? FPGA Place & Route Tool (návrh FPGA)

- Security Dongle (bezpečnostní klíčenka, pouze při nákupu ATDH94DNG)

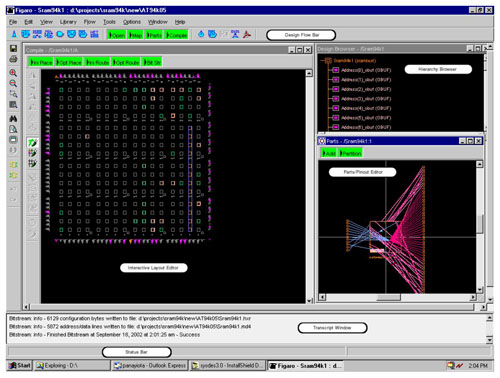

Jenom popis tohoto navrhového systému by vydal na samostatný článek (či spíše sérii článků), proto přidávám na ukázku pouze pár screenshotů.

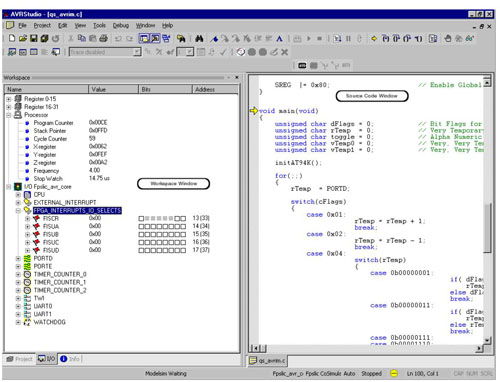

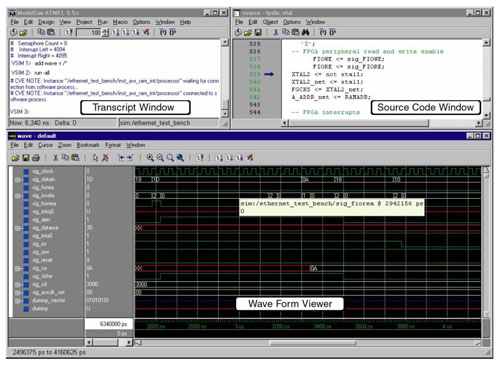

Na obrázku 1 je znázorněn System Designer desktop. Flow-chart diagram patrný na jeho pravé straně poskytuje "push-button" přístup (tlačítka) ke všem stupňům návrhu. Toto zahrnuje vložení kódů, software debugging (obr. 2), simulaci (obr. 3) včetně časových závislostí mezi FPGA a AVR jádrem, syntézu a automatické generování souborů potřebných k simulaci. Rozmístění bloků a vývodů hradlového pole FPGA je vidět na obr. 4. Šipky mezi jednotlivými diagramy určují závislosti mezi jednotlivými kroky.

Závěr:

Obvody FPSLIC se již velmi přibližují sofistikovaným jednočipovým řešením. Spojením výkonného, velmi oblíbeného jádra AVR a programovatelného hradlového pole se nám do rukou dostává obvod, pro který se možnosti použití přímo nabízí. Dle slov výrobce je hradlové pole primárně určeno pro vysoce nestandardní uživatelsky definovaná rozhraním mezi jádrem AVR a systémem kde je obvod použit. Vzhledem k tomu, že I/O FPGA jsou kompatibilní se sběrnicí PCI, dává možnost využít tohoto stále populárního rozhraní i pro amatérské účely. 40 tisíc hradel by mohlo postačit i pro takové věci jako jsou řadičě displejů (alfanumerických i TFT), pro časově náročné operace, různé matematické transformace (např. pro analýzu signálů) atd. I fakt, že obvod má celkově nízkou spotřebu proudu, ho předurčuje pro přenosné aplikace a systémy napájené z baterií. Díky rozhraní JTAG lze celý obvod programovat a konfigurovat z jakéhokoliv programátoru JTAG, který pracuje spolu s AVRStudiem.

Odkazy & Download :

- Oficiální stránka výrobce: http://www.atmel.com

- Datasheet k sérii obvodů AT94K

- Datasheet k System Designeru