Využíváme – li v našich aplikacích vysokorychlostní A/D nebo D/A převodníky, pravděpodobně se neobejdeme bez precizních zdrojů taktovacího kmitočtu či nejrůznějších bufferů, zajišťujících jeho další větvení (viz např. článek Hodinový oscilátor s duálním výstupem a nízkým jitterem od Maximu). Jak nás již ostatně proškolila samotná praxe, budeme při těchto aktivitách muset počítat se dvěma hlavními příčinami degradace hodinového signálu:

- Samotná deska plošného spoje a způsob, jakým vedeme hodinové signály

- Výstupní zakončení zdroje hodinového signálu

Trasa hodinového signálu a jeho rozkmit

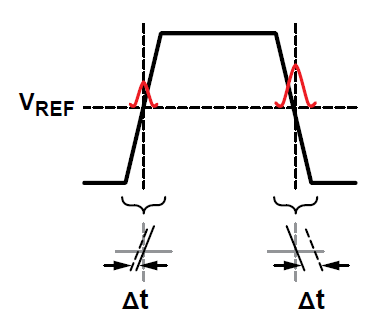

Samotná trasa taktovacího kmitočtu napříč deskou plošného spoje vykazuje chování, typické pro dolnopropustný filtr, čímž dochází k postupnému tlumení užitečného signálu. S rostoucí délkou příslušného vedení rovněž zaznamenáváme zvýšené zkreslení generovaných pulsů i jejich hran. Útlum, zkreslení i šum budou v případě vyšších kmitočtů nabývat na svém významu, což ovšem neplatí pro jitter (časová nejistota, neklid; původní výraz v sobě rovněž nese myšlenku nervozity či paniky), který bude nejhorší právě u malých rychlostí přeběhu (viz obrázek). V typických aplikacích přitom využíváme signály, jejichž hrany vykazují vysokou rychlost změn. Abychom se tedy co nejvíce přiblížili ideálnímu modelu taktování, musíme

Samotná trasa taktovacího kmitočtu napříč deskou plošného spoje vykazuje chování, typické pro dolnopropustný filtr, čímž dochází k postupnému tlumení užitečného signálu. S rostoucí délkou příslušného vedení rovněž zaznamenáváme zvýšené zkreslení generovaných pulsů i jejich hran. Útlum, zkreslení i šum budou v případě vyšších kmitočtů nabývat na svém významu, což ovšem neplatí pro jitter (časová nejistota, neklid; původní výraz v sobě rovněž nese myšlenku nervozity či paniky), který bude nejhorší právě u malých rychlostí přeběhu (viz obrázek). V typických aplikacích přitom využíváme signály, jejichž hrany vykazují vysokou rychlost změn. Abychom se tedy co nejvíce přiblížili ideálnímu modelu taktování, musíme

- použít hodinové signály s velkým rozkmitem a

- krátké cesty na desce plošného spoje, jinými slovy

- umístit taktovanou součástku co nejblíže svému zdroji hodinového kmitočtu.

RMS jitter obvodu ADCLK925 ve vztahu ke vstupní rychlosti přeběhu

Typickými zástupci obvodů pro distribuci hodinového signálu jsou např.

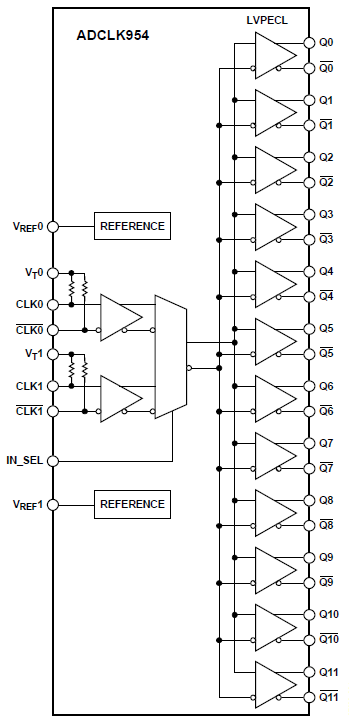

- ADCLK954 (Oddělovací stupeň s funkcí větvení hodinového kmitočtu – Clock Fanout Buffer)

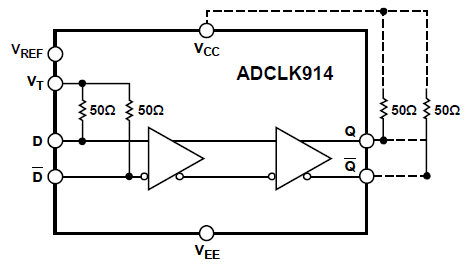

- ADCLK914 (Ultrafast Clock Buffer)

Integrovaný obvod ADCLK954 se skládá z 12 výstupních budičů, které zajistí plný, 800 mV rozkmit ECL (emitter-coupled logic) nebo LVPECL (low-voltage positive ECL) signálů do 50 Ω zátěží, tj. celkový rozkmit výstupního rozdílového signálu 1.6 V (viz obrázek níže). Pracovní kmitočet přitom může dosahovat až 4.8 GHz.

Struktura ADCLK914 zase pracuje s 1.9 V HVDS signály (high-voltage differential signal), dodávanými opět do 50 Ω zátěže s celkovým rozkmitem výstupního rozdílového signálu 3.8 V. ADCLK914 zvládá změny až do 7.5 GHz.

Budeme – li např. budit D/A převodník, měli bychom zajistit, že obvod pro distribuci hodinových signálů bude situován těsně (jak jen to půjde) vedle taktovacího vstupu převodníku. Zbavíme se tak mnoha problémů, při kterých vyžadovaná, vysoká rychlost přeběhu i velká amplituda hodinového signálu již nebudou působit těžkosti se směrováním spojů a výrobou mohutných interferencí (EMI). Také zbytečně nemusíme degradovat užitečné parametry z titulu dielektrických nebo celé řady dalších ztrát. Stojí za zmínku, že charakteristická impedance trasy (Zo) se ráda mění s jejími rozměry, tj. délkou, šířkou i tloušťkou. Výstupní impedanci budičů proto musíme této charakteristické impedanci přizpůsobit.

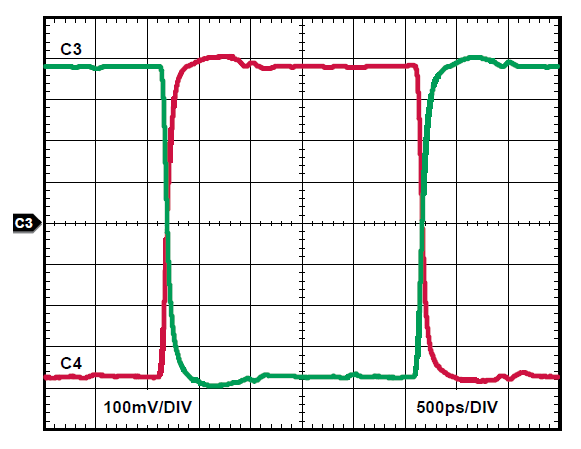

Časový průběh výstupního signálu hodinového bufferu ADCLK954 při napájení ze zdroje 3.3 V

Řádné zakončení výstupu

Protože tlumení hodinového signálu může způsobit zvětšení jitteru, bude nezbytné zakončit výstupy daného budiče tak abychom zabránili odrazům a maximální možnou měrou využili dostupné přenosové možnosti v relativně širokém kmitočtovém pásmu. Je to tak,

odrazy mohou způsobit nejrůznější podkmity či překmity a příšerně tak ublížit nejen samotnému signálu ale také celkovým parametrům. V horším případě tímto způsobem předčasně vypravíme přijímač i jeho budič rovnou do tranzistorového ráje (viz také křemíkové nebe).

Odrazy, způsobené impedančním nepřizpůsobením, pozorujeme tehdy, nemáme – li náležitě zakončeny signálové trasy. Celá situace se dále komplikuje v případě vysokorychlostních signálů s rychlými náběžnými a sestupnými hranami (dáno povahou odrazového koeficientu). Odražený puls se na hlavní hodinový signál nabalí (superponuje) a katastrofa je na světě. Nežádoucí vliv rovněž spatřujeme na hranách signálu, které vykáží nejistotu časového zpoždění jak při svém náběhu tak i během sestupu (viz obrázek).

Nepřizpůsobené zakončení vede v lepším případě jen k odrazům a hůře předvídatelnému časovému zpoždění hran

Amplituda odrazu, způsobeného nevhodným zakončením, se bude v čase měnit, takže ani Δt nebude stálé. Tvar i šířku odraženého pulsu navíc spoludefinuje příslušná časová konstanta. V této souvislosti proto ještě hovoříme o přídavných složkách (Gaussian), které se budou k výchozímu jitteru dále nabalovat. Abychom tedy zabránili zbytečnému znehodnocení signálu, budeme muset zajistit náležité zakončení celé signálové trasy, tak jak je to shrnuto níže.

Pozn.:

- Zo (viz přehled níže) reprezentuje impedanci vedení,

- Zout zahrnuje výstupní impedance budiče a

- Zin je vstupní impedancí přijímače.

Uvažovat přitom budeme jen struktury typu CMOS a PECL/LVPECL.

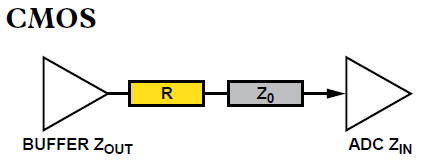

Metoda: Sériové zakončení

Popis:

Je-li díky dynamické frekvenční závislosti obtížné najít impedanční shodu, bývá v praxi odpor R na výstupu bufferu vynecháván.

Silné stránky:

- Nízkopříkonové řešení; do země neodtéká žádný proud.

- Jednoduchý výpočet odporu (Zo - Zout)

Nedostatky:

- Obvodové R a C ovlivňují náběžné / sestupné časy, roste jitter.

- Vhodné jen pro nízkofrekvenční signály.

Komentář:

- Budiče CMOS

- Není vhodné pro vysokofrekvenční taktování.

- Vyhovuje signálům s nízkými frekvencemi a velmi krátkými, přístupovými trasami.

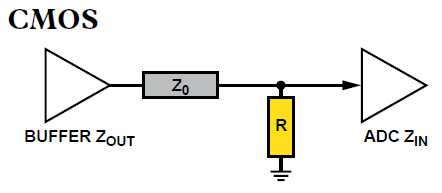

Metoda: Pull – Down rezistor

Popis:

Silné stránky:

- Velmi jednoduché (R = Zo)

Nedostatky:

- Vyšší výkonová spotřeba.

Komentář:

- Nedoporučuje se.

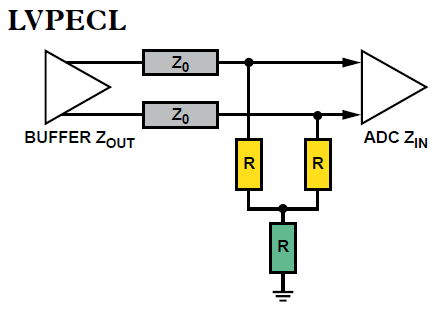

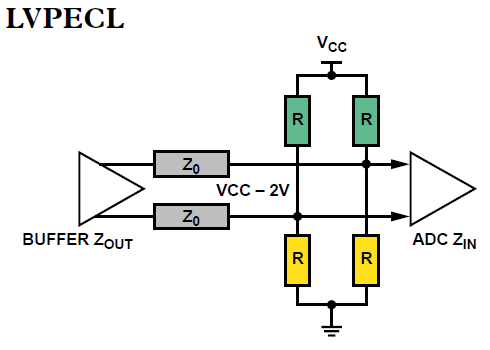

Metoda: Pull – Down rezistor

Popis:

Silné stránky:

- Jednoduché řešení se třemi rezistory.

- O něco málo lepší v otázce výkonové spotřeby; méně součástek ve srovnání se 4rezistorovým zakončením.

Nedostatky:

-

Komentář:

- Doporučeno.

- Zakončovací rezistory je potřeba umístit co nejblíže k PECL přijímači.

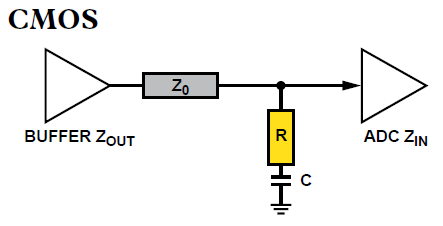

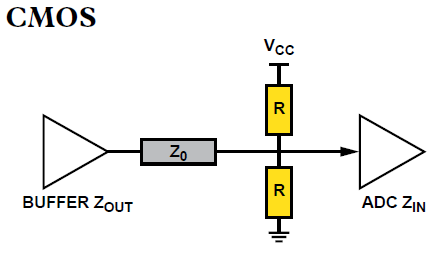

Metoda: Střídavé (AC) zakončení

Popis:

Silné stránky:

- Neprotéká žádný stejnosměrný proud.

Nedostatky:

-

Komentář:

- C volíme kompromisně s ohledem na energetické poměry a velikost odtékajícího proudu.

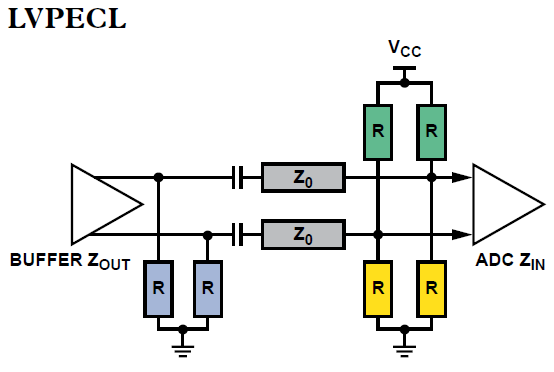

Metoda: Střídavé (AC) zakončení

Popis:

Silné stránky:

- Střídavá vazba umožňuje nastavit předpětí.

- Zároveň brání průtoku stejnosměrného proudu mezi oběma stranami obvodu.

Nedostatky:

- Střídavá vazba je doporučena jen pro symetrické hodinové signály s 50 % střídou.

Komentář:

- Vazební kapacity by měly mít malé ESR a malou kapacitanci.

Metoda: Rezistorový můstek

Popis:

Silné stránky:

- Rozumný výkonový kompromis

Nedostatky:

- Potřebuje dvě součástky pro single – ended hodiny.

Komentář:

-

Metoda: Rezistorový můstek

Popis:

Silné stránky:

-

Nedostatky:

- Výstupní rozdílová logika používá čtyři vnější součástky.

Komentář:

- Široce využívané zakončení pro 3.3 V budiče LVPECL.

Použitá literatura:

- [1] http://www.analog.com/library/analogDialogue/archives/44-01/clock_termination.pdf

- [2] http://www.analog.com/static/imported-files/data_sheets/ADCLK954.pdf

- [3] http://www.analog.com/static/imported-files/data_sheets/ADCLK914.pdf