Texas Instruments přichází s malou revolucí, díky nahrazení FLASH, SRAM a EEPROM v jednočipových procesorech jedinou pamětí FRAM. Sériové paměti EEPROM jsou ale na trhu nejméně od Millenia. Proč to trvalo „tak dlouho“?

Texas Instruments přichází s malou revolucí, díky nahrazení FLASH, SRAM a EEPROM v jednočipových procesorech jedinou pamětí FRAM. Sériové paměti EEPROM jsou ale na trhu nejméně od Millenia. Proč to trvalo „tak dlouho“?

- Pro spojení technologie FRAM s klasickými procesory bylo potřeba překonat řadu technologických problémů. Především vše usnadňuje technologie 130 nm, díky které je pro velikosti do 128 kB pro TI dnes levnější použít FRAM než FLASH.

Parametry FRAM jsou úctyhodné. Člověk se ale neubrání pocitu že „to musí mít nějaký háček“. Proč například FRAM potřebuje méně energie?

- Technologie FLASH potřebuje pro obsluhu zápisu napětí přes 10 V. To si žádá napěťový konvertor na čipu. Efektivita takového měniče pak způsobuje značnou náročnost FLASH na spotřebu energie. Naproti tomu FRAM tento měnič nepotřebuje, proto je pro menší velikosti (do cca 200 kB) již dnes lepším řešením za stejnou cenu.

Snížení energetické spotřeby je obrovské. Jak toho FRAM dosahuje?

- Kromě absence napěťového konvertoru hlavně výměnou energie za čas. FRAM je prostě zásadně rychlejší. Programátor si může rozvrhnout, zda potřebuje číst rychle a vygenerovat proudovou špičku, nebo pomaleji při nízké kontinuální spotřebě.

Jaký je napěťový limit technologie FRAM?

- Zespodu je to minimum 1,5 V. Nyní uváděný čip MSP430FR57xx je sám o sobě 3 V (2 – 2,6 V).

Snažíte se říci, že MSP430FR57xx spotřebuje nejméně energie z celé řady 430?

- V aktivním režimu ano. Ve sleep módu existují některé verze MSP430, které mají ještě nižší spotřebu. To je ale způsobeno návrhem procesoru a nemá to nic společného s FRAM nebo FLASH.

Čím je dosaženo velké odolnosti proti statickému napětí?

- Technologie nám umožnila zcela vynechat železo. To znamená, že ani 50 kV v přímé blízkosti čipu nezpůsobuje bitové chyby. Standardní Flash mají zásadní problémy při 5 až 10 kV ve stejné vzdálenosti a ztrácejí data.

Obsahuje FRAM nějakou detekci a opravu chyb?

- Samozřejmě, standardní jako paměti FLASH.

To znamená automatickou opravu chyby jednoho bitu a upozornění na chybu při více chybách?

- Ano, přesně tak. FRAM blok obsahuje i vlastní CACHE atd.

Představený procesor obsahuje kromě 16 kB FRAM také 2 kB SRAM. Proč?

- 2k SRAM lze díky DMA použít jako “CACHE” pro urychlení operací s pamětí FRAM. FRAM má přístup na 8 MHz, CPU může být rychlejší = SRAM nepotřebuje wait states.

Proč jste začali s FRAM právě s procesorem?

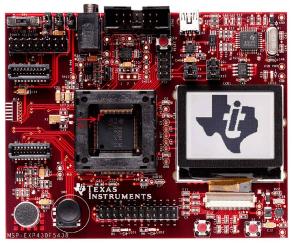

- Někde jsme začít museli. Největší přínos FRAM je právě pro měřicí aplikace, kde je MSP430 významný hráč. MSP430FR57xx je 40 pinový obvod typu VQFN o velikosti 4 x 4 mm s odhadovanou životností 80 let.

Dobře, ale 16 kB není zrovna to, co by si dnes vývojář měřicích aplikací představoval pro blok SRAM + FLASH + EEPROM.

- Při stávající technologii 130 nm lze očekávat, že do velikosti zhruba 128 až 256 kB je cenově efektivnější vyrábět nadále paměti FRAM místo FLASH v nových návrzích čipů. Další procesory budou následovat.

Děkujeme za rozhovor.

Děkujeme za rozhovor.Download a odkazy:

- Domovská stránka Texas Instruments v češtině: http://www.ti.com/ww/cz/

Komentáře

podivne informace

Precetl jsem si se zajmem tento clanek, ale obavam se, ze diky nakupeni chyb nepusobi prilis preofesionalne:

Bod 3) může te mi vysvětlit co bylove skutecnosti mineno timto textem: "...pri jejich vyjmuti ze zdroje energie vysokofrekvencniho pole behem cyklu zapisu." Behem cca 35let ve vyvoji jsem se nesetkal s potrebou vyjimat EEPROM z nejakeho vysokofrekvencniho pole a to jeste behem cyklu zapisu...

Prosim, o vysvetleni obratu: "...vsechen nezbytny proud je zajisten dopredu, jiz na zacatku zapisu dat." Vypada to jako kdyby byly v pametech FRAM integrovany kondenzatory. Je tomu tak?

Jak muze samotny 130nm proces znesnadnit pristup utocniku?

diky za reakci

Informace