Problém

![]() Při přepnutí z pasivního (třístavového) do aktivního módu mohou moderní transceivery RS-485 vykázat nespecifikované dlouhé zpoždění mezi napětím na výstupu (VOD), a povolovacím signálem řadiče (DE), pokud soufázové napětí (VCM) překročí napájecí napětí transceiveru (VCC). Toto zpoždění se významně prodlužuje s rostoucími hodnotami VCM a může vést ke ztrátě dat v klíčových aplikacích.

Při přepnutí z pasivního (třístavového) do aktivního módu mohou moderní transceivery RS-485 vykázat nespecifikované dlouhé zpoždění mezi napětím na výstupu (VOD), a povolovacím signálem řadiče (DE), pokud soufázové napětí (VCM) překročí napájecí napětí transceiveru (VCC). Toto zpoždění se významně prodlužuje s rostoucími hodnotami VCM a může vést ke ztrátě dat v klíčových aplikacích.

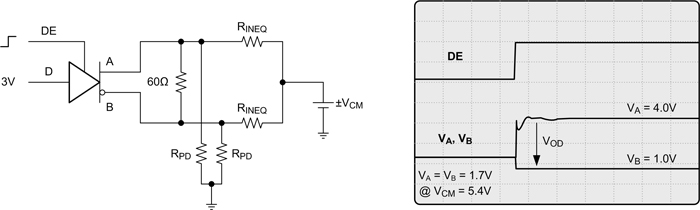

Obr. 1. Zpoždění mezi VOD a DE, pokud VCM > VCC

Časové schéma na obr. 1 ukazuje zpoždění několika set nanosekund mezi různými napětími na výstupu (VOD), a povolovacím signálem řadiče DE, když VCM (5,4 V) je vyšší než VCC (5,0 V). Ve srovnání s uvedeným příkladem se výstupní zpoždění zkrátí výrazně pod 100 ns, když VCM je rovno nebo nižší než VCC.

Hlavní příčina

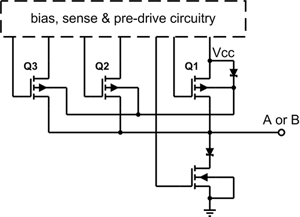

Hlavní příčina spočívá v přepěťových požadavcích struktury rozšířeného třístavového výstupu zařízení (obr 2).

Fáze výstupu se skládá ze sítě tranzistorů PMOS, které:

- produkují vysoce rozdílný signál na výstupu při nízkém napájení;

- zjišťují, zda napětí na lince (VA, VB) převyšuje napájení transceiveru;

- minimalizují svodový proud, pokud platí, že VA, VB > VCC.

Obr. 2: Struktura výstupu na transceiveru PMOS

Předpěťová sekvence zahrnuje nabití a vybití kapacitního odporu brány na interních tranzistorech PMOS FET a zejména pak nabíjení velkého kapacitního odporu brány řízení výstupů PMOS-transistorů.

V aktivním módu jsou tranzistory PMOS na výstupu nastaveny pro vedení vpřed, takže řídí přenos s malou impedancí na výstupu, která zajišťuje, že napětí na lince jsou nižší než VCC.

V pasivním módu nicméně dostávají třístavové vysokoimpedanční výstupy na svých terminálech plné soufázové napětí (VCM). Když Q3 zjistí, že soufázové napětí je vyšší než napájecí napětí (VCM > VCC), nabíjecí obvod (čárkovaný blok) nabije Q2 tak, že to přivede výstupní napětí do brány Q1, aby zabránilo zpětné kondukci.

Protože nabití brány tranzistorů PMOS FET zásadně roste pro soufázová napětí, která jsou vyšší než VCC, významně se prodlužují nabíjecí a vybíjecí časy. Proto, když to umožňuje transceiver, opakované přednabíjení výstupu do přímého vedení vede k výše zmíněnému dlouhému zpoždění.

Řešení

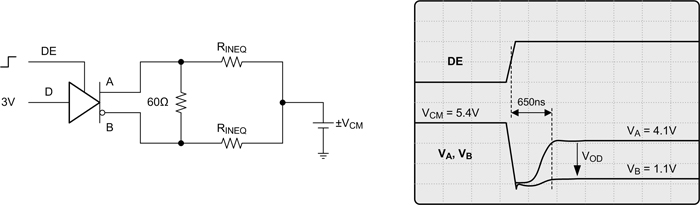

Aby se minimalizovalo zpoždění, je třeba udržovat napětí na lince pod napájecím napětím transceiveru během třístavového přepínání tím, že připojíme snižovací odpor (RPD) z každé signální linky na řídící zem. Jak je zobrazeno na obr. 3, vytváří tyto rezistory dělič napětí se vstupními impedancemi, které snižují soufázové napětí pod úroveň napájení transceiveru.

Obr 3. Snižovací odpor na lince A a B snižuje VCM pod VCC

Hodnota RPD se počítá jako ![]() , kde RINEQ je ekvivalentem vstupního odporu všech transceiverů připojených na sběrnici. Zatímco je možné zvýšit poměr rozdělení pro vyšší soufázové napětí, musí se věnovat pozornost tomu, že obdobná hodnota RPD a RINEQ je vyšší než určené maximální soufázové nabíjení ve výši 375 Ω:

, kde RINEQ je ekvivalentem vstupního odporu všech transceiverů připojených na sběrnici. Zatímco je možné zvýšit poměr rozdělení pro vyšší soufázové napětí, musí se věnovat pozornost tomu, že obdobná hodnota RPD a RINEQ je vyšší než určené maximální soufázové nabíjení ve výši 375 Ω:

![]()

Odkazy:

- Více informací o tomto tématu naleznete na www.ti.com/interface

- Domovská stránka Texas Instrumensts - zde

O autorovi

Thomas Kugelstadt pracuje jako Senior Systems Engineer ve společnosti Texas Instruments, kde je zodpovědný za vytváření nových vysokovýkonných analogových výrobků a vývoj kompletních systémových řešení, které sledují analogové signály nízké úrovně v průmyslových systémech. Během 20 let u TI působil v různých pozicích v Evropě, v Asii a v USA. T. Kugelstadt je absolventem Univerzity aplikovaných věd ve Frankfurtu.

Komentáře

Obrázky

Dobrý den.

Jestli jsem to pochopil správně, tak obrázek 1 a 3 jsou prohozeny.