Vzhledem k tomu, že se i jinak podobné systémy mohou odlišovat docela zásadním způsobem, bývá výběr konkrétního embedded procesoru s ohledem na požadavky ve věci výkonu, paměťového prostoru, rozhraní či technických parametrů dané aplikace zpravidla řazen mezi obávané úkoly nejednoho vývojáře. Třebaže bývají procesory ARM® dostupné ve více variantách, systémoví inženýři jen zřídka nacházejí ideální řešení.

Vzhledem k tomu, že se i jinak podobné systémy mohou odlišovat docela zásadním způsobem, bývá výběr konkrétního embedded procesoru s ohledem na požadavky ve věci výkonu, paměťového prostoru, rozhraní či technických parametrů dané aplikace zpravidla řazen mezi obávané úkoly nejednoho vývojáře. Třebaže bývají procesory ARM® dostupné ve více variantách, systémoví inženýři jen zřídka nacházejí ideální řešení.

V tomto článku se proto zaměříme na různá standardní rozhraní, přičemž ještě zmíníme, jakým způsobem se mohou lišit v provedení různých dodavatelů embedded čipů. Porozumění základním rozhraním pak může vývojářům pomoci při rozhodování o tom, která z nich by měla konečně být také součástí zvoleného obvodu, tzv. on-chip. Třebaže klasická rozhraní mívají v očích vývojářů velkou cenu, setkáváme se rovněž s dodatečnými požadavky na zapracovaná rozhraní s možností přizpůsobení, která by takto vhodně podpořila přídavné možnosti čipu. Článek při svém popisování rovněž pamatuje na dva z těchto periferních bloků.

USB

USB rozhraní (Universal Serial Bus) bylo původně vyvinuto s ohledem na propojení osobních počítačů s jejich periferními zařízeními. S postupem času se však stalo populárním také v rámci průmyslu, infrastruktur a souvisejících aplikací. HID (Human Interface Device) typu klávesnic, myší nebo také osciloskopů rozhraní USB běžně využívají, takže musí být ze strany systémového embedded procesoru podporováno. Nejúčinnější způsob přitom spočívá v on-chip perifériích.

Vedle HID se v rámci průmyslu, infrastruktur a souvisejících aplikací uplatňují další dvě třídy zařízení. O USB CDC (Communication Device Class) hovoříme v souvislosti s modemy a faxy, pro které bylo navrženo, přičemž rovněž podporuje jednoduché síťování z titulu poskytování rozhraní pro přenos Ethernetových paketů. Stejně tak USB MSD (Mass Storage Device), zaměřené na pevné disky a jiná úložiště.

Specifikace USB 2.0 vyžaduje host zařízení pro zahájení veškerých příchozích a také odchozích přenosů. Rovněž zde definujeme tři základní zařízení: Host kontroléry, HUBy a periférie.

Fyzickým propojením ve stylu USB 2.0 rozumíme víceúrovňovou – hvězdicovou topologii s HUBem ve středu každé z hvězd. Každý „drátový“ segment pak znamená spojení typu point-to-point mezi HOSTem a HUBem či funkcí nebo HUB propojený s dalším HUBem či funkcí (viz také článek na hw.cz s názvem USB - Universal Serial Bus - Popis rozhraní).

Adresovací schéma, použité pro jednotlivé prvky systému USB 2.0, podporuje propojení až 127 zařízení s jediným HOSTem. Těmito 127 zařízeními přitom rozumíme jakoukoli kombinaci HUBů či periférií. Složené nebo také kombinované zařízení přitom bude odpovídat za dva nebo více z těchto 127 prvků.

I když bývá USB 2.0 pravděpodobně první volbou pro průmyslové aplikace či celou řadu infrastruktur, USB On-the-Go (OTG) nasazujeme tehdy, pokud periferní zařízení vyžadují vzájemnou komunikaci bez jakékoli účasti HOSTu. Abychom však vyhověli komunikaci typu peer-to-peer, zavádí USB OTG novou třídu zařízení, zahrnujících omezené schopnosti HOSTu pro dvě periférie s ohledem na sdílení dat.

V rámci rozšíření OTG definujeme nový handshake, nazvaný HNP (Host Negotiation Protocol). Díky HNP mohou zařízení, připojená jako běžné periférie, zažádat o změnu stavu na HOST. Existujícímu modelu host – zařízení tak v rámci USB 2.0 umožníme komunikaci typu peer-to-peer. Rovněž zde definujeme protokol SRP (Session Request Protocol).

Popularita USB spolu se statutem pevného standardu umožňuje dodavatelům embedded procesorů nabízet softwarové knihovny se zaměřením na specifické funkce rozhraní a zkrátit tak čas potřebný k vývoji. Místo psaní svého vlastního kódu pro implementaci rozhraní systémoví vývojáři prostě jen volají funkci.

Knihovny by měly být certifikovány v souvislosti se zdárným ověřením shody USB zařízení a embedded HOSTu, prováděným v rámci USB Implementers Forum. Někteří výrobci, např. Texas Instruments (TI), nabízí pro své embedded procesory rozsáhlé USB knihovny.

V roce 2007 vzniklo sdružení USB 3.0 Promoter Group s cílem vytvořit rychlejší variantu USB, která bude zpětně kompatibilní s předchozími standardy USB, ale zajistí přitom 10násobek přenesených dat ve srovnání s USB 2.0. Rozhraní USB 3.0 využívá nové signalizační schéma. Zpětná kompatibilita je zase možná z titulu zachování 2drátového rozhraní USB 2.0. Přestože se již tato rychlejší varianta nachází v prvních etapách nasazování, rozhraní USB 2.0 bude pravděpodobně ještě několik let zůstávat nejoblíbenější verzí USB, nabízející přitom tři volby v otázce rychlosti:

- High-speed (480 Mbps),

- Low-speed (1,5 Mbps) a

- Full-speed (12 Mbps).

EMAC

Třebaže rozhraní vyhovující standardu IEEE 802.3 (Ethernet) bývá často nesprávně nazýváno Ethernet Media Access Controller (EMAC), bude se kompletní rozhraní subsystému EMAC ve skutečnosti skládat ze tří modulů, přičemž všechny z nich buď mohou nebo také nemusí být integrovány přímo na čipu. Jedná se o

- rozhraní fyzické vrstvy (PHY),

- Ethernet MAC, implementující vrstvu EMAC daného protokolu a

- uživatelské rozhraní, obvykle nazývané MAC Control Module.

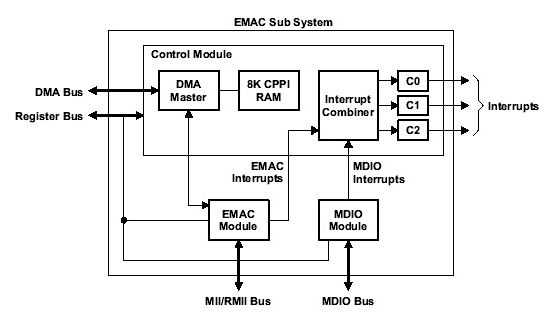

Modul EMAC řídí tok dat (paketů) ze systému do PHY. Konfiguraci PHY včetně monitorování stavu má zase na starosti modul MDIO. K systémovému jádru přistupují oba moduly prostřednictvím MAC Control Module, který rovněž optimalizuje tok dat. V plně integrovaných řešeních typu embedded procesorů od TI uvažujeme uživatelské rozhraní jako nedílnou součást periférií EMAC / MDIO.

Ucelený subsystém EMAC zachycujeme na obr. 1.

Obr. 1: Subsystém EMAC

EMAC Control Module řídí přerušení dané struktury, přičemž k udržení deskriptorů (EMAC buffer) využívá 8 K interní RAMku (Random Access Memory). Modulem MDIO zase realizujeme rozhraní sériového managementu 802.3 pro podrobné zkoumání a také řízení až 32 Ethernetových PHY, připojených k obvodu prostřednictvím sdílené 2drátové sběrnice.

Host software využívá modul MDIO pro konfiguraci parametrů automatického dialogu pro každou PHY připojenou k EMAC, získává výsledky takového jednání a konfiguruje požadované parametry v modulu EMAC s ohledem na bezchybnou činnost. Modul byl navržen tak, aby umožnil téměř transparentní chod rozhraní MDIO s velmi malou péčí ze strany jádra procesoru.

S moduly EMAC zajistíme účinné rozhraní mezi procesorem a sítí. Takové moduly zpravidla nabízí 10Base-T (10 Mbitů/s) a 100BaseTX (100 Mbitů/s), režim polovičního a také plného duplexu či podporu hardwarového řízení toku nebo QoS (Quality-of-Service). Některé procesory kromě toho nyní podporují gigabit EMAC, tj. rychlost přenosu dat 1000 Mbitů/s.

Protože je Ethernet tak široce nasazován, budou embedded procesory na svých čipech zpravidla nabízet také jedno nebo více rozhraní EMAC. Existují však určité rozdíly ve způsobech, kterými různí dodavatelé realizují ucelený subsystém EMAC, popsaný výše. Kvalita včetně rozsahu softwarové podpory a knihoven pro implementaci Ethernetu se tak stává dalším faktorem při výběru konkrétního výrobce embedded procesoru.

Některé aplikace, jako například routery či switche, budou někdy vyžadovat více než jedno EMAC. S využitím vícenásobného EMAC pak mohou tyto aplikace okamžitě komunikovat s četnými zařízeními, vytvářejíce přitom synchronizovaný proces komunikace.

SATA

Sběrnice serial ATA (SATA) slouží k propojení sběrnicových adaptérů (Host) s velkokapacitními paměťovými prostory typu pevných disků či optických mechanik. Prakticky tak nahradila svého předchůdce – parallel ATA (PATA), který vyžadoval 40/80 žilový paralelní kabel, jehož délka nemohla překročit 18 palců. Maximální rychlost přenosu dat činila v případě PATA 133 Mbyte/s, zatímco sériový datový formát SATA využívá při podpoře rozhraní datových úložišť dvou rozdílových párů s linkovými rychlostmi

- 1,5 Gbitů/s (SATA Revision 1),

- 3,0 Gbitů/s (SATA Revision 2) a

- 6,0 Gbitů/s (SATA Revision 3).

Možnosti SATA 1 a SATA 2 lze využívat již dnes, potenciál SATA 3 pak již v blízké budoucnosti.

Kontroléry SATA rovněž definují tenčí kabely, dlouhé dokonce tři stopy (1 stopa = 12 palců, pozn. překl.). S tenčími kabely jde také ruku v ruce flexibilita, tzn. jednodušší vedení tras a lepší ventilace uvnitř krytu velkokapacitního zařízení.

Sériová linka částečně dosahuje své vysoké výkonnosti díky implementování pokročilé struktury systémové paměti, přizpůsobené vysokorychlostním sériovým datům. Paměťová struktura

- AHCI (Advanced Host Controller Interface)

obsahuje generickou oblast pro řízení, status a datovou tabulku seznamu příkazů. Každý záznam v tabulce seznamu příkazů zahrnuje informaci pro programování zařízení SATA stejně jako ukazatel na tabulku deskriptoru pro přenos dat mezi systémovou pamětí a daným zařízením.

Většina SATA kontrolérů podporuje výměnu za provozu (Hot Swapping) a také využití multiplikátoru portu pro zvýšení počtu zařízení, která lze připojit k jedinému portu HBA. Standard SATA definuje dlouhý seznam vlastností, ale jen málo SATA kontrolérů podporuje všechny z nich. Mezi oblíbené rysy řadíme:

- podporu AHCI kontroléru, spec. 1.1

- integrovaný SERDES PHY

- integrované datové buffery (Rx a Tx)

- podporu prvků řízení napájení SATA

- interní jednotku DMA (na port)

- NCQ (Native Command Queuing) s hardwarovou asistencí až pro 32 položek

- 32bitové adresování

- podporu multiplikátoru portu

- podporu LED aktivity

- switch mechanické přítomnosti

Protože s využitím SATA dokážeme ukládat data až do TB rozsahu, bude tato sběrnice velmi úspěšně nasazována v aplikacích typu netbooků, laptopů, desktopů (stolních počítačů), multimediálních zařízení či přenosných datových terminálů. S označením SATA se lze rovněž setkat v rámci průmyslových aplikací, kde mohou senzory či systémová monitorovací zařízení vyžadovat ukládání většího množství dat pro analýzu v pozdějším čase.

Dokončení příště.