Už vím jak na vstupy a výstupy klasických rozhraní – 1.část

DDR2 / Mobile DDR

DDR2 je pokračováním specifikace DDR (Double Data Rate) SDRAM – dva standardy však nejsou kompatibilní. Přenosem dat na vzestupné a sestupné hrany sběrnicového taktovacího signálu a také provozem na vyšších rychlostech sběrnice dosahujeme s DDR2 celkem čtyř datových přenosů na interní hodinový cyklus.

DDR2 je pokračováním specifikace DDR (Double Data Rate) SDRAM – dva standardy však nejsou kompatibilní. Přenosem dat na vzestupné a sestupné hrany sběrnicového taktovacího signálu a také provozem na vyšších rychlostech sběrnice dosahujeme s DDR2 celkem čtyř datových přenosů na interní hodinový cyklus.

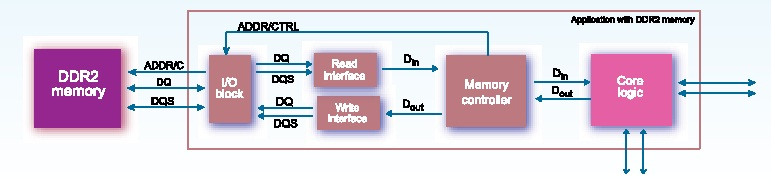

Zjednodušené rozhraní kontroléru DDR2 zahrnuje následující designové bloky:

- Řízení paměti,

- rozhraní pro čtení,

- rozhraní pro zápis a

- IO blok.

Zmíněné bloky a jejich spojitost s paměťovým čipem DDR2 nebo logikou jádra zachycuje obr. 2.

Obr. 2: Zjednodušené provedení kontroléru DDR2

Blok řízení paměti vystavuje přístupy z paměti do logiky aplikačně specifického jádra nebo obráceně. Fyzický blok čtení řeší časování vnějšího signálu v souvislosti se zachytáváním dat během čtecích cyklů. Fyzický blok zápisu zase řídí vystavení taktu a dat spolu s náležitým časováním vnějšího signálu.

Obousměrná synchronizace dat (DQS) široká jeden bajt je přenášena externě spolu s daty (DQ) pro zachycení. Za přispění kontroléru se DQS přenáší během čtení s orientací na hranu, resp. střed v průběhu zápisu. Vestavěné DLL (Delay-Lock Loop) se pak využívají při „registrovaném odchodu“ DQS a příslušných DQ, takže lze zaručit možnost vzájemného sledování pro případ napěťových nebo také teplotních změn.

SRAM DDR2 mají k dispozici hodinové vstupy v rozdílovém provedení, čímž omezují dopad odchylek pracovního cyklu vstupního taktování (viz také článek Jednoduchý návrh hodinového bufferu s malým šumem, vydaný na hw.cz). SRAM DDR2 dále podporují signály, určené pro maskování datových bitů během cyklů zápisu.

- Mobile DDR (MDDR),

obvykle nasazované v přenosných elektronických zařízeních, rovněž označujeme jako paměti LPDDR (Low Power Double Data Rate), protože v protikladu k běžnějším 2,5 V či 3,3 V pracují již na 1,8 V. Paměti Mobile DDR také podporují nízkopříkonové stavy, které na tradičních pamětech DDR2 nenajdeme. Stejně jako u všech DDR i zde dosahujeme onoho „Double Data Rate“ přenosem dat na obě hrany hodinového signálu dané struktury.

uPP

Díky celé řadě zapracovaných periférií, omezených buď cenou či jinými limitujícími faktory, mívají vývojáři častou snahu nacházet neobvyklá řešení přesunu dat na a také ven z daného čipu. Jednou z možností je třeba zapojení jinak nevyužitého video portu, tj. v zásadě realizace určitého „podfuku“, při kterém budeme na vysokých rychlostech vysílat a také přijímat data, která však s videem nemají nic společného. Jedním ze záporů takového přístupu je ale nutnost formátovat data do video rámců, což vyžaduje určité „MIPSy“ procesoru během jeho činnosti a také drahocenný čas programátorů během vývojové fáze.

Další metody znamenají obdobné nesnáze, přičemž většinu standardních on-chip datových rozhraní tvoří sériové porty se kterými nezpracujeme vysokorychlostní přenosy.

Ve výsledku tak spousta vývojářů spatřuje velký význam ve flexibilních vysokorychlostních perifériích a to především pro přenosy dat, které nevyhovují konkrétnímu standardu rozhraní, ale lze je nakonfigurovat hned několika způsoby. Zejména to pak platí tehdy, budeme – li muset systémový procesor propojit s vysokorychlostními DAC, ADC, DSP nebo dokonce FPGA se schopností vysokorychlostních datových přenosů v řádu 250 MB/s.

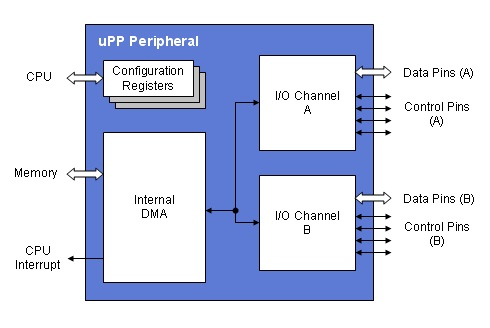

Popis základní architektury takových periférií není vůbec složitý: Mělo by zde být více kanálů s různými, paralelními datovými sběrnicemi, které lze konfigurovat a přizpůsobit tak délce více než jednoho wordu. Rovněž by potěšil interní blok DMA, takže činnost může pokračovat bez odčerpávání „MIPSového rozpočtu“ použitého jádra. Mezi žádoucí vlastnosti také patří jednoduché nebo dvojnásobné rychlosti přenosu dat spolu s větším počtem formátů pro nakládání s číslicovými údaji.

uPP (Universal Parallel Port) je dostupný na celé řadě embedded procesorů TI včetně mikroprocesorů (MPU) Sitara™ ARM9 AM1808 a AM1806 nebo procesorů OMAP-L138 s jádry TMS320C674x a ARM9. Na rozdíl od sériových periférií typu SPI či UARTů nabízí uPP pro vývojáře výhody paralelní datové sběrnice o šířce 8 až 16 bitů na kanál.

Budeme – li pracovat s maximálním taktem 75 MHz, přeneseme data s uPP mnohem rychleji než v případě periférií se sériovými porty. Tak například, jediný 16bitový kanál uPP, pracující na 75 MHz, bude dokonce 24x rychlejší než periférie SPI, provozovaná na 50 MHz.

Zjednodušený blokový diagram vidíme na obr. 3.

Obr. 3: Zjednodušený blokový diagram uPP

Mezi nejdůležitější vlastnosti uPP řadíme:

-

Dva samostatné kanály s oddělenými datovými sběrnicemi

- Kanály mohou souběžně pracovat ve stejných či opačných směrech

- Rychlost I/O až do 75 MHz s datovou šířkou 8 až 16 bitů na kanál

- Interní DMA – volnost pro EDMA CPU

- Jednoduchý protokol jen s několika řídicími piny (konfig.: 2 až 4 na kanál)

-

Jednoduché a dvojnásobné rychlosti přenosu dat (využívá jednu nebo také obě hrany taktovacího signálu)

- Double data rate zavádí max. takt 37,5 MHz

- Četné formáty (Data Packing) pro datové šířky 9 až 15 bitů

- Režim prokládaných dat (pouze jeden kanál)

uPP vykazuje určitou podobnost s další periférií (TI), vyhrazenou konfigurovatelné práci s daty –

- HPI (Host Port Interface).

V případě HPI hovoříme o paralelním rozhraní, umožňujícím externímu hostu přímý přístup do paměti uvnitř procesoru. uPP však na rozdíl od HPI neposkytuje přímý přístup do paměti externích obvodů, takže budeme pro I/O přenosy potřebovat frontu, řešenou příslušným softwarem. Snad největší odlišnost pak spočívá v tom, že uPP bude výrazně rychlejší než HPI a má mnohem jednodušší protokol.

uPP využijeme především v aplikacích, vyžadujících off chip zpracování v reálném čase – např. FPGA či DSP, takže bude znamenat výrazný prospěch pro systémy, požadující okamžitá data, např. v medicíně. Díky uPP pak můžeme realizovat procesory, které vhodně podpoří moderní způsoby práce s daty.

PRU

PRU (Programmable Real-time Unit) je malou 32bitovou jednotkou, která přímo na čipu nabídne přídavné možnosti zpracování v reálném čase. Na základě exkluzivního nasazení v embedded procesorech TI – MPU AM1x či OMAP-L138 může PRU vývojářům zajistit mimořádnou úroveň flexibility spolu s typickým snížením ceny součástek.

Architektura čtyř sběrnic PRU umožňuje vyvolání a také vykonání instrukcí souběžně s přenosy dat. Vstupní registr kromě toho umožňuje odrážet informaci o vnějším stavu ve stavovém registru interního procesoru.

Při návrhu PRU byl kladen důraz na takový rozsah flexibility, jak jen to bude při vykonávání širokého rozsahu funkcí možné. Flexibilita PRU umožňuje vývojářům zapracovat do svých koncových produktů přídavná rozhraní – ať již to bude dotykový panel, integrované displeje či možnost ukládání dat s ohledem na další rozšiřování vlastních potenciálů nebo možností jimi chráněných rozhraní. Úkol se pak v případě PRU podařilo z velké části splnit zajištěním plné systémové viditelnosti včetně veškeré systémové paměti, I/O a přerušení.

Třebaže se jedná o vyčerpávající přístup k systémovým prostředkům, budou interní zdroje PRU relativně skromné. Jedná se o 4 Kbyte paměti pro instrukce a 512 byte paměti pro data. PRU rovněž nabídne svá vlastní GPIO s čekací dobou, měřenou v řádech ns.

PRU lze programovat jednoduchým assembl. kódem (implementace zákaznické logiky). Instrukční soubor přitom dělíme na čtyři základní kategorie:

- Přesun dat do nebo také ven z interních registrů procesoru

- Provádění aritmetických operací

- Provádění logických operací

- Tok řídicího programu

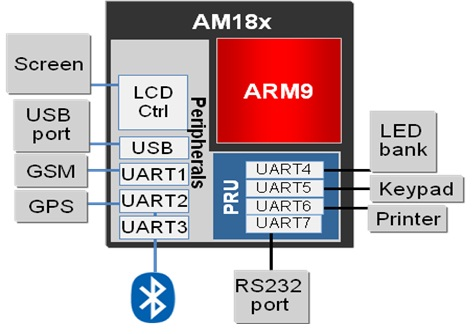

V průmyslových aplikacích se s PRU často setkáváme na pozici IO bloku, zastupujícího IO, které v rámci procesoru nebudou dostupné. Může se například jednat o přenosné datové terminály, vyžadující kombinaci UART bloků a připojení GSM, GPS a Bluetooth, klávesnice, tiskárny, banky LED či portu RS232. Zatímco však v případě nejlepšího možného výběru z dostupné rodiny procesorů obdržíme UARTy pouze tři, lze díky PRU zajistit přídavná rozhraní – UARTy a poradit si tak s potřebami vyvíjejících se koncových zařízení, resp. elegantně zvládnout všechny typy funkcí (viz také článek Caribouboard – platforma pro vývoj náročných aplikací).

Obr. 4: Nasazení PRU s ohledem na rozšíření možností periférií současných obvodů

Kromě náhrady IO lze PRU dále naprogramovat k vykonávání různých forem řízení, monitorování či dalších funkcí, které jinak na čipu nemáme k dispozici. Takovou flexibilitu pak oceníme zejména v aplikacích s požadavky na řízení, které nelze realizovat v rámci dostupných konfigurací kteréhokoli běžného procesoru.

Integrace subsystému ARM a periférií

Hodnotíme – li periferní rozhraní procesoru založeného na ARM, musíme porozumět tomu, jakým způsobem začlenit periférie včetně ARM subsystému.

Procesory ARM jsou vhodné pro složité, multi – taskingové a univerzální řídicí úlohy. Máme zde k dispozici velkou paměť programu a také solidní schopnosti ve věci přepínání kontextu. Vyhovují tak běhu RTOS (Real Time Operating System) či sofistikovaných HLOS (High Level Operating System). ARM zde odpovídá za konfiguraci systému a řízení, což zahrnuje konfiguraci periférií a řízení, řízení taktu, inicializaci paměti, ovládání přerušení, řízení napájení atd. Subsystém ARM přitom zahrnuje procesor ARM včetně dalších částí, nezbytných k tomu, aby procesor ARM vystupoval jako master celkového procesorového systému.

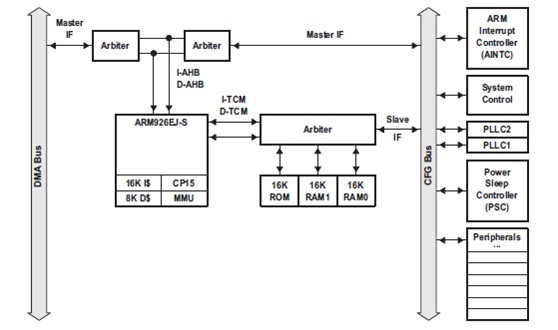

Typický subsystém ARM se skládá z kombinací následujících částí:

-

Jádro ARM (např. ARM926EJ-S nebo ARM Cortex-A8™)

- Koprocesor 15 (CP15)

- MMU

- Write Buffer

- Instruction CACHE

- Data CACHE

- Java accelerator

- SIMD koprocesor (Neon Single Instruction Multiple Data)

- VFP koprocesor (Vector Floating Point)

-

Interní paměti ARM

- RAM

- ROM (ARM boot loader)

-

Prvky, rozhodující o přidělení sběrnice (Arbitr)

- Sběrnicové prvky pro přístup k interním pamětem

- Sběrnicové prvky pro přístup k řídicím registrům systému a periférií

- Sběrnicové prvky pro přístup k externím pamětem

-

Moduly pro ladění, trasování a emulaci

- JTAG

- ICECrusher™

- ETM (Embedded Trace Macrocell)

-

Systémové řídicí periférie

- ARM ICM (Interrupt Control Module)

- PLL (Phased-Lock Loop) a CCM (Clock Control Module)

- PMM (Power Management Module)

- SCM (System Control Module)

Na obr. 5 vidíme blokový diagram typického subsystému ARM, vycházejícího z ARM9.

Obr. 5: Blokový diagram subsystému ARM

V případě periférií typu USB, EMAC, SATA, uPP či PRU bude mít subsystém ARM přístup k periferním řídicím a konfiguračním registrům, souvisejícím hodinám a také řízení napájení.

Závěr:

Přestože hrají standardní rozhraní kritickou úlohu v konstrukčních systémech, které budou schopné spolupráce, levné a také rychleji vyvinutelné, je jejich prospěšnost v případě týmů, které budou chtít své produkty nějak odlišit, stále limitována. Vývojáři by se proto měli seznámit s celkovou nabídkou svého dodavatele čipů ve věci celé řady standardních rozhraní i jejich nejrůznějších kombinací. Mezi další odlišující faktory při výběru výrobce polovodičů pak řadíme vysokou kvalitu softwarových knihoven, které účinně pomohou implementovat zvolené rozhraní. Hodí se také nabídka přídavných stupňů flexibility, na kterou dosáhneme konfigurovatelnými rozhraními typu

- PRU a

- uPP

od TI. S takovými možnostmi ve své sadě nástrojů si mohou systémoví vývojáři zachovat svou kreativitu, zatímco současně udrží cenový rozpočet v přijatelných mezích.

Autoři článku: Clay Turner, James Doublesin, Lawrence Ronk a Steve Kipisz, Texas Instruments