Úvod

V posledních letech dochází ke zvýšené poptávce vícečlánkových lithium-iontových (Li-Ion) baterií pro celou řadu aplikací, ze kterých zmíníme např. elektrické nářadí, zálohované napájecí zdroje (UPS) nebo hybridní vozidla s elektrickým pohonem. Primární pozornost se přitom v rámci těchto systémů věnuje zejména bezpečnosti. Přepěťová ochrana druhého stupně je součástka, používaná pro další zlepšení celkové bezpečnosti dané aplikace. Je připojena ke každému článku současně s primární ochranou, aby kontrolovala, zda napětí baterie nepřesahuje předepsanou úroveň. Jestliže se vyskytne přepětí a primární ochrana systému z nějakého důvodu selže, ochrana druhého stupně obvykle přepálí pojistku nebo sepne ochranný tranzistor FET s cílem zabránit rizikové situaci. Hlavním hodnotícím kritériem pro ochranu druhého stupně jsou celkové náklady, spotřeba energie a také nejvyšší napětí, které takový integrovaný obvod ještě snese.

V posledních letech dochází ke zvýšené poptávce vícečlánkových lithium-iontových (Li-Ion) baterií pro celou řadu aplikací, ze kterých zmíníme např. elektrické nářadí, zálohované napájecí zdroje (UPS) nebo hybridní vozidla s elektrickým pohonem. Primární pozornost se přitom v rámci těchto systémů věnuje zejména bezpečnosti. Přepěťová ochrana druhého stupně je součástka, používaná pro další zlepšení celkové bezpečnosti dané aplikace. Je připojena ke každému článku současně s primární ochranou, aby kontrolovala, zda napětí baterie nepřesahuje předepsanou úroveň. Jestliže se vyskytne přepětí a primární ochrana systému z nějakého důvodu selže, ochrana druhého stupně obvykle přepálí pojistku nebo sepne ochranný tranzistor FET s cílem zabránit rizikové situaci. Hlavním hodnotícím kritériem pro ochranu druhého stupně jsou celkové náklady, spotřeba energie a také nejvyšší napětí, které takový integrovaný obvod ještě snese.

Integrované ochrany druhého stupně (dále jen IO) jsou obvykle navrhovány pro dva až šest článků, řazených do série. S rostoucím počtem článků v bateriové sestavě proto s jedinou integrovanou ochranou druhého stupně všechny dílčí zdroje nepokryjeme. Musíme tedy nasadit více IO a výstup každého z nich, za přispění vnějších součástek, příslušným způsobem vyhodnotit. Jiným řešením je použití speciálních IO s komunikačními kanály pro přenos chybového signálu. Tento postup ale může vést k nárůstu ceny celého systému a také zvýšení vlastní spotřeby. Následující text proto přináší řešení v otázce kaskádního návrhu přepěťové ochrany druhého stupně (Stacked Second-Level Overvoltage Protector) pro vícečlánkové baterie s využitím několika IO, aniž by se přitom neúměrně zvyšoval počet vnějších součástek nebo rostla spotřeba energie.

Předpoklady a popis funkce

Pro účely příkladu v tomto článku vyjdeme z chemického složení baterie a způsobu jejího použití. Využijeme přitom sekundární, integrované přepěťové ochrany BQ2941x [1], kde x rozlišuje velikost prahového, spouštěcího napětí. Prvky jsou navrženy pro dva až čtyři články v sérii a v klidovém stavu vykazují velmi malou proudovou spotřebu o velikosti 2 μA. Výstupy všech IO lze ke společnému výstupu (Alarm) navázat např. pomocí optočlenů [2]. Tento způsob je ale složitější a také celé řešení prodraží. My se proto vydáme jinou cestou a přeneseme chybový signál z horního IO na IO pod ním a analogicky budeme postupovat až k poslednímu použitému obvodu takto vytvořené kaskády.

Uvedené zjednodušené řešení používá výstupní chybový signál z horního IO této sestavy jako vstupu pro IO pod ním. Celou techniku názorně demonstruje použití několika sekundárních přepěťových ochran BQ2941x. U těchto IO představují VC1 až VC4 vstupy jednotlivých článků. Výstupní chybový signál je pak k dispozici na pinu OUT. Časové zpoždění mezi vznikem chyby a příslušným náběhem výstupního chybového signálu je definováno vnější kapacitou, připojenou k pinu CD.

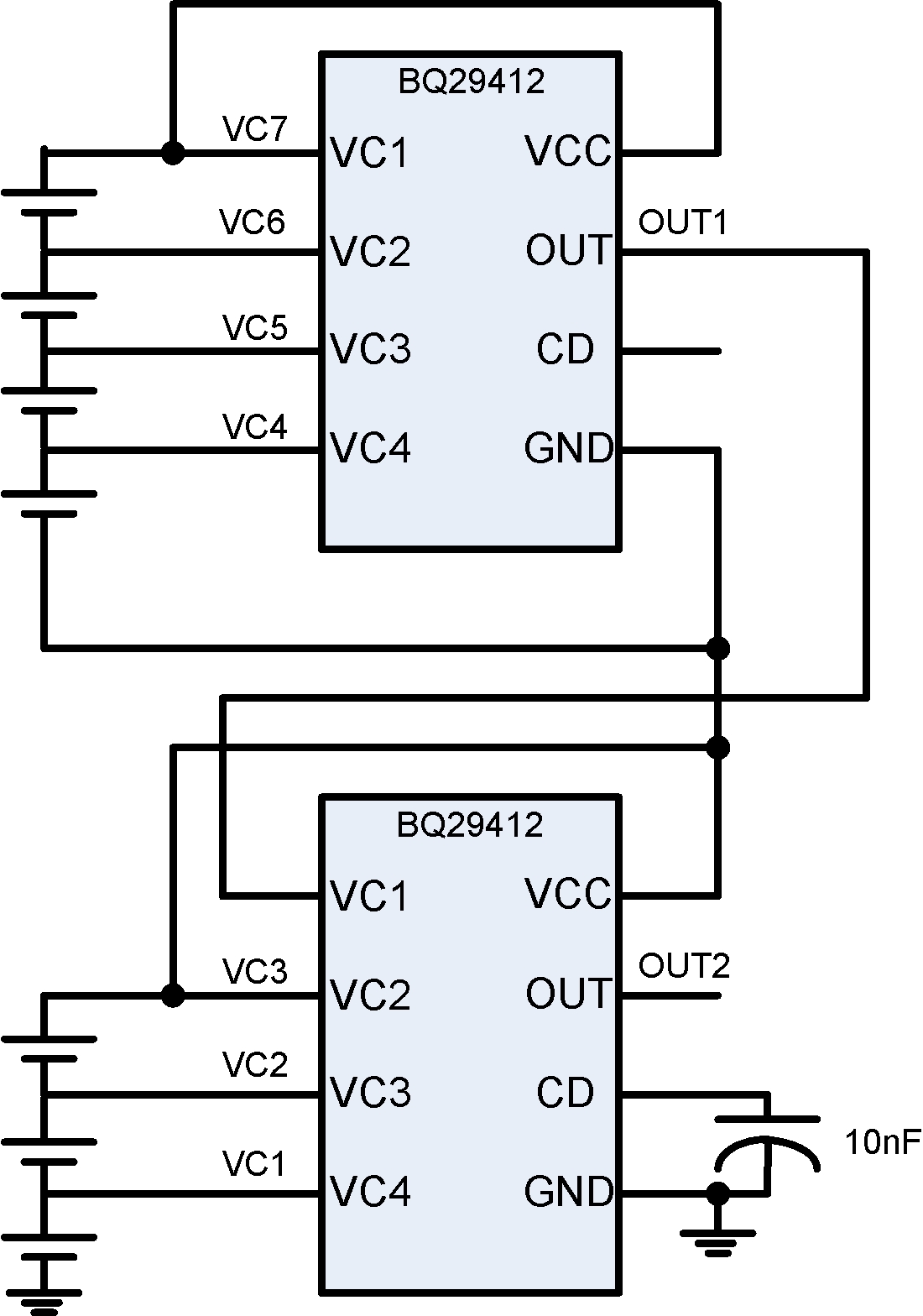

Obr. 1 ukazuje schéma zapojení dvou přepěťových ochran druhého stupně s kaskádním řazením. Výstup OUT horního IO je připojen na vstup VC1 spodního IO. Pin CD horního IO zůstane nezapojený nebo se zatíží velmi malou kapacitou (<1 nF). Pokud bude napětí kteréhokoli článku pod danou spouštěcí hladinou, je výstup OUT držen na nízké úrovni. Při normálním provozu (tj. když nedochází k chybě) je napěťová úroveň signálu OUT horního IO rovna potenciálu bodu VC3, který zde definuje zem GND. V tomto důsledku se na spodním IO nevyskytuje chybový stav. Při poruše dojde na výstupu OUT k nárůstu napětí. Logická jednička má pro tento IO jmenovité napětí 7 V [2], což je mnohem více než definovaný přepěťový práh. Jakmile tedy horní IO detekuje chybu, může být signál OUT použit pro vytvoření chybového signálu na spodním IO, kde rovněž způsobí přechod výstupu OUT do vysoké úrovně. Tuto techniku lze pochopitelně využít i pro větší počet IO a šířit tak informaci o chybě od kteréhokoli IO v sestavě až k poslednímu prvku v řadě.

Časové zpoždění systému definuje kondenzátor, připojený ke spodnímu IO. Kaskádní systém, uvedený na obr. 1, může chránit bateriovou sestavu sedmi sériově spojených článků (7S). Každý další IO přepěťové ochrany druhého stupně může chránit další tři články v sérii (3S). Pro potvrzení této teorie byl systém prověřen v simulačním prostředí s následným jednoduchým experimentem.

Obr. 1: Schéma zapojení, zachycující dva IO přepěťové ochrany druhého stupně s kaskádním řazením. Celkem tak lze chránit až sedm sériových článků.

Simulace a charakteristické výsledky

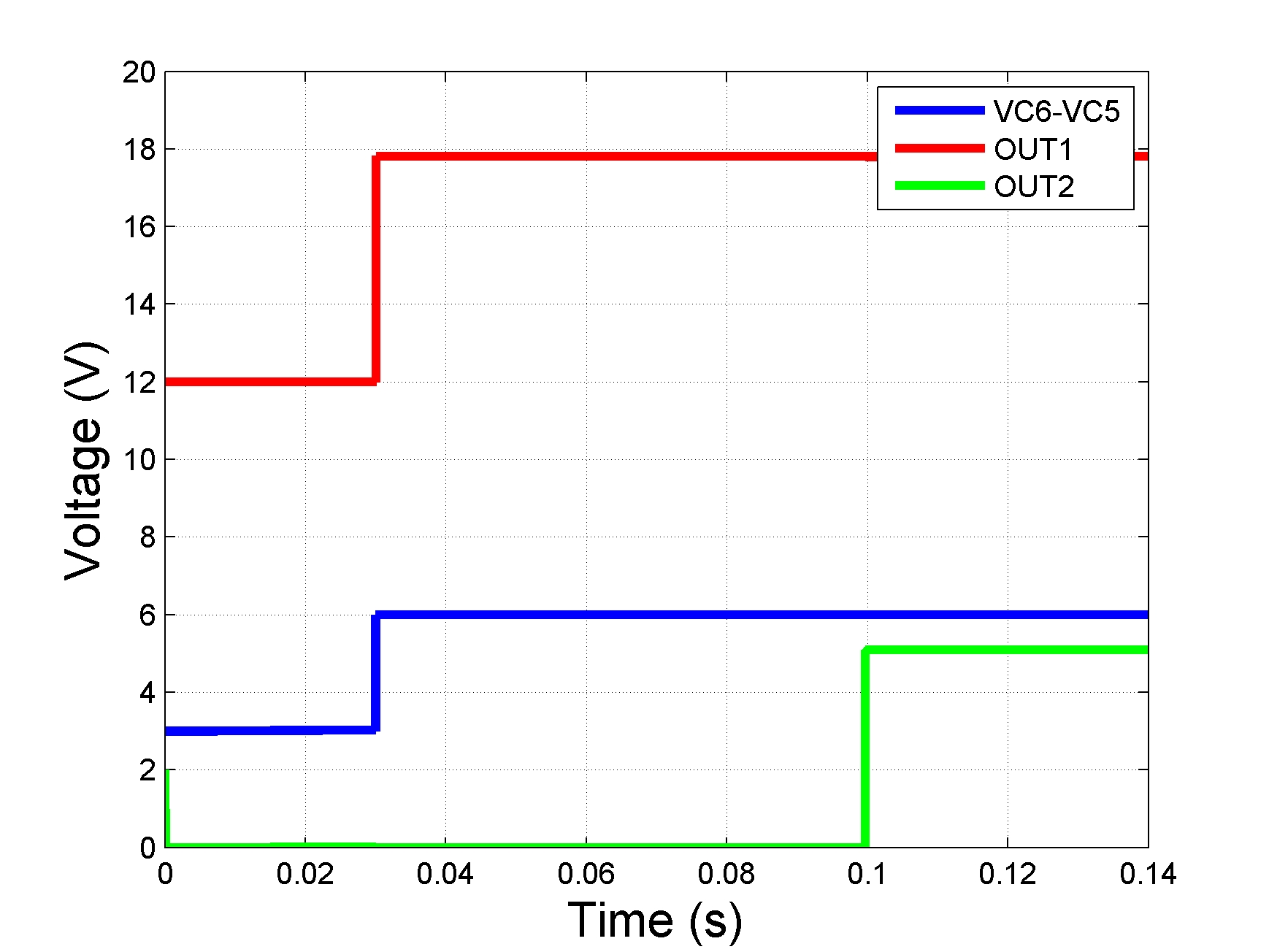

K simulaci obvodu na obr. 1 byl použit SPICE model na úrovni jednotlivých tranzistorů. Výsledky zachycuje obr. 2. Pro účely simulace se napětí každého článku udržovalo pod spouštěcí úrovní. Chybové podmínky byly simulovány tak, že se napětí druhého článku horního IO (VC6 – VC5) změnilo na 5 V. Signál OUT spodního IO poté přechází do logické jedničky, čímž svému okolí signalizuje přepětí. Napětí na výstupu horního IO přechází do log. 1 s velmi malým zpožděním. Následně stejným způsobem roste i napětí na výstupu OUT spodního IO. Zanedbatelné zpoždění horního IO určuje parazitní kapacita spolu s malým kondenzátorem, připojeným k pinu CD. Zpoždění výstupu OUT dolního IO, tj. ~68 ms, je zase podmíněno kondenzátorem (10 nF), připojeným k pinu CD dolního IO.

Obr. 2: Výsledek simulace s využitím SPICE modelu přepěťové ochrany. Průběh zachycuje napětí na článku (VC6-VC5) a také oba výstupní signály OUT z horního i dolního IO.

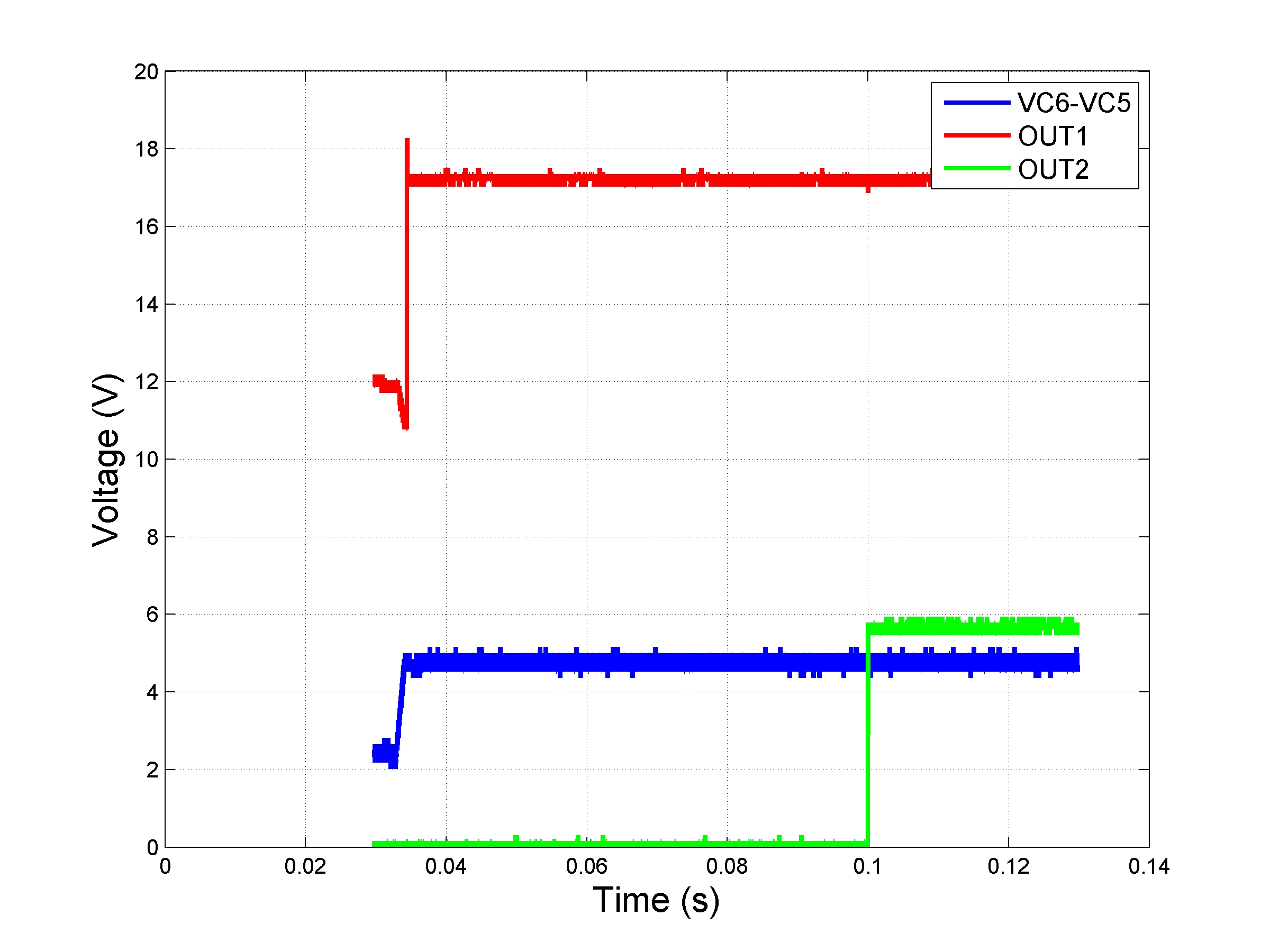

Obr. 3: Experimentální výsledky kaskádního řazení sekundární přepěťové ochrany v integrovaném provedení. Opět zde vidíme napětí na článku (VC6-VC5) a výstupní signály OUT z obou IO.

Obr. 3 zachycuje experimentální výsledky. Je zobrazen rozdíl napětí mezi uzly VC5 a VC6. Napětí na článku přechází ze jmenovité úrovně 2.5 V až na 5 V, čímž vzniká stav přepětí. Na stejné časové ose jsou rovněž zachyceny výstupní signály OUT z obou IO. Signál OUT horního IO přechází v důsledku malé kapacity na jeho vývodu CD na vysokou úroveň prakticky okamžitě. Signál dolního IO zase přechází na log. 1 s určitým zpožděním. Celková prodleva pak činí přibližně 65 ms (podmíněno kondenzátorem 10 nF, připojeným k pinu CD dolního IO). Doba zpoždění tedy velmi dobře odpovídá výsledkům simulace na obr. 2.

Pro kaskádní konfiguraci je důležité, aby velikost klidového proudu byla, pokud možno, stejná jako v případě jediného IO. Bylo ověřeno, že proudový odběr z bateriové sestavy byl pro jeden i pro konfiguraci dvou IO přibližně roven 2 μA, což odpovídá publikovaným specifikacím v datovém listu.

Závěr:

Článek stručně zmiňuje přepěťové ochrany druhého stupně i způsob, který řadí několik IO tak, abychom mohli sledovat větší počet monitorovaných bateriových článků. Zmíněného cíle tak lze dosáhnout bez zbytečného nárůstu počtu vnějších součástek i vlastní proudové spotřeby. Celá myšlenka byla nejprve simulována a poté také s úspěchem experimentálně ověřena.

Reference:

- [1] “Voltage Protection for 2-, 3-, or 4-Cell Li-Ion Batteries (2nd-Level Protection),” Data Sheet, Texas Instruments, 2005: www.ti.com/bq29410datasheet-ca

- [2] Williams, Doug, “Stacking Multiple bq2941x Li-Ion Secondary Voltage Protectors,” Application Report, Texas Instruments, SLUA434, August 2007: www.ti.com/bq2941xappnote-ca

Něco o autorech:

- John Carpenter, Jr., je Senior Design Engineer a Supervisor, zodpovědný za integraci na systémové úrovni a také za různorodé návrhy IO pro aplikace se smíšenými signály v procesech BICMOS. Získal titul MSEE a BSEE na University of South Florida, Gainesville. John je držitelem 11 patentů a je Senior Member of IEEE, Senior Member Technical Staff ve společnosti Texas Instruments a Qualified Naval Engineering Duty Officer pro US Navy Reserves.

- Karthik Kadirvel je návrhář obvodů, zodpovědný za návrh a charakteristiky IO pro analogové a smíšené signály. Karthik získal titul PhD na University of Florida, Gainesville a je členem IEEE.

- Robert Taylor je Applications Engineer a Member Group Technical Staff ve společnosti Texas Instruments, kde má na starosti referenční výkonové návrhy pro zákazníky s hromadnými objednávkami. Robert získal titul MSEE a BSEE na University of Florida, Gainesville.