Neustále se hledá návrh systému, který by poskytoval optimální výpočetní výkon pro různě náročné aplikace. V mnoha situacích se obrátíme na programovatelné hradlové pole - FPGA, ale mnoho lidí neumí FPGA správně implementovat do systému. Tento článek stručně popisuje postup návrhu takového systému, který může těžit z výhod FPGA.

Proč používat FPGA?

Existuje celá řada výpočetních aplikací, na které se hodí různý typ hardware. Například běžně dostupné mikroprocesory (MPU), mikrokontroléry (MCU), grafické procesory (GPU), FPGA nebo SoC čipy. Rozhodnutí, který typ hardware použijeme k dané aplikaci vyžaduje podrobnou analýzu.

Například pro stanice 5G se musíme počítat s tím, že základní standardy a protokoly se stále vyvíjejí. To znamená, že se stanice musí rychle a efektivně přizpůsobit jakékoli změně. Podobně je nutné reagovat na neočekávané chyby ve funkčnosti systému, díry v zabezpečení systému, upravovat stávající funkce nebo přidávat nové funkce, aby se prodloužila životnost celého systému.

Co se týče výkonu, tak to je často vyřešeno použitím SoC čipu. Toto řešení je drahé a časově náročné. Všechny algoritmy, které jsou implementovány do struktury čipu, jsou v podstatě „zamrznuty v křemíku“. Tato nepružnost se stává problémem, jelikož je nutné mít systém flexibilní. Aby bylo možné najít kompromis mezi optimálním výkonem a flexibilitou je nutné zvolit alternativu. Například použít kombinaci mikroprocesorů / mikrokontrolérů a FPGA nebo FPGA, které mají v sobě jádra procesoru integrovány.

Co je FPGA?

Jednoduchá odpověď – Programovatelné hradlové pole. Pod tímto výrazem, ale existuje mnoho různých typů FPGA a každé z nich má různé schopnosti a funkce.

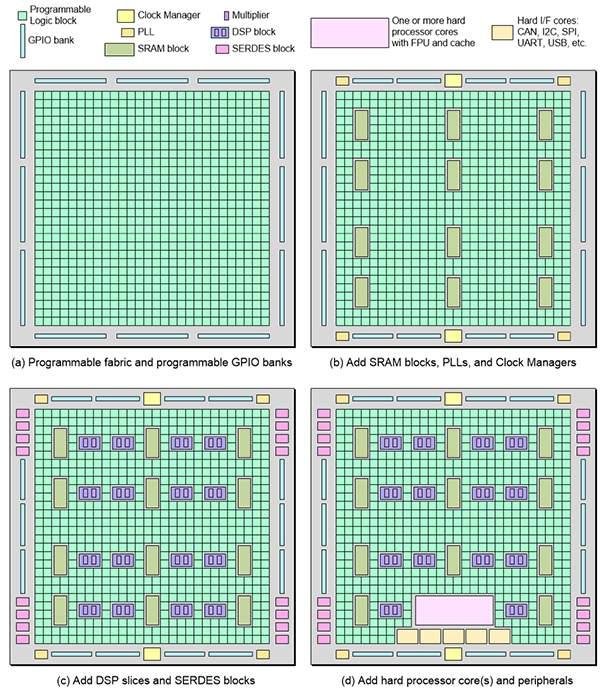

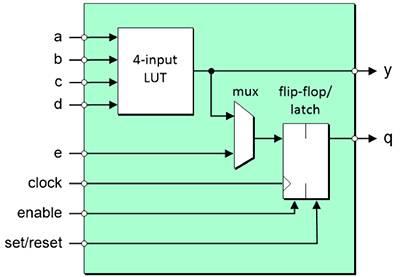

Srdcem každého FPGA je programovatelná struktura, která je reprezentována jako řada programovatelných logických bloků (obrázek 1a). Každý z těchto logických bloků obsahuje vyhledávací tabulku (LUT), multiplexor a registr. Vše lze nakonfigurovat (naprogramovat) tak, aby fungovaly dle potřeby (obrázek 2).

Obrázek 1: Nejjednodušší FPGA obsahuje pouze programovatelnou strukturu a konfigurovatelné GPIOS (a). Různé architektury rozšiřují tuto základní strukturu o bloky SRAM, PLL a správce hodin (b), bloky DSP a rozhraní SERDES (c) a jádra procesorů a periferie (d). (Zdroj obrázku: Max Maxfield)

Obrázek 2: Každý programovatelný logický blok obsahuje vyhledávací tabulku, multiplexor a registr. Každou část lze nakonfigurovat (naprogramovat) tak, aby fungovaly podle potřeby. (Zdroj obrázku: Max Maxfield)

Mnoho FPGA používá 4-vstupovou vyhledávací tabulku LUT, kterou lze nakonfigurovat tak, aby splňovala jakoukoli logickou funkci se 4 vstupy. Pro lepší podporu širokých datových cest, které se používají v některých aplikacích, jsou k dispozici FPGA se 6, 7 nebo dokonce 8 vstupy pro vyhledávací tabulku LUT. Výstup z vyhledávací tabulky LUT je vyveden ven z logického bloku (y) a je přiveden k jednomu ze vstupů multiplexoru. Druhý vstup multiplexoru je připojen ke vstupu logického bloku (e). Multiplexor lze nakonfigurovat tak, aby vybral jeden z těchto vstupů.

Výstup z multiplexoru je veden přímo do vstupu registru. Každý registr může být nakonfigurován tak, aby fungoval jako klopný obvod typu „Flip - Flop“ nebo Latch. Typ Flip-Flop je řízený hranou, kdežto typ Latch je řízen úrovní. Použití asynchronní logiky u typu Latch se uvnitř FPGA nedoporučuje). Hodiny (clock) nebo povolení (enable) každého registru lze nakonfigurovat tak, aby byly aktivní při vysoké nebo nízké úrovni. Podobně lze také nakonfigurovat aktivní úroveň pro pin set/reset.

Tyto logické bloky lze považovat za „ostrovy programovatelné logiky“ plovoucí v „moři programovatelného pole“. Primární vstupy do FPGA lze připojit k libovolným vstupům logických bloků a výstupy z logických bloků lze vyvést k primárních výstupů ze zařízení.

Primární vstupy / výstupy (GPIO) jsou nalinkovány do bank (skupinách), kde každou banku lzue nakonfigurovat tak, aby podporovala jiný standard rozhraní jako je LVCMOS, LVDS, LVTTL, HSTL nebo SSTL. Kromě toho lze nakonfigurovat impedanci vstupů nebo rychlost přeběhu (slew rate) výstupů.

Ve struktuře FPGA mohou být přímo bloky SRAM, nazývané bloková RAM (BRAM), fázový závěs (PLL) nebo správce hodin (obrázek 1b). Lze také přidat bloky digitálního zpracování signálu (DSP), které obsahují konfigurovatelné multiplikátory a konfigurovatelný sčítač, který umožňuje provádět vícenásobné operace (MAC) (obrázek 1c).

Další funkcí FPGA je vysokorychlostní blok SERDES, který umožňuje vytvořit gigabitová sériová rozhraní. Je důležité si uvědomit, že ne všechny FPGA mají všechny výše uvedené funkce. Různé FPGA nabízejí různé kombinace funkcí, které jsou zaměřeny na různé trhy a aplikace.

Programovatelnou strukturu v FPGA lze použít k implementaci jakékoli logické funkce nebo souboru požadovaných funkcí až po jádro procesoru nebo dokonce více jader. Pokud jsou tato jádra implementována do programovatelné struktury, označují se jako „měkká jádra“. Některá FPGA obvykle označované jako SoC FPGA obsahují jeden nebo více jader procesorů přímo v křemíku. Tato jádra se označují jako „tvrdá jádra“ (obrázek 1d). Tato jádra mohou zahrnovat výpočetní jednotky s pohyblivou desetinou čárkou (FPU) a mezipaměť L1 / L2.

Periferní rozhraní CAN, I2C, SPI, UART nebo USB mohou být implementovány jako měkká jádra do programovatelné struktury, ale mnoho FPGA je zahrnuje jako tvrdá jádra přímo v křemíku. Komunikace mezi jádry procesoru, funkcemi rozhraní a programovatelnou strukturou se obvykle realizuje pomocí vysokorychlostních sběrnic AMBA nebo AXI.

První FPGA, které Xilinx uvedl na trh v roce 1985 obsahovalo pouze 8 x 8 programovatelných logických bloků (žádné bloky RAM, bloky DSP atd.). Pro srovnání, dnešní špičkové FPGA mohou obsahovat stovky tisíc logických bloků, tisíce DSP bloků a megabity RAM. Celkově mohou obsahovat miliardy tranzistorů rovnajících se desítkám milionů reprezentujících příslušná logická hradla (např. 2-vstupních NAND hradel).

Konfigurační technologie

Určení funkce logických bloků a směru propojení se provádí pomocí konfiguračních buněk. Mohou být zobrazeny jako přepínače 0/1 (vypnuto / zapnuto). Tyto buňky se také používají ke konfiguraci rozhraní GPIO, vstupní impedance, výstupní rychlosti přeběhu atd. V závislosti na FPGA se používají tři technologie pro konfigurační buňky.

- Antifuse: Tyto konfigurační buňky jsou jednorázově programovatelné (OTP). To znamená, že jakmile je zařízení naprogramováno, již není možno jeho vnitřní strukturu měnit. Takové zařízení se používají pro bezpečnostní aplikace. Vzhledem k tomu, že se prodávají v malém množství, je jejich cena vysoká.

- Flash: Stejně jako v případě Antifuse jsou buňky založené na technologii Flash energeticky nezávislé. Na rozdíl od technologie Antifuse lze flash buňky podle potřeby přeprogramovat. Flash konfigurační buňky jsou odolné vůči záření, díky čemuž jsou vhodná pro kosmické aplikace (i když je nutno upravit horní metalizovanou vrstvu a pouzdro).

- SRAM: V tomto případě jsou konfigurační data uložena v externí paměti, odkud jsou načtena při každém zapnutí FPGA (nebo podle doporučení v případě dynamických konfiguračních scénářů).

Výhody FPGA, jejichž konfigurační buňky jsou založeny na Antifuse nebo Flash, spočívají v tom, že jsou „okamžité“ a spotřebovávají jen málo energie. Jednou z nevýhod je to, že vyžadují kroky navíc nad základním CMOS procesem, který je použit ve zbytku čipu. Výhodou FPGA na bázi SRAM, je to, že jsou vyrobeny pomocí stejného procesu CMOS jako zbytek čipu. Navíc nabízí vyšší výkon, protože jsou obvykle o jednu nebo dvě generace před technologií Antifuse a Flash. Hlavní nevýhoda je v tom, že SRAM konfigurační buňky spotřebovávají více energie a jsou citlivé na single event upsets (SEU) způsobené zářením. Kvůli této citlivosti na záření nebyly FPGA s technologií SRAM vhodné pro vesmírné aplikace. V poslední době byly použity speciální technologie, které tuto nevýhodu eliminovaly a FPGA na bázi SRAM se nachází v systému Mars Curiosity Rover vedle FPGA na bázi Flash technologie.

FPGA nabízí flexibilitu

FPGA se používají pro mnoho různých aplikací. Jsou zvláště užitečné pro implementaci inteligentních rozhraní, řízení motoru, vysoce výkonné výpočty (HPC), zpracování obrazu a videa, strojové vidění, umělou inteligenci (AI), strojové učení (ML), hluboké učení (DL), radary, tvarování paprsků (beamforming), základnové stanice pro komunikace a další.

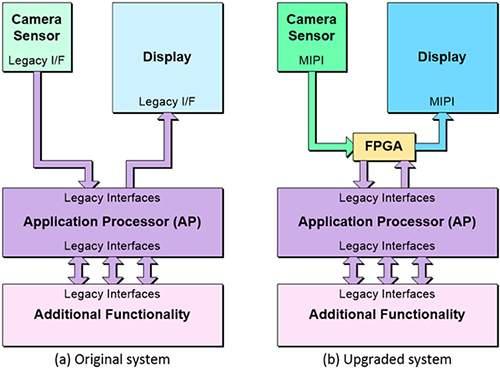

Jedním jednoduchým příkladem použití je vytvoření inteligentního rozhraní mezi zařízeními, která používají různé komunikační protokoly. Například nový systém, který obsahuje aplikační procesor a je připojený ke kameře a displeji pomocí staršího rozhraní (obrázek 3a).

Obrázek 3: FPGA lze použít jako inteligentní rozhraní mezi zařízeními, která používají různé standardy nebo komunikační protokoly. Tím se prodlouží životnost existujících systémů založených na starších protokolech. (Zdroj obrázku: Max Maxfield)

Představme si situaci, kdy je nutné v systému upgradovat kamerový senzor a zobrazovací jednotku .na něco modernějšího, levnějšího a s nižší spotřebou energie. Jediným problémem je, že jeden nebo oba z těchto nových periferií používají nový typ rozhraní (například mobilní průmyslové rozhraní MIPI), který není podporován původním aplikačním procesorem (AP). V tomto případě je jasným řešením použití FPGA, které díky měkkému jádru MIPI IP poskytne rychlou, levnou a bezrizikovou cestu upgradu (obrázek 3b).

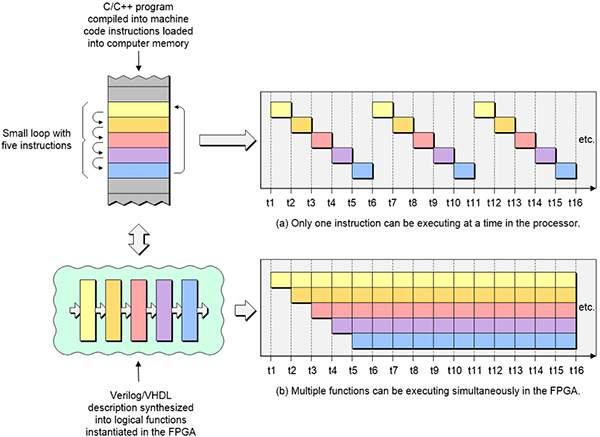

Jako další příklad je použití FPGA pro výpočetně náročný úkol jako je zpracování signálu v radarovém systému. Běžné procesory s von Neumannovými nebo Harvardovými architekturami se dobře hodí k určitým úkolům, ale jsou méně vhodné pro ty, které vyžadují opakování stejného sledu operací. Je tomu tak proto, že jedno jádro procesoru, které zpracovává jediné vlákno, může provádět v jeden okamžik pouze jednu instrukci (obrázek 4a).

Obrázek 4: Na rozdíl od mikroprocesorů, ve kterých může být současně prováděna pouze jediná instrukce (sekvenčně), může být v FPGA spuštěno více funkčních bloků současně; FPGA také mohou implementovat vhodné algoritmy masivně paralelním způsobem. (Zdroj obrázku: Max Maxfield)

V FPGA lze provádět současně více funkcí. To umožňuje shlukovat řadu operací, a to zase způsobí mnohem větší propustnost. Než aby se provedla stejná operace 1 000krát na 1 000 párech datových hodnot v procesoru, můžeme stejné výpočty provést masivně paralelním způsobem v jediném hodinovém cyklu v FPGA tím, že v programovatelném programu vytvoříte 1 000 sčítání (obrázek 4b).

Kdo vyrábí FPGA?

Dvěma hlavními výrobci opravdu high-end zařízení s nejvyšší kapacitou a výkonem je Intel (který získal Alteru) a Xilinx . Intel a Xilinx pokrývají celý rozsah od low-end FPGA po high-end FPGA SoC. Dalším dodavatelem, který se zaměřuje téměř výhradně na FPGA je Lattice Semiconductor, který cílí na malé a středně velké aplikace. V neposlední řadě je tu Microchip Technology (prostřednictvím svých akvizic Actel, Atmel a Microsemi), který nyní nabízí rodiny malých a středních FPGA a low-end členy skupiny SoC FPGA.

Jak navrhnout design s FPGA?

Tradiční způsob, jak vytvořit FPGA je používat speciální jazyk jako je Verilog nebo VHDL. Programy vytvořené těmito jazyky se nejprve simulují za účelem ověření, že vykonávají vše podle potřeby. Pak jsou předávány do nástroje pro syntézu, který generuje konfigurační soubor ke konfiguraci (naprogramování) FPGA.

Každý prodejce FPGA buď má vlastní interně vyvinuté nástroje od specializovaného dodavatele. Aby se FPGA staly přístupnější, někteří FPGA prodejci nyní nabízí tzv. hiht-leel synthesis (HLS) nástroje na vysoké úrovni. Tyto nástroje dokáží interpretovat algoritmický popis požadovaného chování v jazyce C, C ++, nebo OpenCL a generovat vstup pro konfiguraci FPGA.

Pro ty, kteří chtějí začít, existuje mnoho vývojových desek, z nichž každá nabízí různé možnosti a funkce. Například DFR0600 vývojový kit od DFRobot, který je postaven na Zynq-7000 SoC FPGA od firmy Xilinx. Kit DE10 Nano z Terasic Inc s Cyclone V SoC FPGA od společnosti Intel. A ICE40HX1K-stick-EVN vývojovou desku pro iCE40 FPGA od Lattice Semiconductor. Pro rychlé použití FPGA lze využít jednu z karet Alveo PCIe od firmy Xilinx, která dokáže běžet na X86.

Závěr

Optimální konstrukční řešení pro výkonné systémy jsou často poskytovány pomocí FPGA, kombinací procesoru a FPGA nebo FPGA, které se mají integrovány jádra procesoru přímo v křemíku. FPGA se rychle vyvíjí a jejich velké výhody jsou: flexibilita, rychlost a vysoký výkon.

Článek vyšel v originále " Fundamentals of FPGAs: What Are FPGAs and Why Are They Needed?" na webu DigiKey.com, autorem je Clive "Max" Maxfield.