Tento článek popisuje, jak rozšířit Flash paměť mikroprocesoru přidáním externího sériového paměťového čipu od společnosti Adesto Technologies. Tato paměť podporuje rozhraní SPI eXecute in Place (XiP). Dozvíme se, jak je XiP Flash paměť namapována přímo do paměťového prostoru mikroprocesoru Microchip Technology.

Důvody pro rozšíření externí paměti

Již při výběru mikroprocesoru by se mělo počítat s možností rozšíření paměti. Proto bychom měli volit mikroprocesory, které existují ve více variantách, jsou pinově kompatibilní a mají různé velikosti paměti. Pokud se během vývoje kód rozšíří tak, že přesáhne Flash paměť v mikroprocesoru, lze ji během vývoje snadno nahradit mikroprocesorem, který je pinově kompatibilní a má větší paměť. Aplikace však může vyžadovat více paměti, než je k dispozici v celé rodině kompatibilních mikroprocesorů. V tomto případě musíme použít externí Flash paměť. To nastává stále častěji a může k tomu dojít z několika důvodů:

- Rozsah celého systému se zvětší mimo počáteční koncepci. To může být způsobeno změnami na poslední chvíli, tzv. feature creep nebo nepřesným odhadem velikosti paměti. Možnosti jsou buď upgrade na pinově kompatibilní mikroprocesor, který má více paměti nebo přidat externí paměť. To může zpozdit projekt.

- Budoucí aktualizace firmwaru může vyžadovat více paměti, než je k dispozici v mikroprocesoru, který je osazen na desce. V této situaci jsou možnosti opravy omezené. Buď vyměnit mikroprocesor přímo u zákazníka za ten, který obsahuje více paměti nebo zrušit upgrade.

- Pokud se jedná o vývoj celého ekosystému, může nastat situace, kdy nový produkt bude potřebovat více Flash programové paměti, než je k dispozici v celé rodině kompatibilních mikroprocesorů. Možnosti máme takové, že se provede redesign celého systému pomocí nové rodiny mikroprocesorů nebo se přidá externí paměti.

Je důležité již na začátku vývoje provést podrobnou analýzu paměťových potřeb současných a budoucích produktů. Na základě analýzy vyhodnotit celou situaci a připravit si místo na desce pro použití externí paměti. Je lepší si vytvořit rezervu, jelikož systémy jsou více a více komplikované a firmware zabírá čím dál více paměti.

Rozšíření paměti se provádělo použitím paralelního rozhraní s adresovými a datovými linkami. Nejefektivnější využití paralelní Flash paměti, která neomezuje rychlost, může používat až 16 bitové adresy, 16 bitová data a čtyři nebo více řídicích signálů. To vyžaduje 36 nebo více pinů mikroprocesoru. Externí paralelní sběrnice zabírá potřebné místo na desce a vysokorychlostní adresní a datová sběrnice zvyšuje elektromagnetické rušení (EMI).

Spuštění kódu v paměti SPI XiP

Efektivnější možností je použít externí Flash paměť, která podporuje rozhraní SPI XiP. Rozhraní SPI XiP používá pouze šest pinů pro připojení k hostitelskému mikroprocesoru. K externí paměti není přímo přistupováno, ale paměť je mapována v programové paměti mikroprocesoru, což je rozdíl od rozhraní SPI.

Dobrým příkladem externí sériové Flash paměti s rozhraním SPI XiP je AT25SL321-UUE-T od společnosti Adesto Technologies (Obrázek 1). Jedná se o 32 Mbit flash paměť, která podporuje režimy single, dual nebo quad SPI. SPI hodiny běží na frekvenci 104 MHz, které v režimu dual SPI poskytují ekvivalentní hodinovou frekvenci 266 MHz a v režimu quad SPI ekvivalentní hodinovou frekvenci 532 MHz.

Obrázek 1: Adesto AT25SL321 je 32 Mbit Flash paměť, která podporuje režimy SPI sinle, dual a quad. Poskytuje 32 MB paměti Flash v 8-pinovém SOIC, DFN8 nebo TSSOP8 pouzdru. (Zdroj obrázku: Adesto Technologies)

Kromě 32 Mbits Flash pamětí má také stavové registry pro konfiguraci zařízení. Čtením ze stavových registrů může firmware zjistit, zda paměť provádí zápis nebo mazání. Zápisem do stavových registrů můžeme zajistit ochranu bloků paměti proti zápisu.

Adesto AT25SL321 má také 4 Kbits jednorázové programovatelné paměti (OTP), kterou lze použít k ukládání informací ke zvýšení bezpečnosti. Jako je například jedinečné sériové číslo. Dodává se v 8-pinovém pouzdru SOIC, DFN8 nebo TSSOP8.

Stejně jako všechna sériová paměťová zařízení, která podporují SPI XiP se Adesto AT25SL321 konfiguruje pomocí instrukční sady. Instrukční sada se skládá z 38 příkazů, které jsou používány hostitelským mikroprocesorem pro ovládání sériové paměti. Periferie SPI XiP na mikroprocesoru obsahuje programovatelný stavový stroj, který je inicializován přímo v mikroprocesoru instrukční sadou cílové sériové Flash paměti.

Pokud například firmware mikroprocesoru čte data z oblasti mapované paměti, SPI XiP, který je konfigurován instrukční sadou Adesto, odešle do sériové paměti kód instrukce Read Data následovaný 24bitovou adresou. Sériová paměť Adesto pak odešle obsah paměti do mikroprocesoru najednou. Ve firmware se vše projeví jako normální čtení z paměti.

Kromě SPI hodin má Adesto AT25SL321 dva další piny pro lepší funkčnost systému. WP\ je aktivní ochrana proti zápisu, která zabraňuje zápisu do stavového registru. Mikroprocesor může tento pin použít, aby zabránil neautorizovaným změnám. HOLD\ slouží k pozastavení probíhajícího přenosu dat. To může být užitečné ve chvíli, kdy mikroprocesor přijme přerušení s vyšší prioritou, a tak musí pozastavit přenos dat dokud se neobslouží proces s vyšší prioritou.

Zařízení Adesto AT25SL321 32 Mbit Flash podporuje čtyři režimy provozu:

- Standardní operace SPI: Paměť Flash je přístupná jako standardní SPI paměťové zařízení s SPI hodinami (SCLK), active chip select (CS\), sériovými vstupy (SI) a sériovými výstupy (SO). Jsou podporovány standardní režimy sběrnice SPI 0 a 3.

- Duální SPI operace: Poskytuje dvojnásobek datové rychlosti pomocí obousměrných datových pinů SI a SO, označené jako IO0 a IO1.

- Quad SPI operace: Poskytuje čtyřnásobek datové rychlosti standardní SPI operace. Kromě IO0 a IO1 se WP\ a HOLD\ používají jako obousměrné datové piny IO2 a IO3, jelikož v režimu quad SPI se WP\ a HOLD\ nepoužívá.

- Operace QPI: Tento režim se používá pouze pro provoz SPI XiP. Zatímco režimy SPI standard, dual a quad podporují odesílání příkazů do paměti SPI pouze pomocí pinů IO0, operace QPI podporuje odesílání příkazů pomocí čtyř IO [0: 3] pinů, což výrazně zlepšuje výkon SPI XiP.

Pokud nestačí dostatek 32 Mbits paměti, Adesto nabízí také 64 Mbit AT25QL641-UUE-T. Obě paměti jsou pinově kompatibilní. Kromě toho, že má více paměti, AT25QL641 je standardně nastaven na QPI. Tím se zkracuje doba nastavení zařízení ve vysoce výkonných systémech. Obě paměti mají spotřebu během čtení z paměti pouze 5 mA. Pracují s napětím od 1,7 do 2,0 V a jsou schopny spolupracovat s mikroprocesory se stejnou napěťovou hladinou a s rozhraním SPI XiP.

Jako hostitelský mikroprocesor lze použít AT25QL641-UUE-T od Microchip Technology. Jádrem je Arm Cortex-M4F s frekvencí 120 MHz. Celou řadu procesorů naleznete pod názvem ATSAMD51. AT25QL641-UUE-T má 1 MB Flash a 256 Kbytes RAM paměť. Má celou řadu periferií včetně analogově-digitálního převodníku (ADC), digitálně-analogového převodníku (DAC), USB portu a I2S. Má také veřejný klíč šifrování a skutečný generátor náhodných čísel (TRNG) pro bezpečnostní funkce.

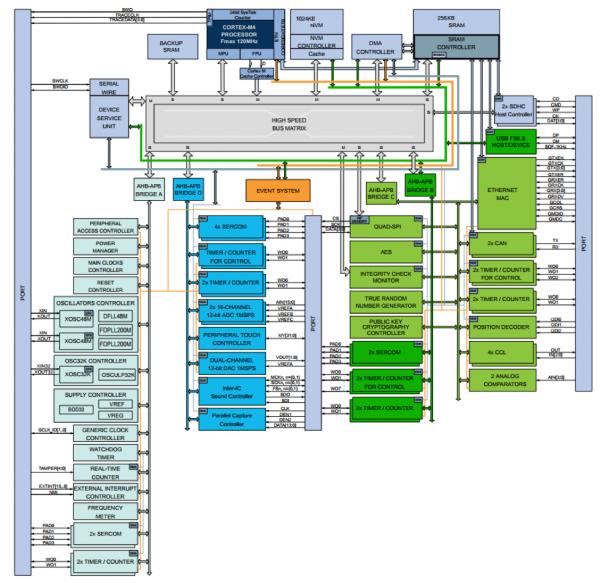

Obrázek 2: Microchip ATSAMD51J20A má sadu periferií, včetně sériového rozhraní SPI XiP, ADC, DAC a podpory šifrování dat. (Zdroj obrázku: Microchip technology)

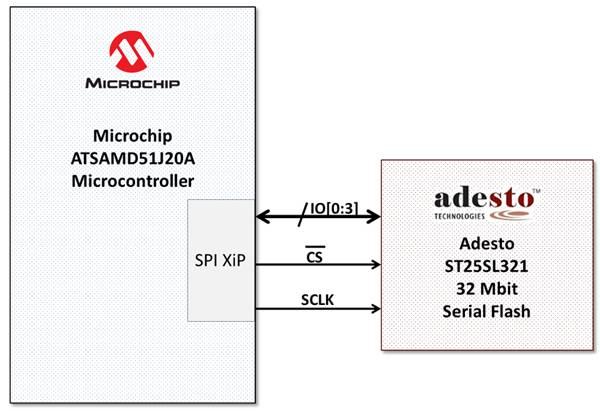

Pro připojení k externí paměti lze použít ATSAMD51J20A QSPI, který podporuje SPI XiP. To umožňuje běh kódu přímo z Flash paměti Adesto. ATSAMD51J20A mapuje Adesto Flash do Arm’s Advanced High-Performance Bus (AHB) paměťového místa. Pro ochranu dat v sériové paměti ATSAMD51J20A SIP XiP podporuje šifrování dat zapisovaných do externí paměti a dešifrování dat načtených z externí paměti. To může zabránit neoprávněnému kopírování firmwaru.

Obrázek 3: Microchip ATSAMD51J20A 32-bitový mikroprocesor má periférii QSPI, která podporuje SPI XiP. Díky tomu lze snadno připojit sériovou paměť Adesto AT25SL321 pouze šesti piny. (Zdroj obrázku: Digi-Key Electronics)

Použití ATSAMD51J20A s paměťovým zařízením Adesto Serial Flash

ATSAMD51J20A SPI XiP má tři registry používané k odesílání příkazů externí sériové XiP Flash paměti.

Vzhledem k tomu, že sériové paměti Flash XiP od různých dodavatelů používají různé instrukční kódy, musí být tyto registry pro daného dodavatele paměti nakonfigurovány následovně:

- Registr instrukčních kódů obsahuje instrukce pro přístup k sériové Flash paměti. Pro paměťové zařízení Adesto Flash pracující v režimu quad SPI obsahuje tento registr instrukci pro výstup rychlého čtení Quad Output 0x6B, pokud firmware provádí kód z oblasti XiP mapované paměti. Tento registr musí být změněn na příslušný kód instrukce, pokud je prováděna operace zápisu, vymazání nebo čtení stavového registru.

- Registr instrukčních adres obsahuje adresu paměti Flash, ke které je přistupováno externě. Pokud je Microchip ATSAMD51J20A SPI XiP nakonfigurován pro režim sériové paměti, tato adresa je automaticky nastavena periferií SPI XiP na adresu prováděnou firmwarem v rozsahu paměti mapované paměti AHB v rozsahu 0x0400 0000 až 0x0500 0000.

- Register instrukčních rámců konfiguruje SPI XiP pro formát specifický pro použitou externí paměť. To zahrnuje výběr délky adresy 24 nebo 32 bitů, což umožňuje dvojitou datovou rychlost (DDR), bez ohledu na to, zda je podporován režim nepřetržitého čtení.

Ostatní rozhraní Microchip SPI XiP lze snadno konfigurovat pomocí ovladačů Microchip SPI. Pokud je aplikační firmware spuštěn z oblasti mapované SPI XiP paměti, periferie SPI XiP v mikroprocesoru nemusí být překonfigurována. Paměť Adesto Flash podporuje také režim čtení pouze s jedním pinem SI s instrukčním kódem 0x03. Pokud je používán pouze režim dual SPI, kód instrukce je 0x3B. Tyto kódy jsou zapsány aplikačním firmwarem do registru instrukčního kódu.

Je považováno za dobré vyprázdnit všechny data z mezipaměti přidružené k paměťovému adresovému prostoru, když je změněn registr instrukčních kódů. Při čtení nebo zápisu do registrů stavu paměti by měla být mezipaměť vyprázdněna a poté zakázána. To by mělo být také provedeno při zápisu. Mezipaměť by měla být znovu aktivována, jakmile se obnoví operace čtení paměti.

Vzhledem k vysokorychlostním přenosům, sériová paměť Flash by měla být umístěna na desce co nejblíže SPI XiP portu. Pokud to není možné, nesmí být žádná dráha delší než 120 mm. Signál hodin by měl být nejméně trojnásobek šířky dráhy ostatních signálů, aby se zabránilo rušení. IO [0: 3] obousměrné datové signály by měly být do 10 mm od sebe, aby nedocházelo ke zkosení hran.

Závěr

Externí sériová paměť Flash může zajistit rychlé spuštění kódu bez složitosti a nadbytečného prostoru, který je nutný při použití paralelní Flash paměti. To umožňuje snadné rozšiřování kódu v průběhu času, stejně jako aktualizaci u zákazníka bez přepracování systémové desky.

Článek vyšel v originále na webu DigiKey.com, autorem je Bill Giovino.